# Chapter 4 Concurrent Constructs for RT Level Descriptions

# Concurrent Constructs for RT Level Descriptions

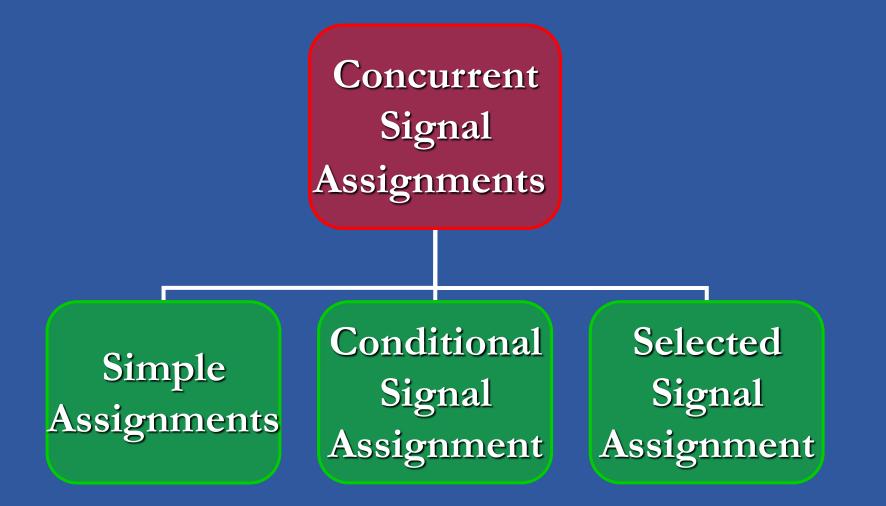

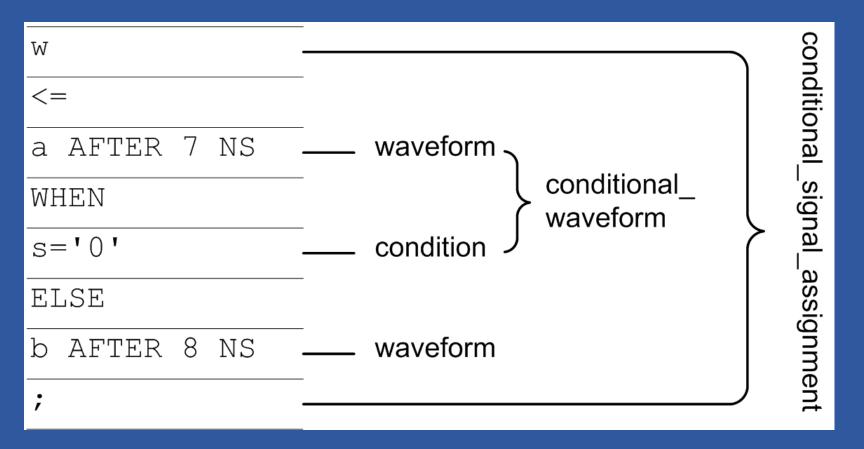

- 4.1 Concurrent Signal Assignments

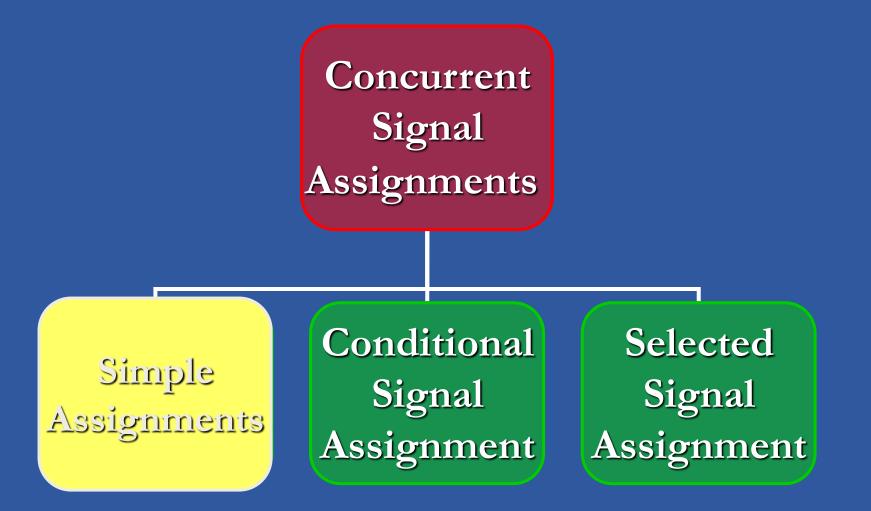

4.1.1 Simple Assignments

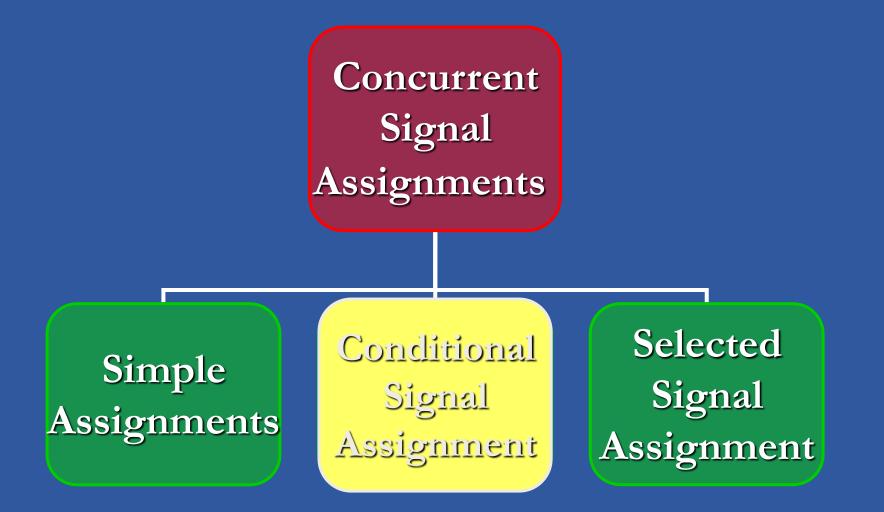

4.1.2 Conditional Signal Assignment

4.1.3 Selected Signal Assignment

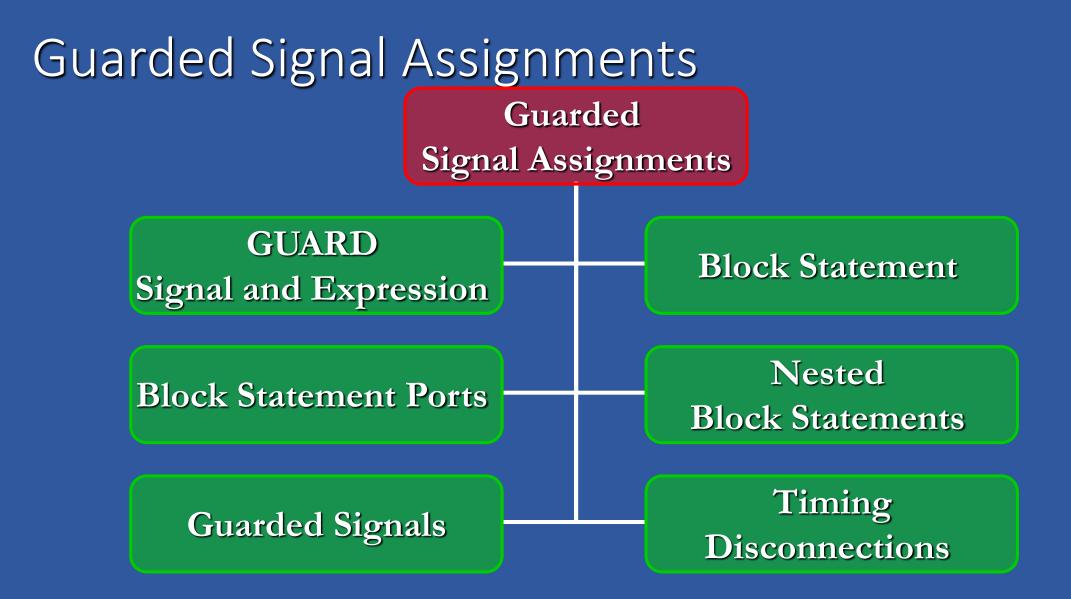

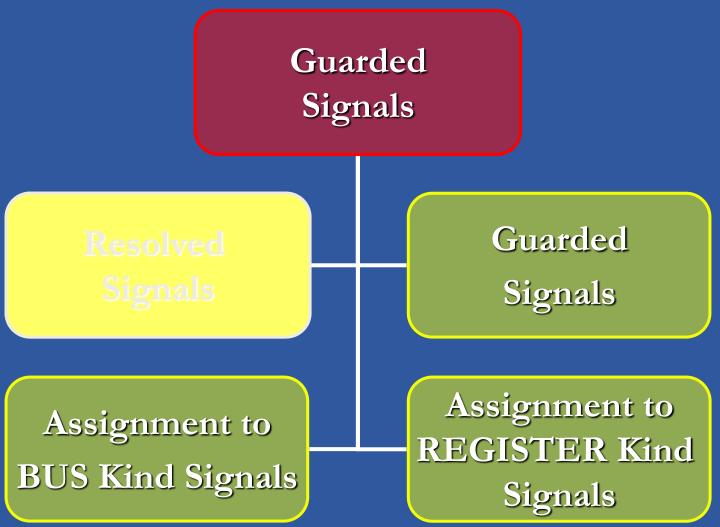

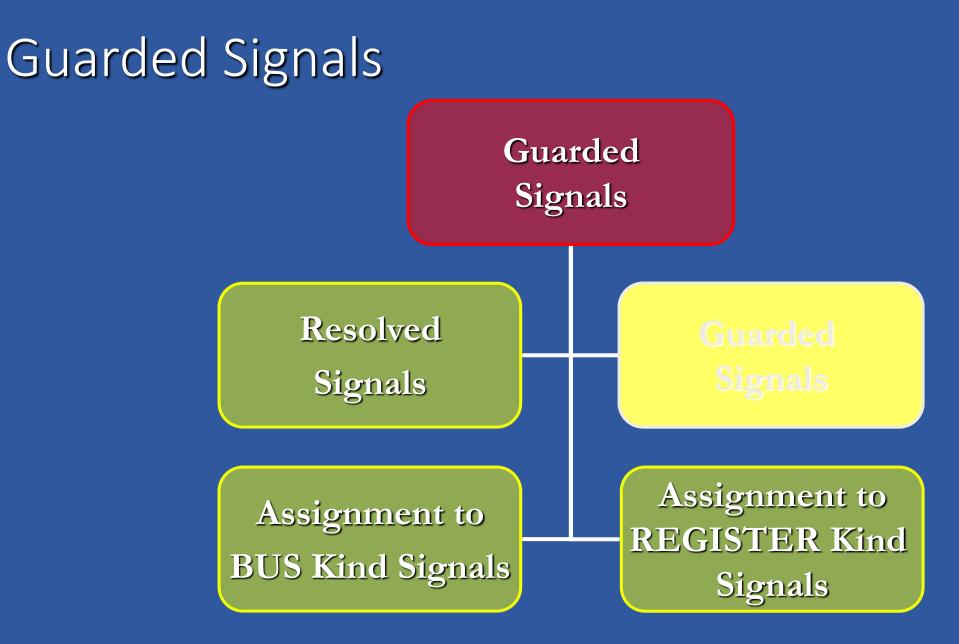

- 4.2 Guarded Signal Assignments

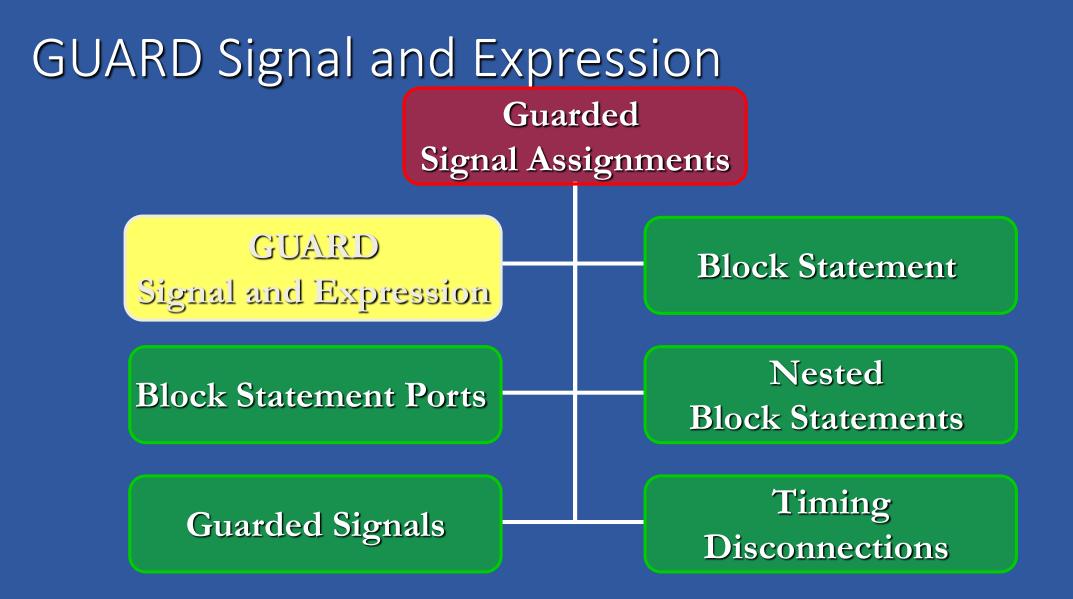

4.2.1 GUARD Signal and Expression

4.2.2 Block Statement

4.2.3 Block Statement Ports

4.2.4 Nested Block Statements

4.2.5 Guarded Signals

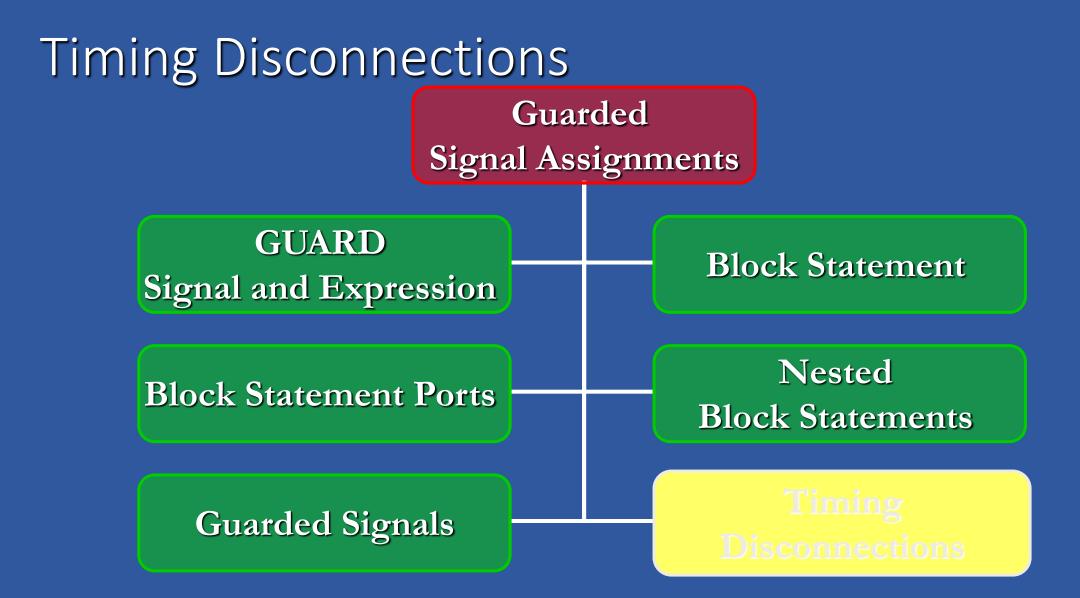

4.2.6 Timing Disconnections

#### 4.3 Summary

#### **Concurrent Signal Assignments**

February 2019

## Simple Assignments

February 2019

#### Simple Assignments

```

ENTITY multiplexer IS

PORT (a, b, s : IN BIT; w : OUT BIT);

END ENTITY;

---

ARCHITECTURE expression OF multiplexer IS

BEGIN

w <= (a AND NOT s) OR (b AND s) AFTER 7 NS;

END ARCHITECTURE expression;</pre>

```

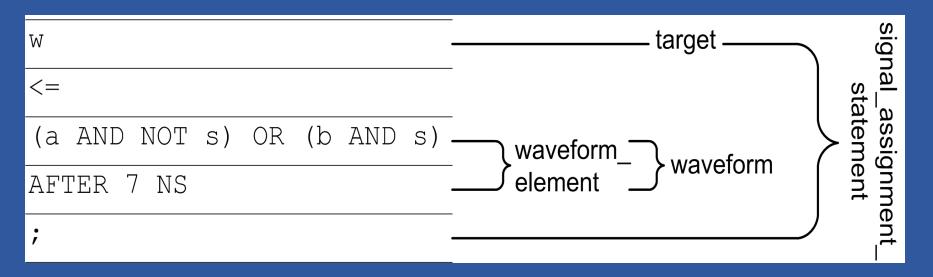

Concurrent Signal Assignment

# Simple Assignments

#### Signal Assignment Syntax Structure

February 2019

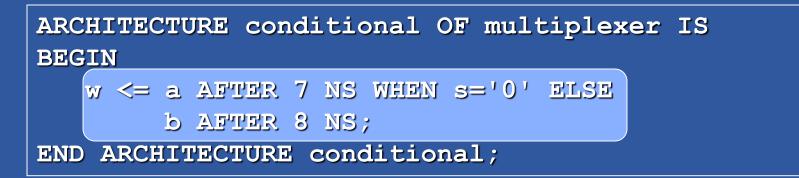

Using Conditional Signal Assignment

Syntax Structure of Conditional Signal Assignments

```

ENTITY flipflop IS

PORT (reset, din, clk : IN BIT; qout : OUT BIT);

END ENTITY;

---

ARCHITECTURE async_reset OF flipflop IS

BEGIN

qout <= '0' WHEN reset = '1' ELSE

din WHEN clk'EVENT AND clk = '1';

END ARCHITECTURE async_reset;</pre>

```

Flip-Flop Using Conditional Signal Assignment

```

ENTITY latch IS

PORT (din, clk : IN BIT; qout : OUT BIT);

END ENTITY;

___

ARCHITECTURE assign OF latch IS

BEGIN

qout <= din WHEN clk = '1';</pre>

END ARCHITECTURE assign;

____

ARCHITECTURE unaffect OF latch IS

BEGIN

qout <= din WHEN clk='1' ELSE UNAFFECTED;

END ARCHITECTURE unaffect;

```

Conditional Signal Assignment Used in Latch Description

February 2019

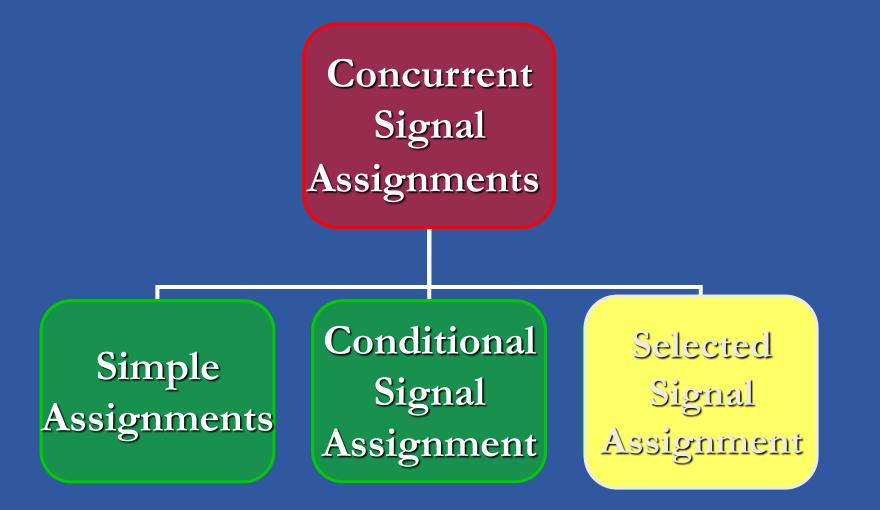

Using a Selected Signal Assignment

Using a Selected Signal Assignment (Continued)

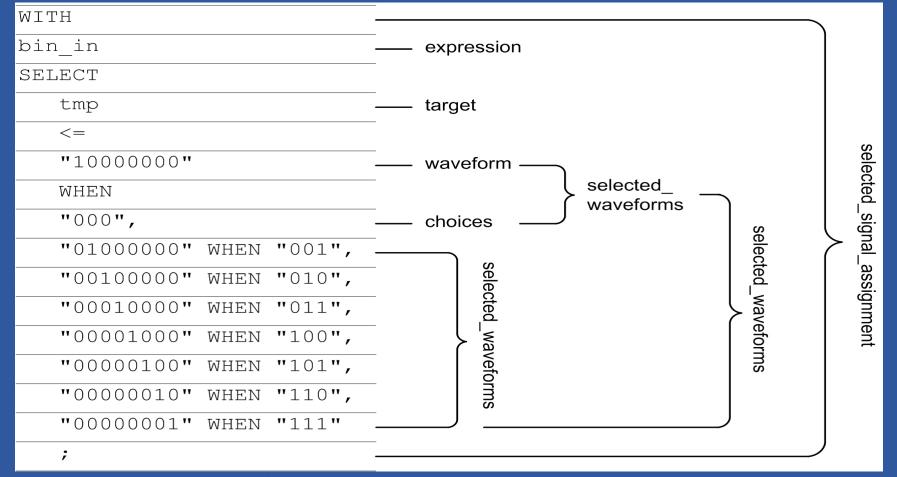

Syntax of Selected Signal Assignment

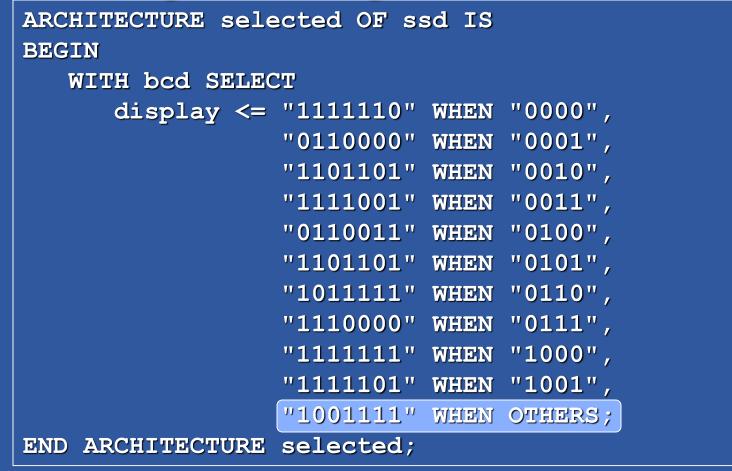

Selected Signal Assignment with Others

Selected Signal Assignment with Others (Continued)

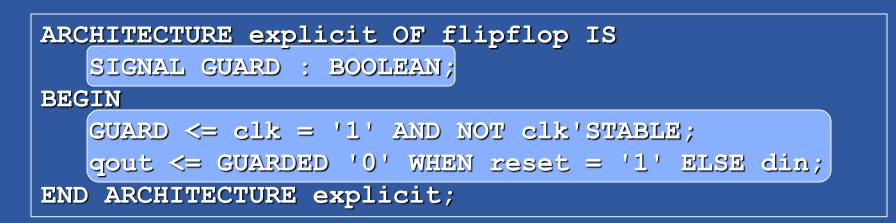

# **GUARD** Signal and Expression

Explicit GUARD Signal

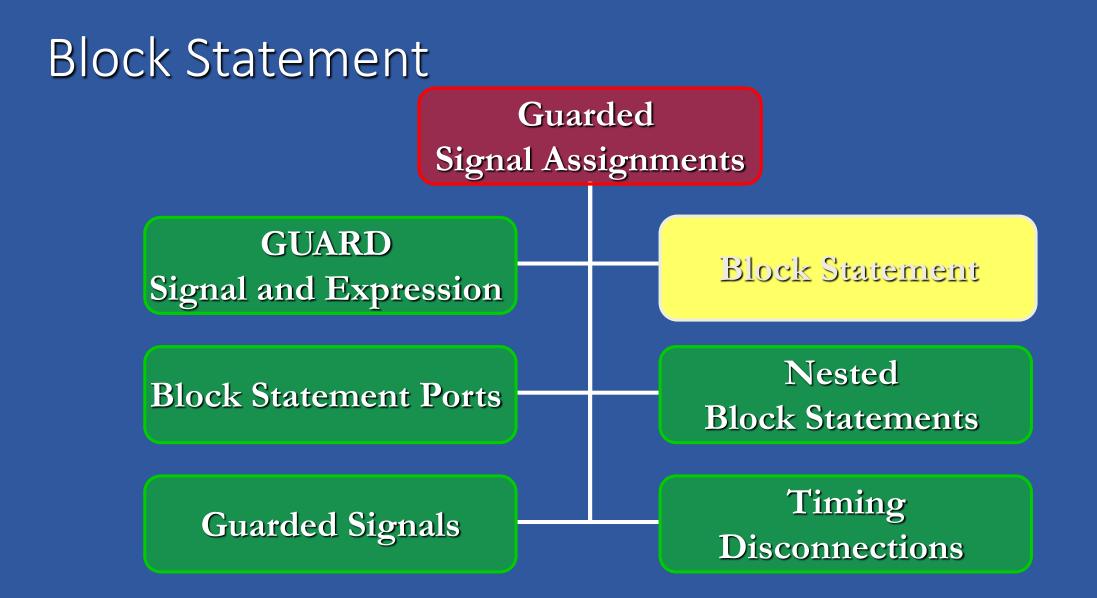

# Block Statement

Block Statement with Guard Expression

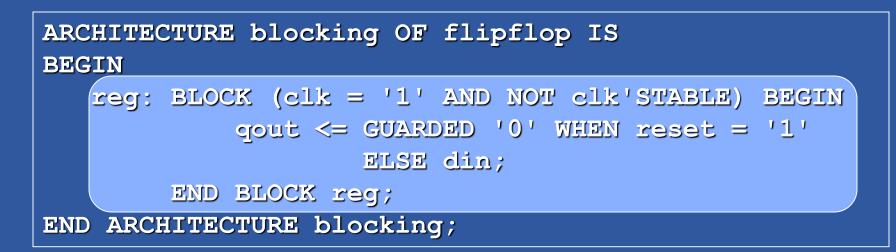

# **Block Statement**

Block Statement Syntax

February 2019

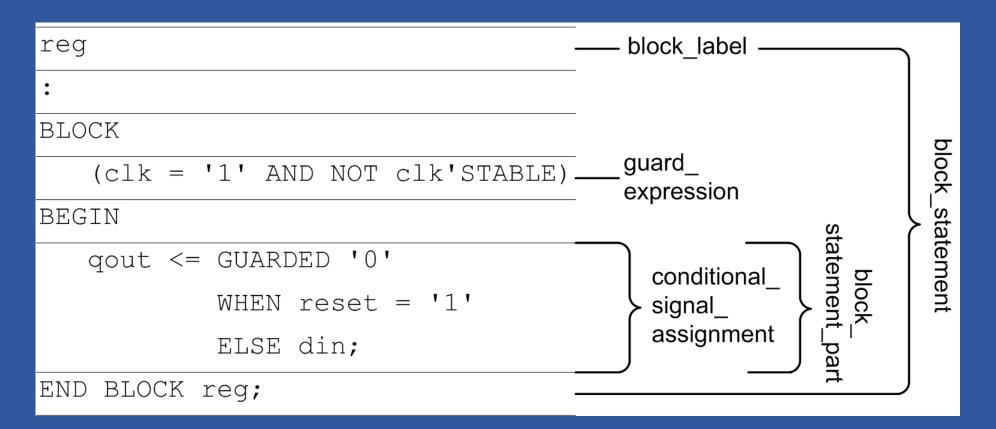

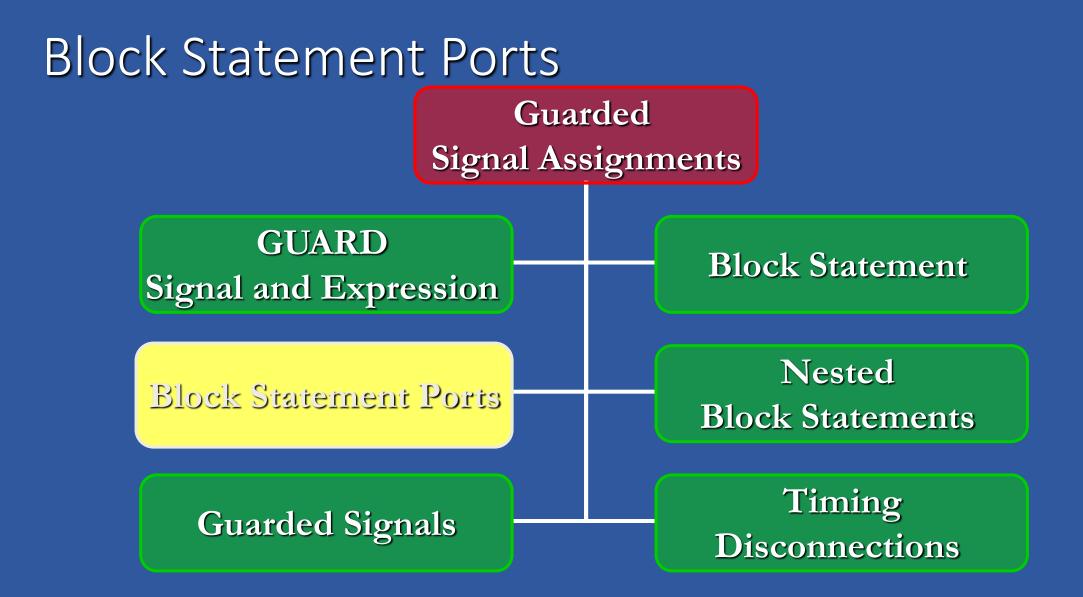

#### **Block Statement Ports**

```

ARCHITECTURE blockport OF flipflop IS

BEGIN

reg: BLOCK (clk = '1' AND NOT clk'STABLE) IS

PORT (r, d, c : IN BIT; q : OUT BIT);

PORT MAP (reset, din, clk, qout);

BEGIN

q <= GUARDED '0' WHEN r = '1' ELSE d;

END BLOCK reg;

END ARCHITECTURE blockport;</pre>

```

```

Block Statement with Ports

```

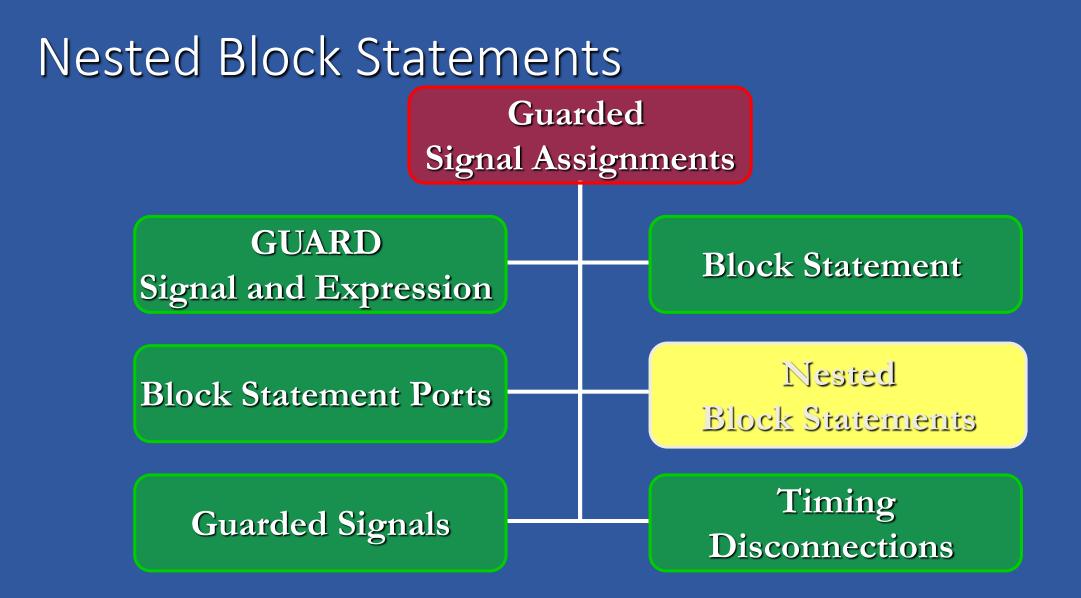

#### Nested Block Statements

```

ENTITY latchflop IS

PORT (din, clk : IN BIT; ql, qf : OUT BIT);

END ENTITY;

___

ARCHITECTURE nested OF latchflop IS

BEGIN

lat: BLOCK (clk = '1') BEGIN

ql <= GUARDED din;</pre>

reg: BLOCK (GUARD AND NOT clk'STABLE) BEGIN

qf <= GUARDED din;</pre>

END BLOCK reg;

END BLOCK lat;

END ARCHITECTURE nested;

```

Nested Block Statements

February 2019

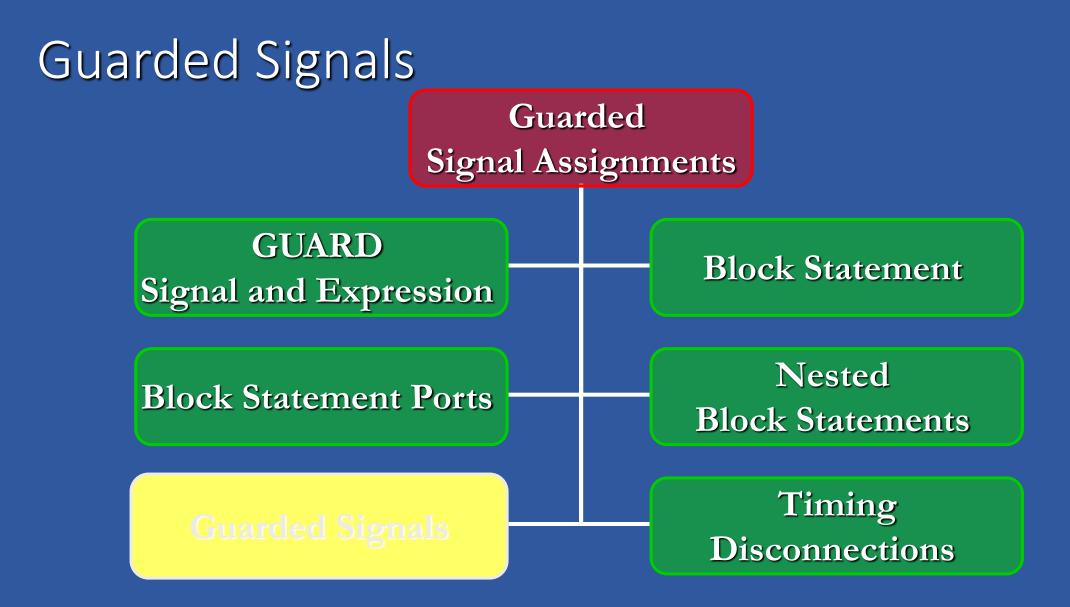

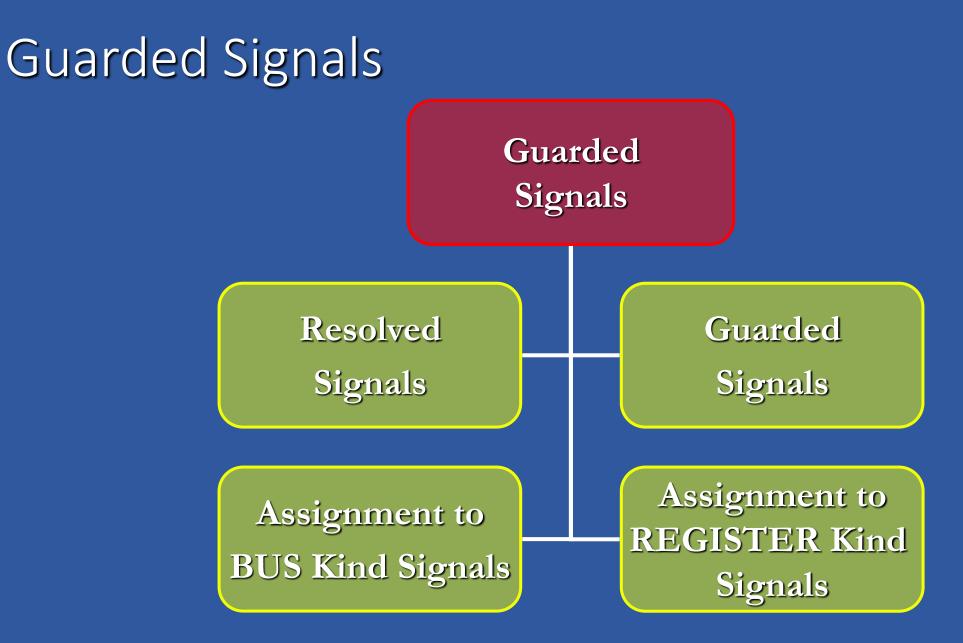

# **Resolved Signals**

# **Resolved Signals**

- Resolved signals can have multiple concurrent drivers

- Associated with a resolved signal is a resolution function that resolves between multiple values assigned to a signal.

- VHDL predefined *std\_logic* resolved type

- Limiting the use of resolved signals to having only one concurrent driver.

- With a resolution function, there is a default resolved value:

- Becomes the value of the resolved signal if the signal has no driver.

- Defined by the resolution function and may be different from the default value of signal

- The default resolved value for std\_logic type is 'Z'.

# Resolved Signals

- A resolved signal can be declared to have a kind.

- Kind specification follows the type mark of the resolved signal in its declaration.

- Kind of a signal can be

- **BUS**

- REGISTER

- If undriven or if a disconnection occurs:

- A guarded signal of BUS kind receives its default resolved value

- An undriven REGISTER kind guarded signal retains its old value (the value before disconnection).

February 2019

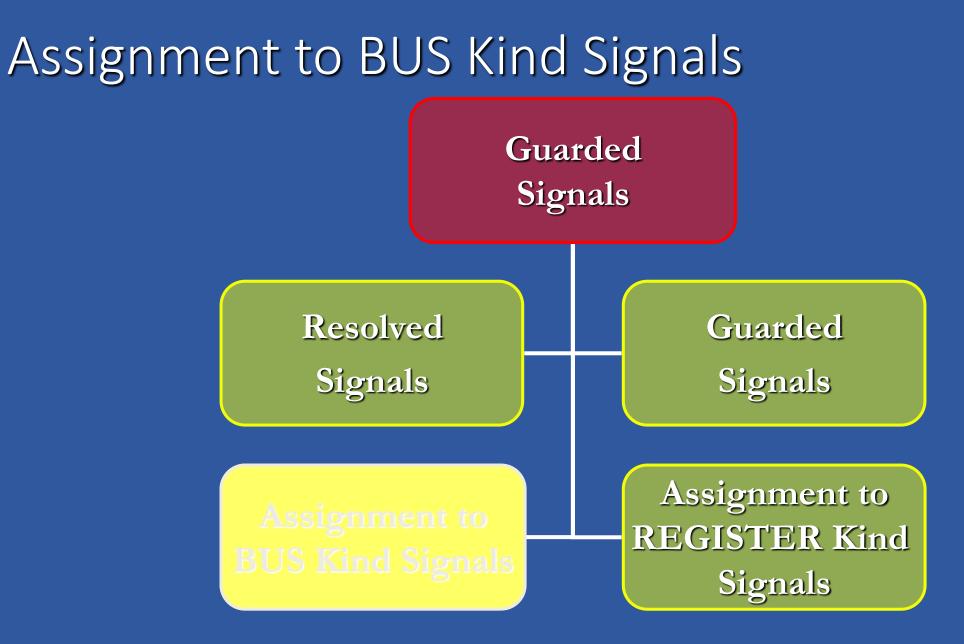

### Assignment to BUS Kind Signals

```

ENTITY multiplexer en IS

PORT (a, b, s, e : IN std_logic; w : OUT std_logic);

END ENTITY;

___

ARCHITECTURE blocking OF multiplexer en IS

SIGNAL t : std logic BUS;

BEGIN

(tri: BLOCK (e='1') BEGIN

t <= GUARDED (a AND NOT s) OR (b AND s);

w \ll t;

END BLOCK tri;

END ARCHITECTURE blocking;

```

BUS Kind Guarded Signal

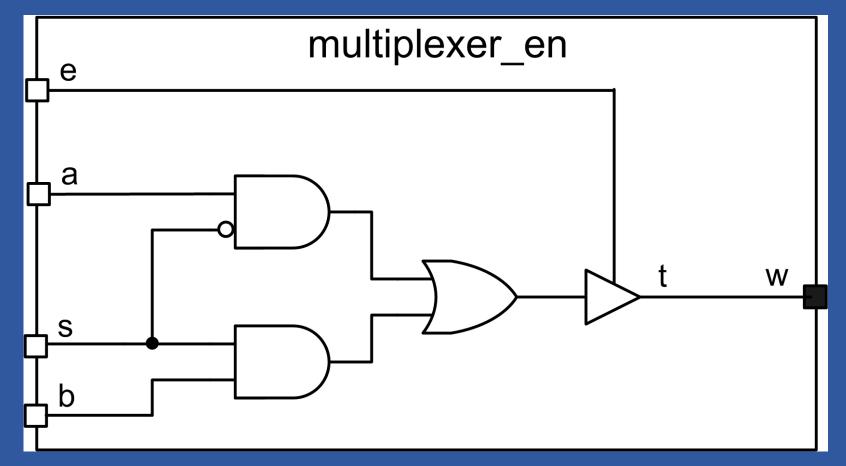

### Assignment to BUS Kind Signals

Hardware Corresponding to *multiplexer\_en*

VHDL: Modular Design and Synthesis of Cores and Systems Copyright Z. Navabi, 2007

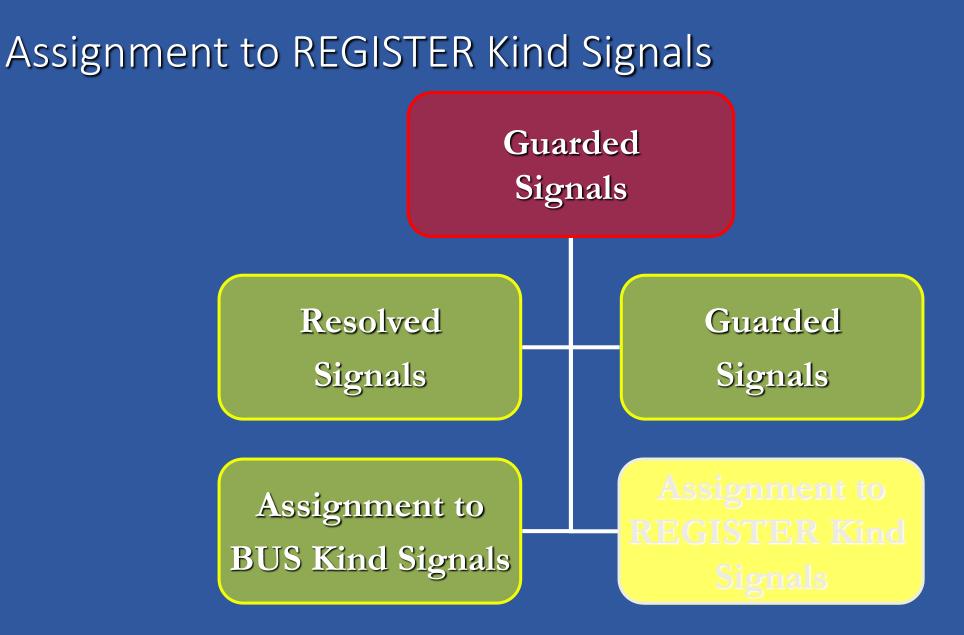

#### Assignment to REGISTER Kind Signals

```

LIBRARY IEEE;

USE IEEE.std logic 1164.ALL;

ENTITY stdflop IS

PORT (reset, din, clk, cen : IN std logic:='0';

qout : OUT std logic);

END ENTITY;

ARCHITECTURE blockport OF stdflop IS BEGIN

reg: BLOCK (clk = '1' AND NOT clk'STABLE)

PORT (r, d, c : IN std_logic; q : OUT std_logic);

PORT MAP (reset, din, clk, qout);

SIGNAL ff : std logic REGISTER;

BEGIN

ff \leq GUARDED '0' WHEN r = '1' ELSE d;

q \leq ff;

END BLOCK reg;

END ARCHITECTURE blockport;

REGISTER Kind Guarded Signal

```

February 2019

VHDL: Modular Design and Synthesis of Cores and Systems Copyright Z. Navabi, 2007

```

ARCHITECTURE timedisconnect OF multiplexer_en IS

SIGNAL t : std_logic BUS;

DISCONNECT t : std_logic AFTER 3.25 NS;

BEGIN

tri: BLOCK (e='1') BEGIN

t <= GUARDED (a AND NOT s) OR (b AND s);

w <= t;

END BLOCK tri;

END ARCHITECTURE timedisconnect;</pre>

```

Multiplexer with Disconnect Time

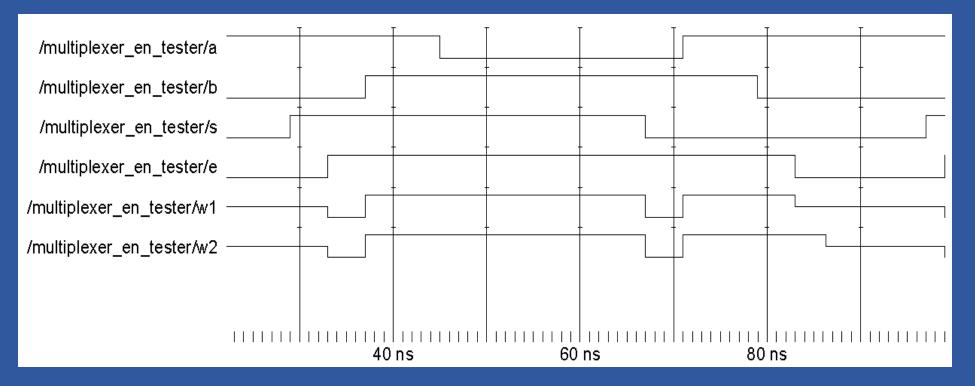

ARCHITECTURE timed OF multiplexer en tester IS SIGNAL a, b, s, e, w1, w2 : std logic; BEGIN UUT1: ENTITY WORK.multiplexer en (blocking) PORT MAP (a, b, s, e, w1);UUT2: ENTITY WORK.multiplexer\_en (timedisconnect) PORT MAP (a, b, s, e, w2);a <= '0', '1' AFTER 20 NS, '0' AFTER 45 NS, '1' AFTER 71 NS;  $b \le 1'$ , '0' AFTER 11 NS, '1' AFTER 37 NS, '0' AFTER 79 NS;  $s \leq 0'$ , '1' AFTER 29 NS, '0' AFTER 67 NS, '1' AFTER 97 NS;  $e \le '0'$ , '1' AFTER 33 NS, '0' AFTER 83 NS, '1' AFTER 99 NS; END ARCHITECTURE timed;

Comparing Disconnection Timing

Comparing Disconnection Times

February 2019

VHDL: Modular Design and Synthesis of Cores and Systems Copyright Z. Navabi, 2007

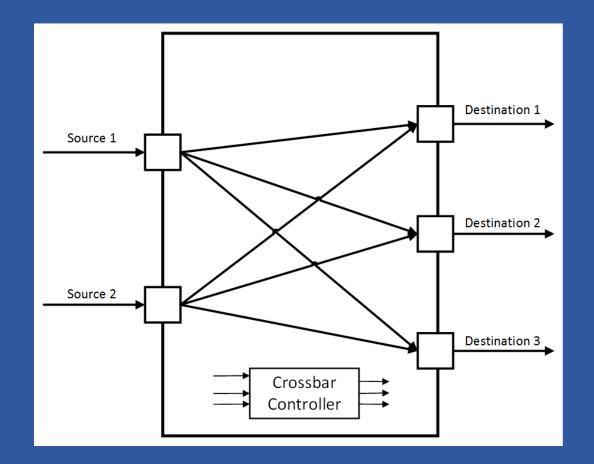

```

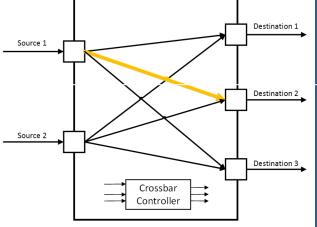

ARCHITECTURE timedisconnect OF crossbar IS

SIGNAL s1d2: std_logic_vector(7 DOWNTO 0) BUS;

DISCONNECT s1d2: std_logic_vector(7 DOWNTO 0) AFTER 3.25 NS;

...

BEGIN

tri: BLOCK (cont_en='1') BEGIN

s1d2 <= GUARDED (s1turn AND s1tod2);

d2 <= s1d2;

...

END BLOCK tri;

END ARCHITECTURE timedisconnect;</pre>

```

• A crossbar connection with Disconnect Time

Copyright Z. Navabi, 2007

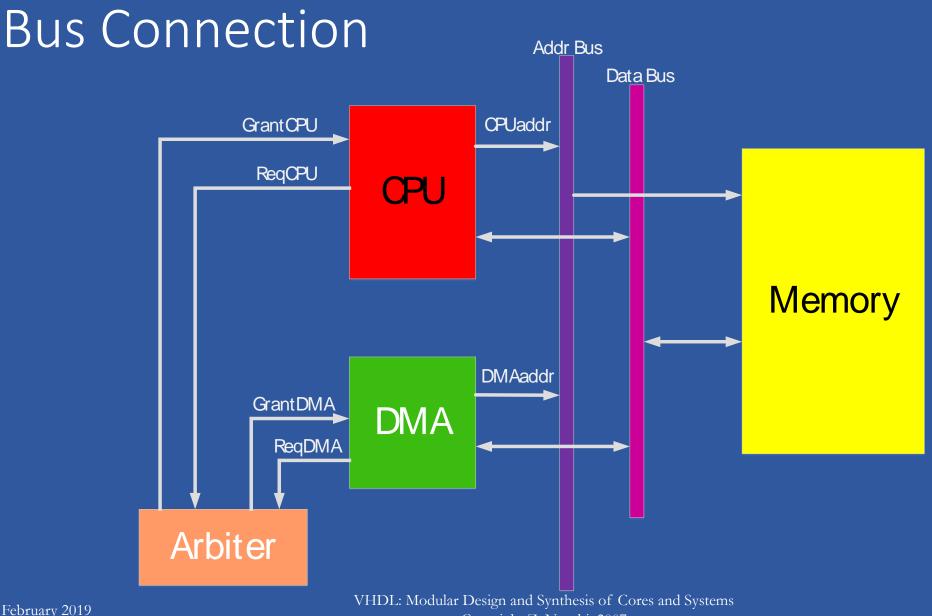

#### **Bus Connection**

```

ARCHITECTURE Blocked OF DMA IS

BEGIN

Block (GrantDMA = '1') BEGIN

addrBus <= GUARDED (DMAaddr);</pre>

END BLOCK;

PROCESS ( ... ) BEGIN

. . .

WAIT FOR GrantDMA;

• • •

END PROCESS;

END ARCHITECTURE Blocked;

```

#### **Bus Connection**

```

ARCHITECTURE Blocked OF CPU IS

BEGIN

addr: BlOCK (GrantCPU = '1')

BEGIN

addrBus <= GUARDED (CPUaddr);</pre>

END BLOCK addr;

• • •

data: BlOCK (GrantCPU = '1' AND W Mem = '1')

BEGIN

dataBus <= GUARDED (CPUdata);</pre>

END BLOCK data;

• • •

END ARCHITECTURE Blocked;

```

### Summary

- The focus of this chapter was on

- Concurrent bodies of VHDL

- Signal assignments

- Block statements

- Guarded signals and guarded assignments

- The constructs discussed here enable description of hardware at a level higher that what was discussed in the previous chapter.

- For more behavioral descriptions VHDL offers sequential statements within concurrent bodies that will be discussed in the next chapter.

## Acknowledgment

Slides developed by: Homa Alemzadeh First revision 2017 by: Bahar Behazin Second revision 2019 by: Saba Yousefzadeh