# Chapter 2 RTL Design with VHDL

# **RTL** Design with VHDL

2.1 Basic Structures of VHDL

2.1.1 Entities and Architectures

2.1.2 Entity-Architecture Outline

2.1.3 Entity Ports

2.1.4 Signals and Variables

2.1.5 Logic Value System

2.1.6 Resolutions

**2.2 Combinational Circuits**

2.2.1 Gate Level Combinational Circuits

2.2.2 Gate Level Synthesis

2.2.3 Descriptions by Use of Equations

2.2.4 Instantiating Other Modules

2.2.5 Synthesis of Assignment Statements

2.2.6 Descriptions with Sequential Flow

2.2.7 Combinational Rules Modular Design and Synthesis of Cores and Systems Copyright Z. Navabi, 2007

# **RTL** Design with VHDL

2.2.8 Bussing2.2.9 Synthesizing Procedural Blocks

#### **2.3 Sequential Circuits**

2.3.1 Basic Memory Elements at the Gate Level

2.3.2 Memory Elements Using Procedural Statements

2.3.3 Flip-flop Synthesis

2.3.4 Registers, Shifters and Counters

2.3.5 Synthesis of Shifters and Counters

2.3.6 State Machine Coding

2.3.7 State Machine Synthesi

2.3.8 Memories

#### 2.4 Writing Testbenches

#### **2.5 Synthesis Issues** February 2019

### **RTL Design with VHDL**

#### 2.6 VHDL Essential Terminologies

2.6.1 Design 2.6.2 Analysis 2.6.3 Library 2.6.4 Standard Packages 2.6.5 Elaboration 2.6.6 Event Driven Simulation 2.6.7 Concurrency **2.6.8 Concurrent Bodies** 2.6.9 Sequentiality 2.6.10 Sequential Bodies 2.6.11 VHDL Objects and Classes 2.6.12 Real Time 2.6.13 Delta Delay 2.6.14 Scheduling 2.6.15 Resolution 2.6.16 Code Formal 2.7 Summary

### **Basic Structures of VHDL**

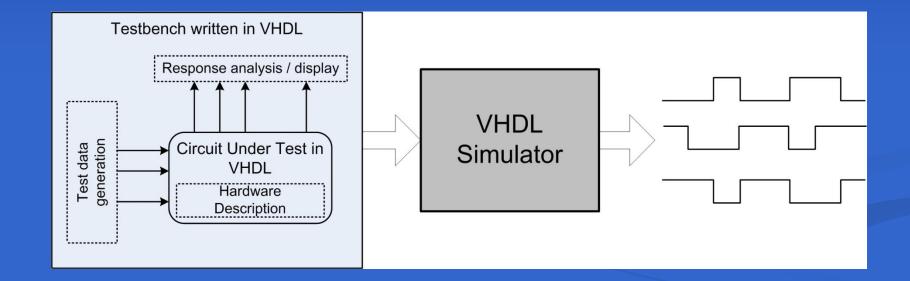

Simulation in VHDL

### **Basic Structures of VHDL**

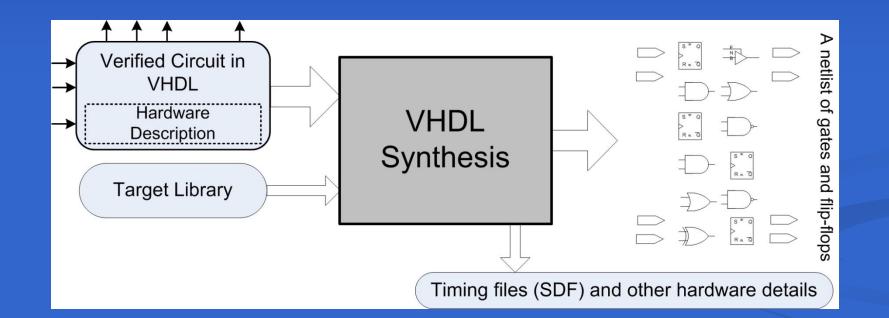

#### Synthesis of a VHDL Design

### **Basic Structures of VHDL**

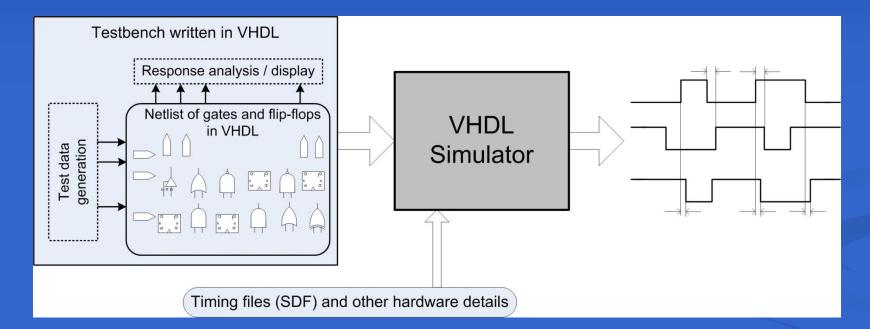

Post-synthesis Simulation in VHDL

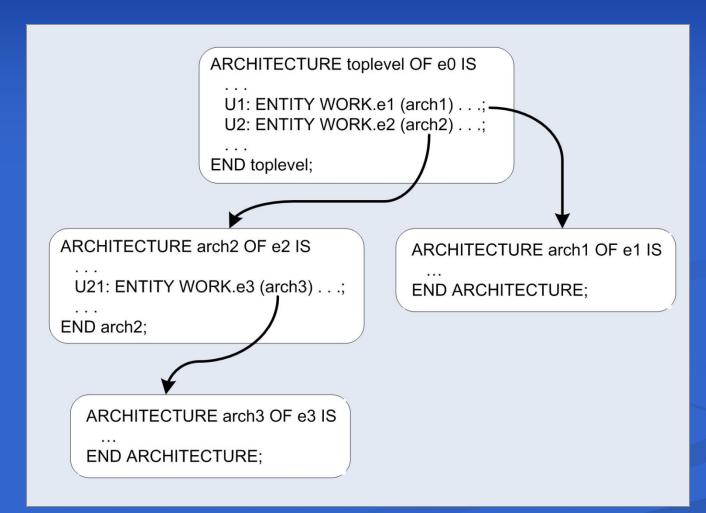

### **Entities and Architectures**

ENTITY entity\_name IS input and output ports END ENTITY entity\_name; ARCHITECTURE identifier OF entity\_name IS declarative part BEGIN statement part END ARCHITECTURE identifier;

### **Entities and Architectures**

### **Entity-Architecture Outline**

```

ENTITY entity1 IS PORT (i1, i2 : IN BIT; w1 : OUT

BIT);

END ENTITY entity1;

ARCHITECTURE simple1 OF entity1 IS

SIGNAL s1 : BIT;

BEGIN

statement1;

statement2;

statement3;

END ARCHITECTURE simple1;

```

### **Entity-Architecture Outline**

```

ENTITY simple IS PORT (i1, i2, i3 : IN BIT; w1, w2 : OUT BIT); END ENTITY simple;

ARCHITECTURE simple 1a OF simple IS

SIGNAL c1 : BIT;

BEGIN

U1: ENTITY WORK.nor2 PORT MAP (i1, i2, c1);

U2: ENTITY WORK.and2 PORT MAP (c1, i3, w1);

U3: ENTITY WORK.xor2 PORT MAP (c1, i3, w2);

END ARCHITECTURE simple 1a;

ARCHITECTURE simple 1b OF simple IS

BEGIN

w1 <= (i1 NOR i2) AND i3;

w2 <= (i1 NOR i2) XOR i3;

END ARCHITECTURE simple 1b;

ARCHITECTURE simple 1c OF simple IS

BEGIN

PROCESS (i1, i2, i3)

VARIABLE c1 : BIT;

BEGIN

c1 := i1 NOR i2;

IF (c1 = 1) THEN w1 <= i3; ELSE w1 <= 0';

IF (c1 = i3 ) THEN w2 <= 0'; ELSE w2 <= 1';

END PROCESS;

END ARCHITECTURE simple 1c;

```

#### Architecture Definition Alternatives

# **Entity Ports**

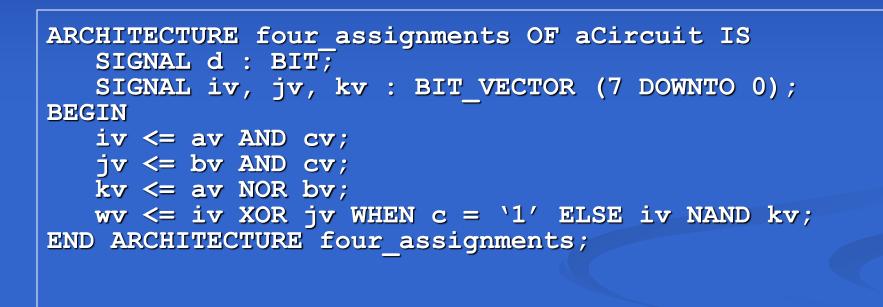

ENTITY aCircuit IS

PORT (a, b : IN BIT;

c : INOUT BIT;

av, bv : IN BIT\_VECTOR (7 DOWNTO 0);

cv : INOUT BIT\_VECTOR (7 DOWNTO 0);

w : OUT BIT;

wv : OUT BIT\_VECTOR (7 DOWNTO 0));

END ENTITY aCircuit;

# Signals and Variables

```

ARCHITECTURE two processes OF aCircuit IS

SIGNAL d : BIT;

SIGNAL dv : BIT VECTOR (7 DOWNTO 0);

BEGIN

p1: PROCESS (a, b, cv)

VARIABLE e : BIT;

VARIABLE ev : BIT_VECTOR (7 DOWNTO 0);

BEGIN

-- Can see all of aCircuit, plus d, dv, e, and ev.

. . .

END PROCESS;

p2: PROCESS (av, bv, c)

VARIABLE f : BIT;

VARIABLE fv : BIT_VECTOR (7 DOWNTO 0);

BEGIN

-- Can see all of aCircuit, plus d, dv, f, and fv.

. . .

END PROCESS;

END ARCHITECTURE two_processes;

```

Signal and Variable Declaration VHDL: Modular Design and

### Data Part

Using Signals

### Data Part

```

ARCHITECTURE mixed_processes_assignments OF aCircuit IS

SIGNAL d : BIT;

SIGNAL dv : BIT_VECTOR (7 DOWNTO 0);

BEGIN

p1: PROCESS (a, b, cv)

VARIABLE e : BIT;

VARIABLE ev : BIT_VECTOR (7 DOWNTO 0);

BEGIN

IF (a = b) THEN ev := av; ELSE ev := bv;

IF (a = '1') THEN wv <= av; ELSE wv <= "1000111";

d <= e;

END PROCESS;

dv <= av XOR bv;

w <= d AND a;

END ARCHITECTURE mixed_processes_assignments;</pre>

```

#### Using Signals and Variables

### Data Part

#### Using Indexing and Slicing

# Logic Value System

| Value | Representing    |

|-------|-----------------|

| 'U'   | Uninitialized   |

| 'X'   | Forcing Unknown |

| '0'   | Forcing 0       |

| '1'   | Forcing 1       |

| 'Z'   | High Impedance  |

| 'W'   | Weak Unknown    |

| 'L'   | Weak 0          |

| 'H'   | Weak 1          |

| 1_1   | Don't care      |

### Resolutions

#### Multiple Assignments to a Resolved Signal

### Resolutions

| U | U | Х | 0 | 1 | Ζ |

|---|---|---|---|---|---|

| U | U | U | U | U | U |

| X | U | X | X | X | X |

| 0 | U | X | 0 | X | 0 |

| 1 | U | X | X | 1 | 1 |

| Z | U | X | 0 | 1 | Ζ |

Partial std\_logic resolved Function

### **Gate Level Combinational Circuits**

| ENTITY AND2 :<br>END ENTITY AN |                                     | .2 : IN std_lo | ogic; ol: OUT std_logic);                                                            |                        |                |            |

|--------------------------------|-------------------------------------|----------------|--------------------------------------------------------------------------------------|------------------------|----------------|------------|

| BEGIN                          | example OF AN<br>AND i2 AFTER 3     |                |                                                                                      |                        |                |            |

| 1                              |                                     | 5 PORT (i1, i2 | 2, i3 : IN std_logic; o1: OUT                                                        | <pre>std_logic);</pre> |                |            |

|                                | ARCHITECTURE<br>BEGIN<br>o1 <= i1 0 | example OF OF  |                                                                                      |                        |                |            |

|                                | END anamala.                        |                | L IS PORT (i1, en : IN std_log                                                       | gic; ol: OUT s         | std_logic);    |            |

|                                |                                     | BEGIN          | example OF BUFIF1 IS<br>AFTER 4 NS WHEN en = $1'$ ELSE                               | 'Z' AFTER 3 1          | NS ;           |            |

|                                |                                     | END example;   | ENTITY BUFIFO IS PORT (i1, en<br>END ENTITY BUFIFO;                                  | n : IN std_lo          | gic; ol: OUT s | td_logic); |

|                                |                                     |                | ARCHITECTURE example OF BUFIN<br>BEGIN<br>ol <= il AFTER 4 NS WHEN e<br>END example; |                        | 'Z' AFTER 3 N  | IS;        |

Basic Primitives Described in VHDL

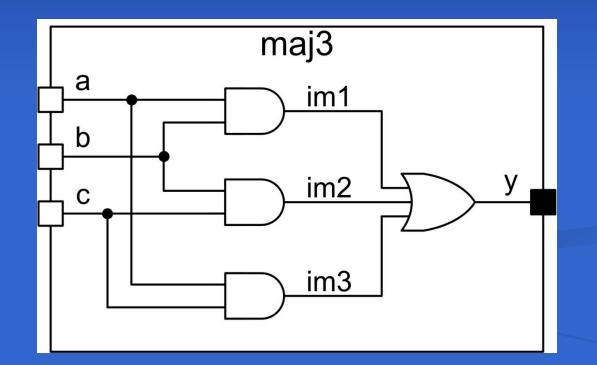

# Majority Example

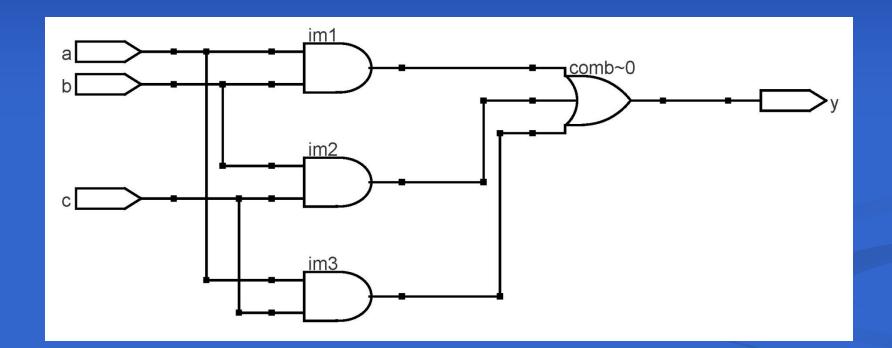

#### A Majority Circuit

# Majority Example

```

LIBRARY IEEE;

USE IEEE.std logic 1164.ALL;

ENTITY maj3 IS

PORT (a, b, c : IN std_logic; y : OUT

std logic);

END maj3;

ARCHITECTURE gate level OF maj3 IS

SIGNAL im1, im2, im3 : std logic;

BEGIN

ANDa: ENTITY WORK.AND2 PORT MAP (a, b, im1);

ANDb: ENTITY WORK.AND2 PORT MAP (b, c, im2);

ANDC: ENTITY WORK.AND2 PORT MAP (a, c, im3);

ORa : ENTITY WORK.OR3 PORT MAP (im1, im2, im3, y);

END ARCHITECTURE gate level;

```

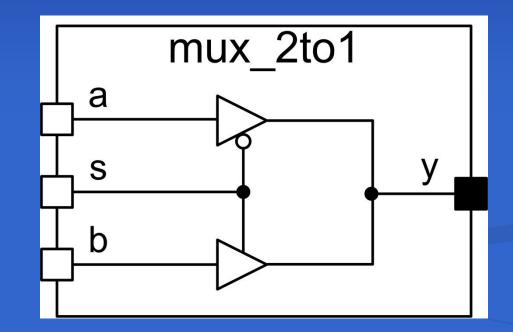

# Multiplexer Example

Multiplexer Using Three-state Gates

# Multiplexer Example

# Gate Level Synthesis

### Gate Level Synthesis

RTL (logical) View of Synthesized maj3

# Descriptions by Use of Equations

| Boolean<br>Operators    | NOT | AND | OR  | NAND | NOR | XOR | XNOR |    |

|-------------------------|-----|-----|-----|------|-----|-----|------|----|

| Comparison<br>Operators | =   | /=  | <   | <=   | ^   | >=  |      |    |

| Arithmetic<br>Operators | +   | -   | ABS | MOD  | REM | *   | /    | ** |

| Concat.<br>Operators    | &   |     |     |      |     |     |      |    |

VHDL Operators

### **XOR** Example

ENTITY xor2 IS

PORT (i1, i2: IN std\_logic; o1: OUT std\_logic);

END ENTITY xor2;

--ARCHITECTURE expression OF xor2 IS

BEGIN

o1 <= i1 XOR i2 AFTER 3 NS;

END ARCHITECTURE expression;</pre>

### Full-Adder Example

```

ENTITY full_adder IS

PORT (a, b, cin : IN std_logic;

sum, cout : OUT std_logic);

END ENTITY full_adder;

--

ARCHITECTURE expression OF full_adder IS

BEGIN

sum <= a XOR b XOR cin AFTER 0.3 NS;

cout <= (a AND b) OR (a AND cin) OR (b AND cin) AFTER 0.2

NS;

END ARCHITECTURE expression;</pre>

```

Assign Statement and Boolean

# **Comparator Example**

Copyright Z. Navabi, 2007

```

ENTITY comp 4bit IS PORT (

in1, in2 : IN std logic vector (3 DOWNTO 0);

: OUT std logic );

eq

END comp 4bit;

ARCHITECTURE functional OF comp_4bit IS

SIGNAL im : std logic vector (3 DOWNTO 0);

FUNCTION nor reduce

(in1: IN std_logic_vector (3 DOWNTO 0))

RETURN std logic

IS

VARIABLE result : std logic ;

BEGIN

result:= NOT (in1(3) OR in1(2) OR in1(1) OR

in1(0)) ;

RETURN result;

END;

BEGIN

im <= in1 XOR in2;</pre>

eq <= nor reduce(im);</pre>

VHDL: Modular Design and

END functional;

Synthesis of Cores and Systems

```

### Multiplexer Example

ENTITY multiplexer IS

PORT (a, b : IN std\_logic\_vector; s : IN

std\_logic;

w : OUT std\_logic\_vector);

END ENTITY;

ARCHITECTURE expression OF multiplexer IS

BEGIN

w <= a WHEN s = '0' ELSE b;

END ARCHITECTURE expression;</pre>

An Unconstrained 2-to-1 Mux using Condition Operator

### **Decoder** Example

```

ENTITY dcd2to4 IS

PORT (sel: IN std_logic_vector (1 DOWNTO 0);

y: OUT std_logic_vector (3 DOWNTO 0) );

END dcd2to4;

ARCHITECTURE structural OF dcd2to4 IS

BEGIN

WITH sel SELECT

y <= "0001" WHEN "00",

"0010" WHEN "01",

"0100" WHEN "10",

"1000" WHEN "11",

"0000" WHEN "11";

"0000" WHEN OTHERS;

END ARCHITECTURE structural;</pre>

```

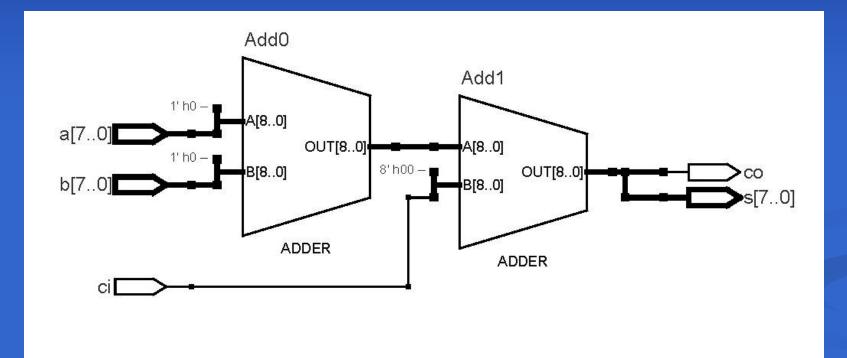

### Adder Example

```

LIBRARY IEEE;

USE IEEE.std logic 1164.ALL;

USE IEEE.std_logic_unsigned.ALL;

ENTITY adder\overline{8} IS \overline{PORT}

a : IN std logic vector (7 DOWNTO 0);

b : IN std logic vector (7 DOWNTO 0);

ci : IN std logic;

s : OUT std logic vector (7 DOWNTO 0);

co : OUT std logic );

END ENTITY adder8;

____

ARCHITECTURE equation OF adder8 IS

SIGNAL mid : std logic vector (8 DOWNTO 0);

BEGIN

mid \le ('0'\&a) + ('0'\&b) + ci;

co <= mid (8);

s \ll mid (7 DOWNTO 0);

END equation;

```

#### Adder with Carry-in and Carry-out

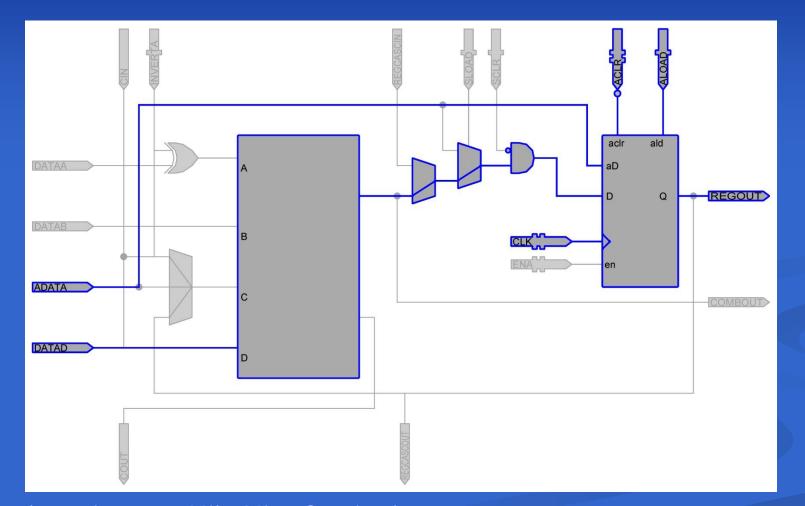

# **ALU Example**

```

ENTITY alu8 IS PORT (

a, b : IN std logic vector (7 DOWNTO 0);

addsub : IN std logic;

gt, zero, co : OUT std logic;

: OUT std_logic_vector (7 DOWNTO 0));

r

END ENTITY alu8;

ARCHITECTURE assigns OF alu8 IS

SIGNAL mid : std logic vector (8 DOWNTO 0);

BEGIN

mid <= ('0'& a) + ('0'& b) WHEN addsub = '1' ELSE ('0'& a)

- ('0'& b);

co <= mid (8);

r \ll mid (7 DOWNTO 0);

gt <= '1' WHEN a > b ELSE '0';

zero <='1' WHEN mid (7 DOWNTO 0) = "00000000" ELSE '0';</pre>

END assigns;

```

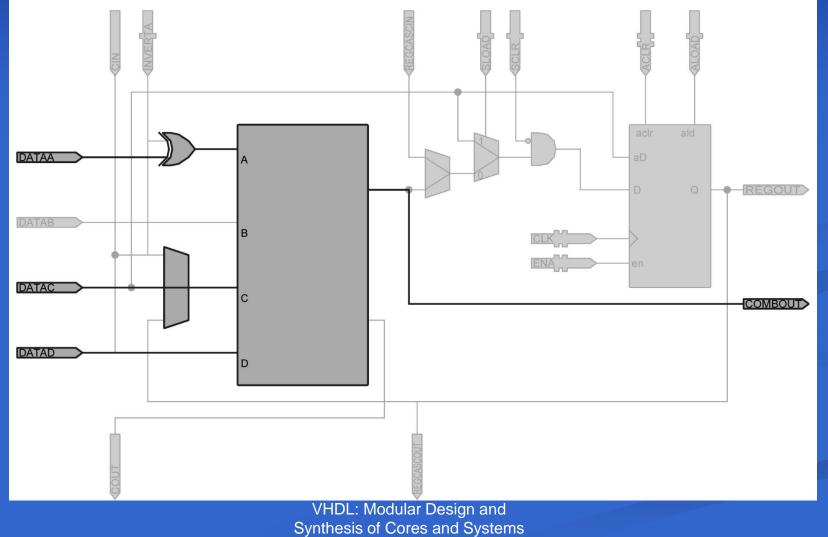

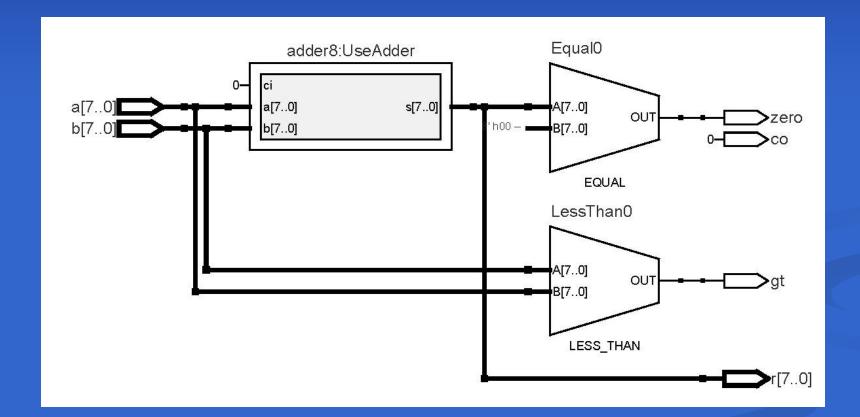

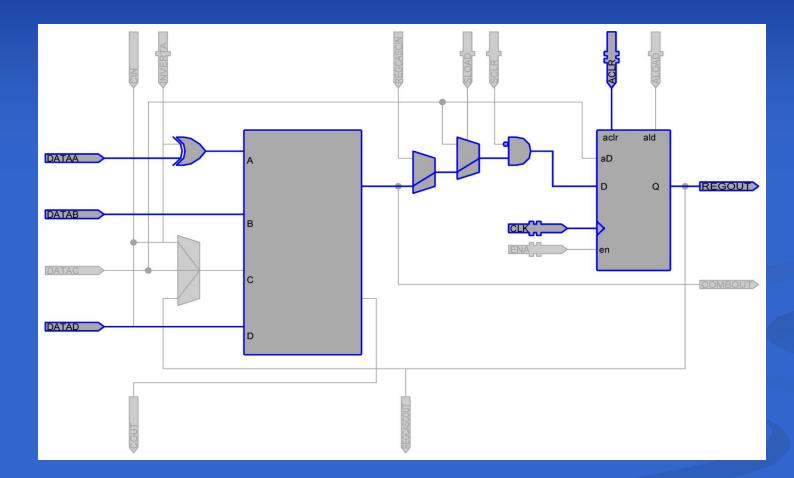

# **ALU Example Using Adder**

**ENTITY** alu8add **IS PORT** (

a, b : **IN** std\_logic\_vector (7 DOWNTO 0);

gt, zero, co : OUT std\_logic;

r : **OUT** std\_logic\_vector (7 DOWNTO 0));

**END ENTITY** alu8add;

**ARCHITECTURE** assigns **OF** alu8add IS

**SIGNAL** mid8 : std\_logic\_vector (7 DOWNTO 0);

**SIGNAL** mid1 : std\_logic;

**BEGIN**

AD: ENTITY WORK.adder8 PORT MAP (a, b, '0', mid8, OPEN);

-- AD: ENTITY WORK.adder8 PORT MAP

--

$$(a => a, b => b, ci => '0', s => mid8);$$

$r \leq mid8;$

gt <= '1' **WHEN** a > b **ELSE** '0';

zero <= '1' **WHEN** mid8 = "00000000" **ELSE** '0';

**END** assigns;

#### ALU VHDL Code Using Instantiating an Adder

### Synthesis of Assignment Statements

ALU\_Adder RTL View after Synthesis

### Synthesis of Assignment Statements

#### ALU\_Adder RTL View after Synthesis

# Descriptions with Sequential Flow

#### Procedural Block Describing a Majority Circuit

## Majority Example with Delay

## Procedural Multiplexer Example

```

ENTITY multiplexer IS

PORT (a, b, s : IN BIT; w : OUT BIT);

END ENTITY;

--

ARCHITECTURE procedural OF multiplexer IS BEGIN

PROCESS (a, b, s) BEGIN

IF (s = '0') THEN w <= a;

ELSE w <= b;

END IF;

END PROCESS;

END ARCHITECTURE procedural;</pre>

```

#### Sequential Flow Multiplexer

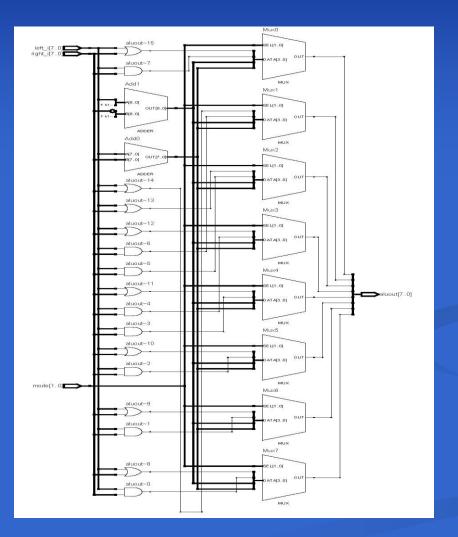

## Procedural ALU Example

```

ENTITY alu8 IS

PORT (left_i, right_i: IN std_logic vector (7 DOWNTO 0);

mode : IN std_logic_vector (1 DOWNTO 0);

aluout : OUT std_logic_vector (7 DOWNTO 0));

END ENTITY;

___

ARCHITECTURE procedural OF alu8 IS BEGIN

PROCESS (left i, right i, mode) BEGIN

CASE mode IS

WHEN "00" => aluout <= left i + right i;

WHEN "01" => aluout <= left i - right i;

WHEN "10" => aluout <= left i AND right i;

WHEN "11" => aluout <= left i OR right i;

WHEN OTHERS => aluout <= "XXXXXXXXX";

END CASE;

END PROCESS;

END ARCHITECTURE procedural;

```

```

ENTITY bussing IS

PORT (

busin1: IN std logic vector (3 DOWNTO 0);

busin2: IN std logic vector (3 DOWNTO 0);

busin3: IN std_logic_vector (3 DOWNTO 0);

en1: IN std logic;

en2: IN std logic;

en3: IN std logic;

busout: OUT std logic vector(3 DOWNTO 0) );

END bussing;

___

ARCHITECTURE structural OF bussing IS

BEGIN

busout <= busin1 WHEN en1 = '1' ELSE (OTHERS => 'Z');

busout <= busin2 WHEN en2 = '1' ELSE (OTHERS => 'Z');

busout <= busin3 WHEN en3 = '1' ELSE (OTHERS => 'Z');

END structural;

```

#### Three-state Bussing

# Synthesizing Procedural Blocks

Synthesis of

Sequential Flow ALU

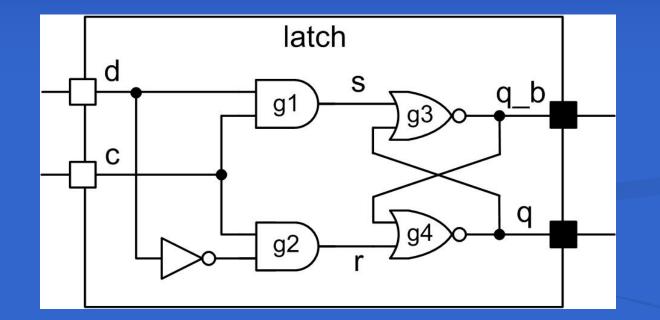

### Basic Memory Elements at the Gate Level

Clocked D-latch

### Basic Memory Elements at the Gate Level

```

ENTITY latch IS

PORT (d, c: IN std_logic;

q, q_b : BUFFER std_logic);

END latch;

ARCHITECTURE structural OF latch IS

SIGNAL s, r : std_logic;

BEGIN

s <= c AND d AFTER 6 ns;

r <= c AND (NOT d) AFTER 6 ns;

q_b <= s NOR q AFTER 4 ns;

q <= r NOR q_b AFTER 4 ns;

END structural;</pre>

```

#### • 37 VHDL Code for a Clocked D-latch

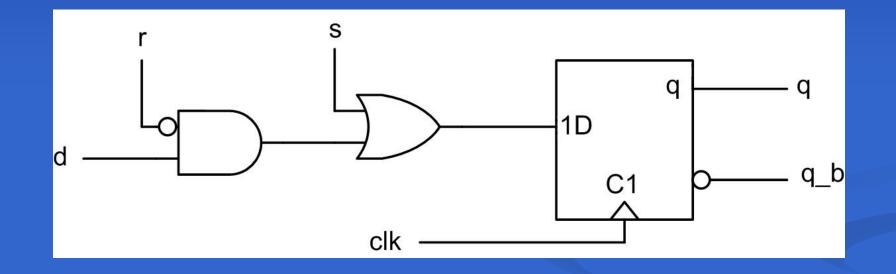

## Basic Memory Elements at the Gate Level

```

ENTITY master_slave IS

PORT (d, c: IN std logic;

q : OUT std_logic);

END master_slave;

ARCHITECTURE dual OF master_slave IS

SIGNAL qm : std_logic;

BEGIN

qm <= d WHEN c = '1';

q <= qm WHEN c = '0';

END dual;</pre>

```

#### Master-Slave Flip-Flop

## Memory Elements Using Procedural Statements

```

ENTITY latch1 IS

PORT (d, c: IN std_logic; q: OUT std_logic);

END latch1;

ARCHITECTURE behavioral OF latch1 IS

BEGIN

PROCESS (d, c)

BEGIN

IF c = '1' THEN

q <= d;

END IF;

END PROCESS;

END ARCHITECTURE behavioral;</pre>

```

#### Procedural Latch

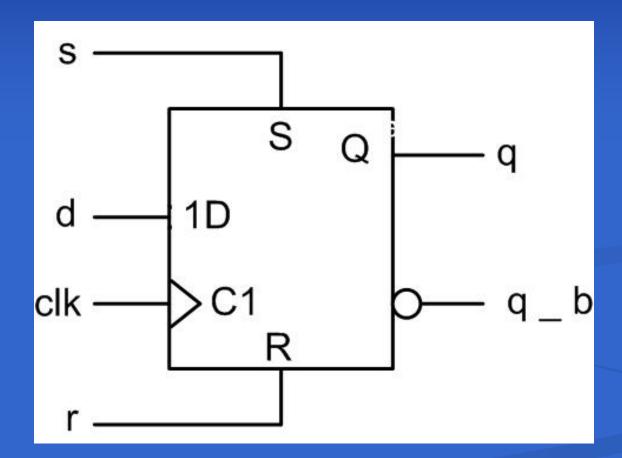

# D Flip-Flop

```

ENTITY DFF1 IS

PORT (d, clk: IN std logic; q : OUT std logic);

END DFF1;

___

ARCHITECTURE behavioral OF DFF1 IS

BEGIN

PROCESS (clk)

BEGIN

IF clk = '1' AND clk'EVENT THEN

q \leq d;

END IF;

END PROCESS;

END ARCHITECTURE behavioral;

```

#### A Positive-Edge D Flip-Flop

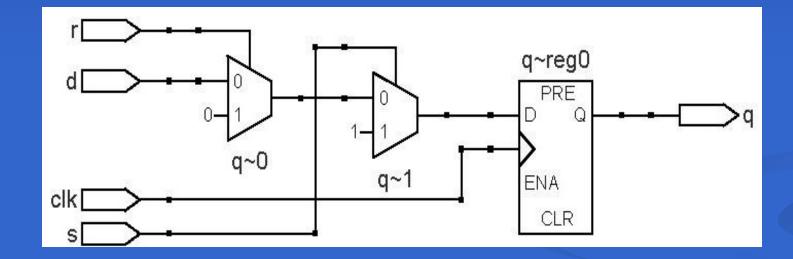

### Synchronous Control

```

ENTITY DFF1sr IS

PORT (d, clk, s, r: IN std logic; q : OUT std logic);

END DFF1sr;

____

ARCHITECTURE behavioral OF DFF1sr IS

BEGIN

PROCESS (clk)

BEGIN

IF clk = '1' AND clk'EVENT THEN

IF s = '1' THEN

q <= '1';

ELSIF r = '1' THEN

q <= '0';

ELSE

q <= d;

END IF;

END IF;

END PROCESS;

END ARCHITECTURE behavioral;

```

### Synchronous Control

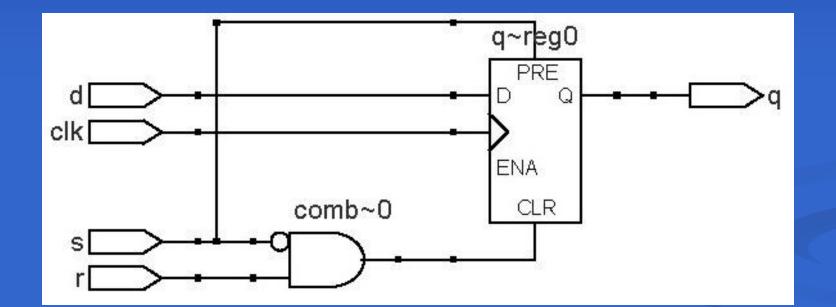

### Asynchronous Control

```

ARCHITECTURE asynchronous OF DFF1sr IS

BEGIN

PROCESS (clk, s, r) BEGIN

IF s = '1' THEN

q <= '1';

ELSIF r = '1' THEN

q <= '0';

ELSIF clk = '1' AND clk'EVENT THEN

q <= d;

END IF;

END PROCESS;

END ARCHITECTURE asynchronous;</pre>

```

### Asynchronous Control

Synchronous Flip-Flop Synthesis

Asynchronous Flip-Flop Synthesis

VHDL: Modular Design and

d

q

```

ENTITY register8 IS

PORT (

: IN std logic vector (7 DOWNTO 0);

: IN std_logic; clk, s, r

: OUT std_logic_vector (7 DOWNTO 0));

END register8;

____

ARCHITECTURE behavioral OF register8 IS

BEGIN

PROCESS (clk)

BEGIN

IF clk = '1' AND clk'event THEN

IF s = '1' THEN

q <= (OTHERS => '1');

ELSIF r = '1' THEN

q \leq (OTHERS = '0');

ELSE

q \leq d;

END IF;

END IF;

END PROCESS;

END behavioral;

```

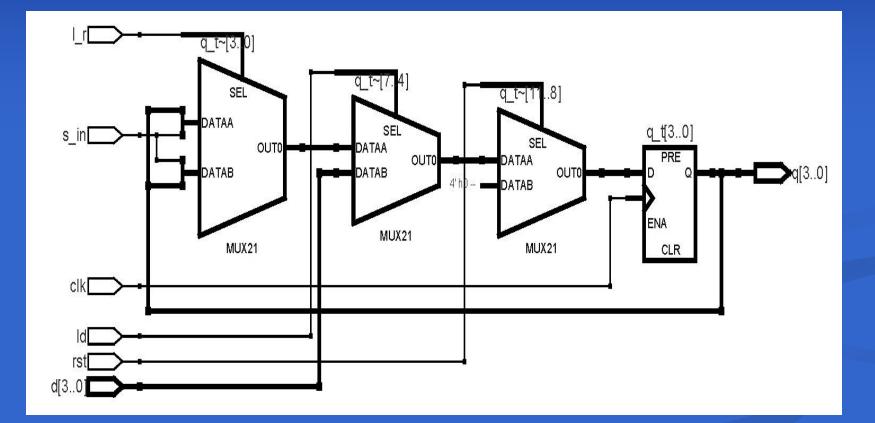

```

ENTITY shift reg4 IS

PORT (

d : IN std logic vector (3 DOWNTO 0);

clk, ld, rst, l_r, s_in : IN std_logic;

q : OUT std_logic vector (3 DOWNTO 0));

END shift reg4;

ARCHITECTURE behavioral OF shift_reg4 IS

BEGIN

PROCESS (clk)

VARIABLE q t: std logic vector (3 DOWNTO 0);

BEGIN

IF rising_edge (clk) THEN

IF rst= '1' THEN

q t := (OTHERS => '0');

ELSIF 1d = '1' THEN

q_t := d;

ELSIF 1 r = '1' THEN

qt := qt (2 DOWNTO 0) \& s in ;

ELSE

q_t := s_{in} \& q_t (3 \text{ DOWNTO } 1);

END IF;

END IF;

q \leq q t;

END PROCESS;

END behavioral;

```

#### Counters

```

ENTITY counter4 IS

PORT (reset, clk : IN std logic;

count : OUT std_logic_vector (3 DOWNTO 0));

END ENTITY;

___

ARCHITECTURE procedural OF counter4 IS

SIGNAL cnt reg : std logic vector (3 DOWNTO 0);

BEGIN

PROCESS (clk)

BEGIN

IF (clk = '0' AND clk'EVENT) THEN

IF (reset='1') THEN

cnt req <="0000" AFTER 1.2 NS;

ELSE

cnt_reg <= cnt_reg + 1 AFTER 1.2 NS;</pre>

END IF;

END IF;

END PROCESS;

count <= cnt reg;</pre>

END ARCHITECTURE procedural;

```

#### Synthesis of Shifters and Counters

Shift Register Synthesis RTL View

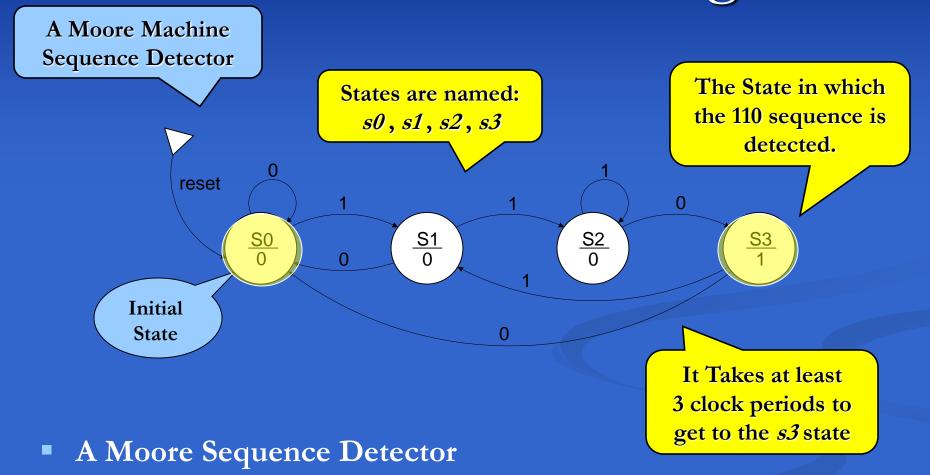

### **State Machine Coding**

### Moore Machine VHDL Code

```

ENTITY detector110 IS

WHEN S1 =>

PORT (a, clk, reset : IN std logic; w : OUT

IF a='1' THEN current <= S2;

std logic);

ELSE current <= S0; END IF;

END ENTITY;

WHEN S2 =>

___

IF a='1' THEN current <= S2;

ARCHITECTURE procedural OF detector110 IS

ELSE current <= S3; END IF;

TYPE state IS (S0, S1, S2, S3);

WHEN S3 =>

SIGNAL current : state := S0;

IF a='1' THEN current <= S1;

BEGIN

ELSE current <= S0; END IF;

PROCESS (clk) BEGIN

WHEN OTHERS => current <= S0;

IF (clk = '0' AND clk'EVENT) THEN

END CASE;

IF reset = '1' THEN current <= S0;

END IF;

ELSE

END IF;

CASE current IS

END PROCESS;

WHEN SO =>

w \leq '1' WHEN current = S3 ELSE '0';

IF a='1' THEN current <= S1;

END ARCHITECTURE procedural;

ELSE current <= S0; END IF;</pre>

```

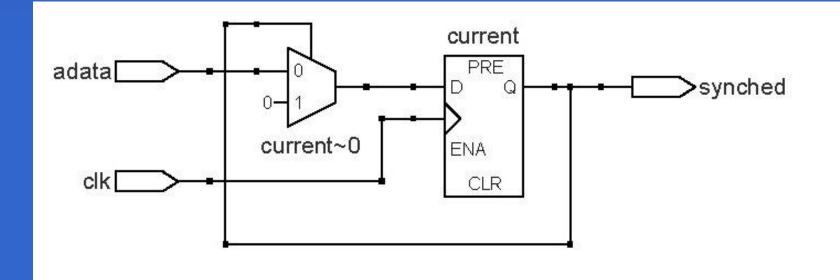

#### **Pulse Synchronizer**

```

ENTITY synchronizer IS

PORT (clk, adata : IN std logic;

synched : OUT std logic);

END ENTITY;

___

ARCHITECTURE procedural OF synchronizer IS

TYPE state IS (S0, S1);

SIGNAL current : state;

BEGIN

PROCESS (clk) BEGIN

IF (rising edge(clk)) THEN

IF current = S0 THEN

IF adata = '0' THEN

current <= S0;

ELSE

current \leq S1;

END IF;

ELSE -- current = S1

current <= S0;</pre>

END IF;

END IF;

VHDL: Modular Design and

END PROCESS;

Synthesis of Cores and Systems

Uppright Z. NavaSi, 2007 SE '0';

synched <= '1'

WHEN

END ARCHITECTURE procedural;

```

February 2019

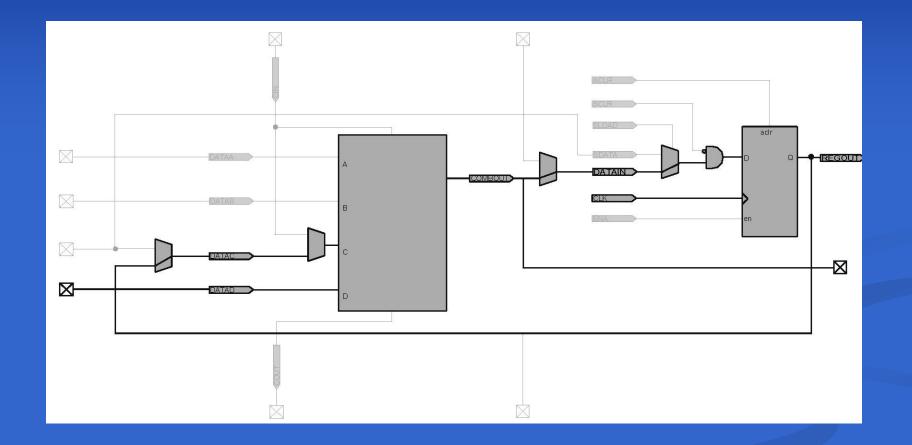

#### **State Machine Synthesis**

### **State Machine Synthesis**

# Writing Testbenches

```

ARCHITECTURE . . .

TYPE memory IS

ARRAY (INTEGER RANGE <>) OF

std logic vector (7 DOWNTO 0);

SIGNAL mem: memory(0 to 1023);

BEGIN

PROCESS (mem)

VARIABLE memv: memory(0 to 15);

VARIABLE data: std logic vector(7 DOWNTO 0);

VARIABLE short_data: std_logic_vector(3 DOWNTO 0);

BEGIN

. . .

data := mem(956);

short data := mem(931) (6 downto 3);

memv (12) := mem(189);

mem (932) <= data ;

mem (321)(5 DOWNTO 2) <= short data;</pre>

mem (940) <= "0000" & short data ;

END PROCESS;

• • •

VHDL: Modular Design and

END ARCHITECTURE;

Synthesis of Cores and Systems

```

Copyright Z. Navabi, 2007

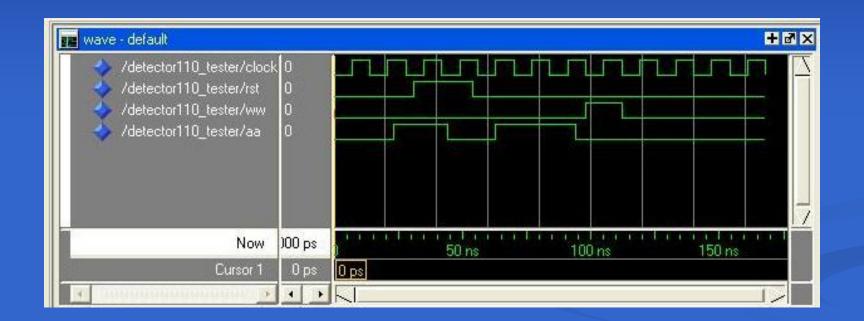

# Writing Testbenches

```

ENTITY detector110 tester IS END ENTITY;

___

ARCHITECTURE timed OF detector110 tester IS

SIGNAL aa, clock, rst, ww : std logic := '0';

BEGIN

UUT1: ENTITY WORK.detector110 (procedural)

PORT MAP (aa, clock, rst, ww);

rst <= '1' AFTER 31 NS, '0' AFTER 54 NS;</pre>

clock <= NOT clock AFTER 7 NS WHEN NOW<=165 NS ELSE '0';

PROCESS BEGIN

WAIT FOR 23 NS; aa \leq 1';

WAIT FOR 21 NS; aa \leq '0';

WAIT FOR 19 NS; aa \leq 1';

WAIT FOR 31 NS; aa \leq '0';

WAIT;

END PROCESS;

PROCESS (ww) BEGIN

REPORT "Signal w changed to: "& std logic 'IMAGE (ww) &

" at " & TIME ' IMAGE (NOW)

SEVERITY NOTE;

VHDL: Modular Design and

END PROCESS;

END ARCHITECTURE timed; Convint of Cores and Systems

```

February 2019

# Writing Testbenches

#### Testbench Waveform Results

## Summary

- This chapter presented:

- RT level description in the VHDL HDL language

- examples of synthesizable one-to-one hardware correspondence

- introducesing some VHDL terminologies that are needed for understanding the linguistics of VHDL

- How testbenches could be developed in VHDL and new constructs of it in this part