# Course Overview

- Semiconductor physics

- PN junction

- BJT physics

- BJT Model

- MOSFET

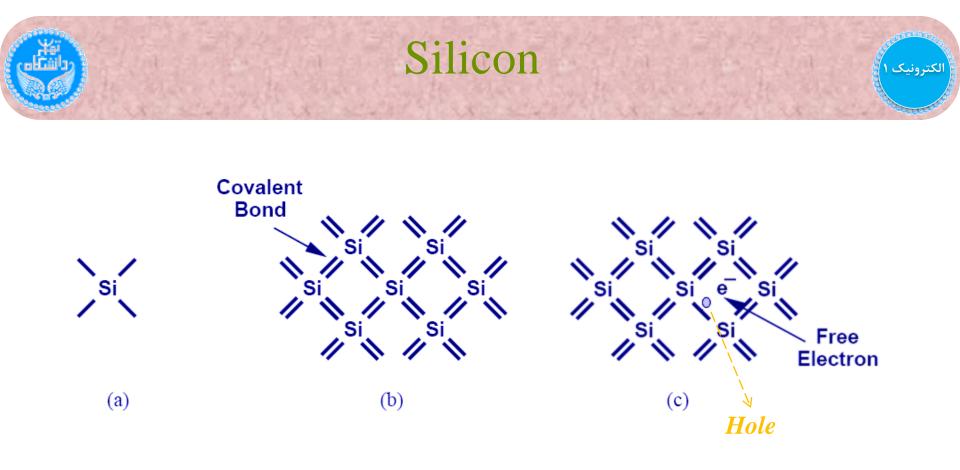

- Si has four valence electrons. Therefore, it can form covalent bonds with four of its neighbors.

- When temperature goes up, electrons in the covalent bond can become free.

- $E_g$ , or bandgap energy determines how much effort is needed to break off an electron from its covalent bond.

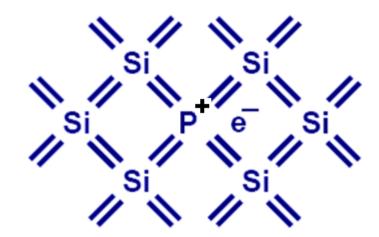

# Doping (N type)

Free electron density: nHole density: pDonor concentration:  $N_d$  $n=p+N_d$

- Pure Si can be doped with other elements to change its electrical properties.

- For example, if Si is doped with group-V elements such as P (phosphorous), then it has more electrons, or becomes type N (electron).

- Group-V impurities are called Donors

- electron: majority carrier

کترونیک

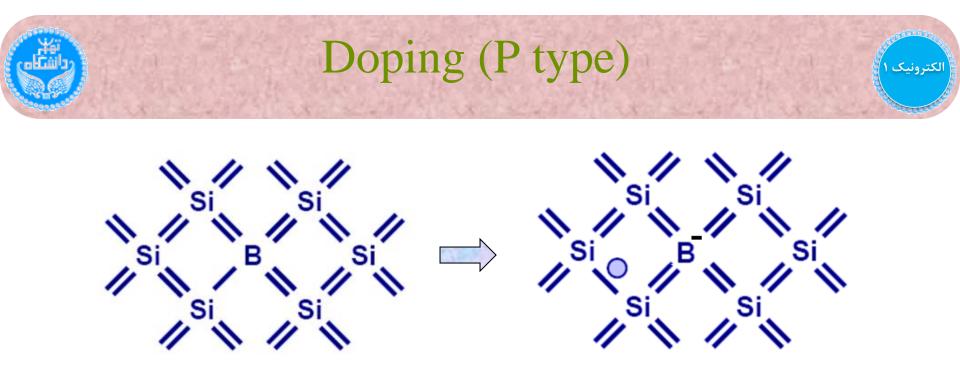

- If Si is doped with group-III elements such as B (boron), then it has more holes, or becomes type P. hole: majority carrier

- Group-III impurities are called Acceptors.

Free electron density: n Hole density: p Acceptor concentration:  $N_a$  $n + N_a = p$

### **Electron and Hole Densities**

• The product of electron and hole densities is ALWAYS equal to the square of intrinsic electron density regardless of doping levels.

$$n.p=n_i^2$$

:Mass Action Law

$$n + N_a = p + N_d$$

|        | Majority Carrier Conc. | Minority Carrier Conc.<br>(Mass Action Law) |

|--------|------------------------|---------------------------------------------|

| N-Туре | $n \approx N_d$        | $p=n_i^2/n$                                 |

| Р-Туре | $p \approx N_a$        | $n=n_i^2/p$                                 |

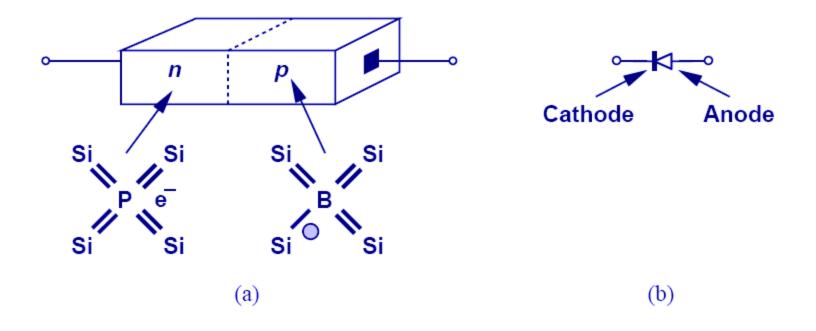

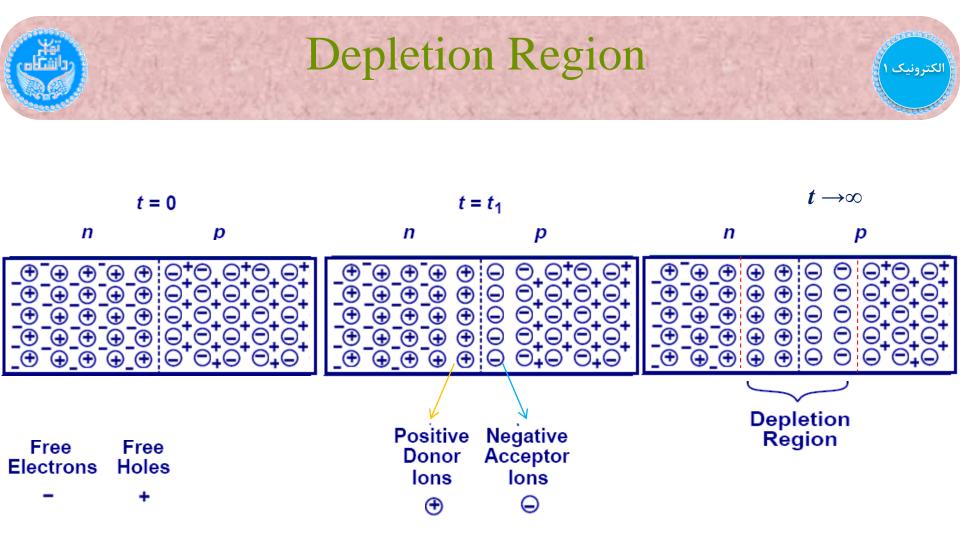

• When N-type and P-type dopants are introduced side-byside in a semiconductor, a PN junction or a diode is formed.

• As free electrons and holes diffuse across the junction, a region of fixed ions is left behind. This region is known as the "depletion region."

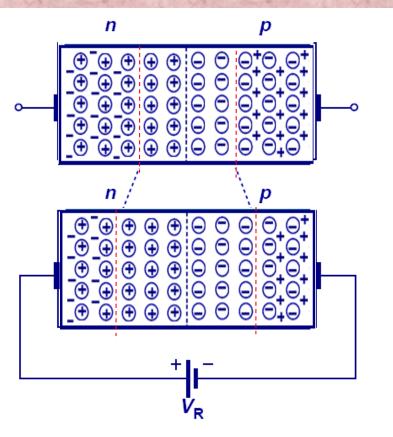

#### Diode in Reverse Bias

• When the N-type region of a diode is connected to a higher potential than the P-type region, the diode is under reverse bias, which results in wider depletion region and larger built-in electric field across the junction.

كترونيك

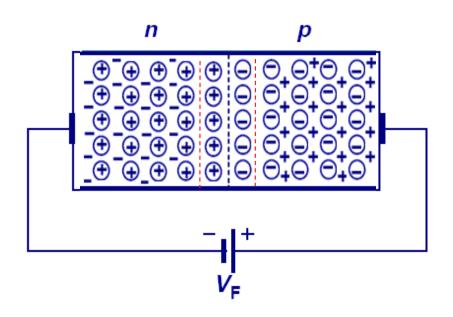

#### Diode in Forward Bias

- When the N-type region of a diode is at a lower potential than the P-type region, the diode is in forward bias.

- The depletion width is shortened and the built-in electric field decreased.

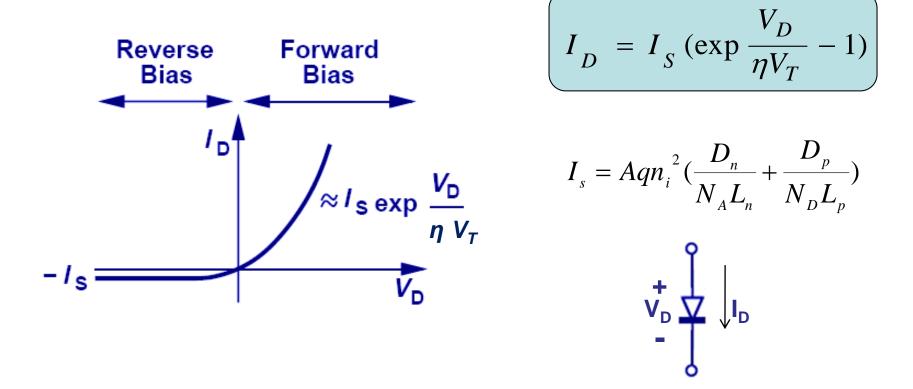

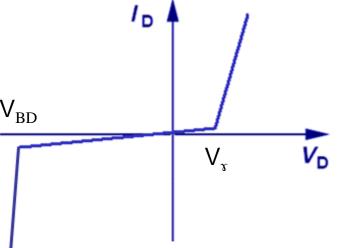

#### IV Characteristic of PN Junction

لكترونيك

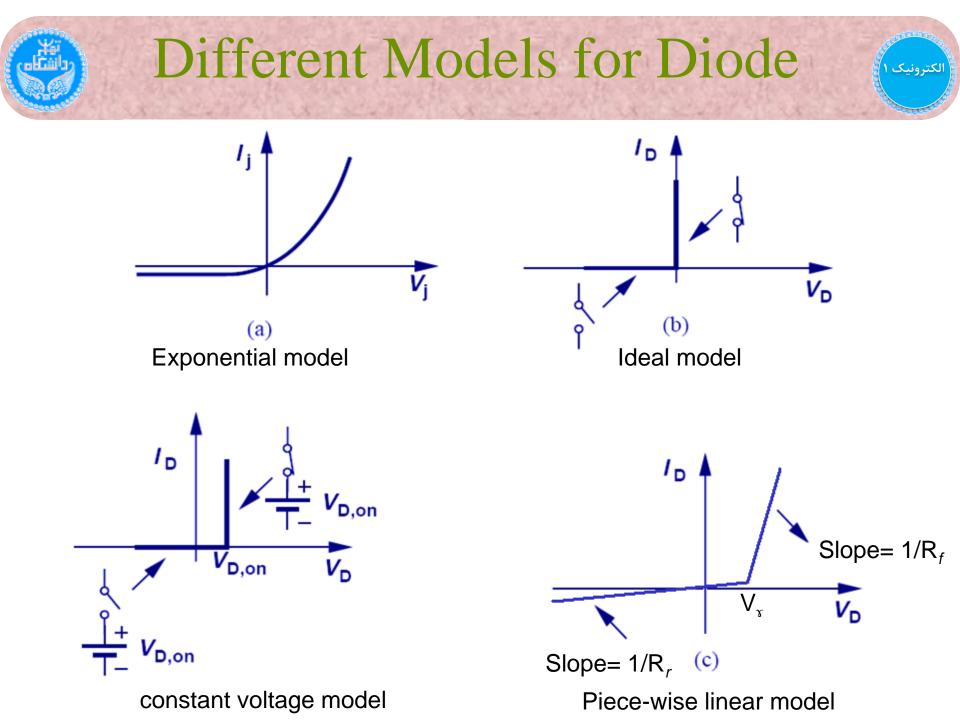

• The current and voltage relationship of a PN junction is exponential in forward bias region, and relatively constant in reverse bias region.

(a)

(b)

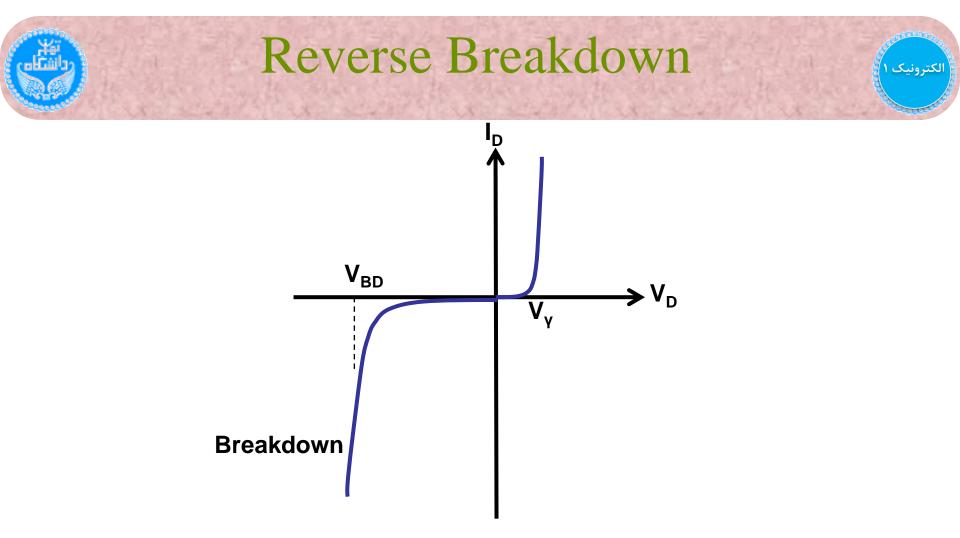

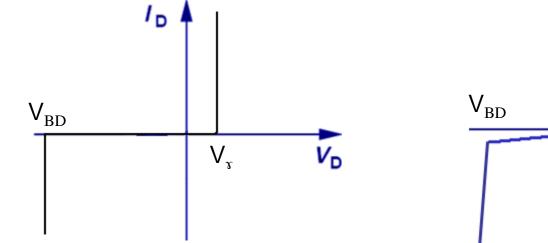

• When a large reverse bias voltage is applied, breakdown occurs and an enormous current flows through the diode.

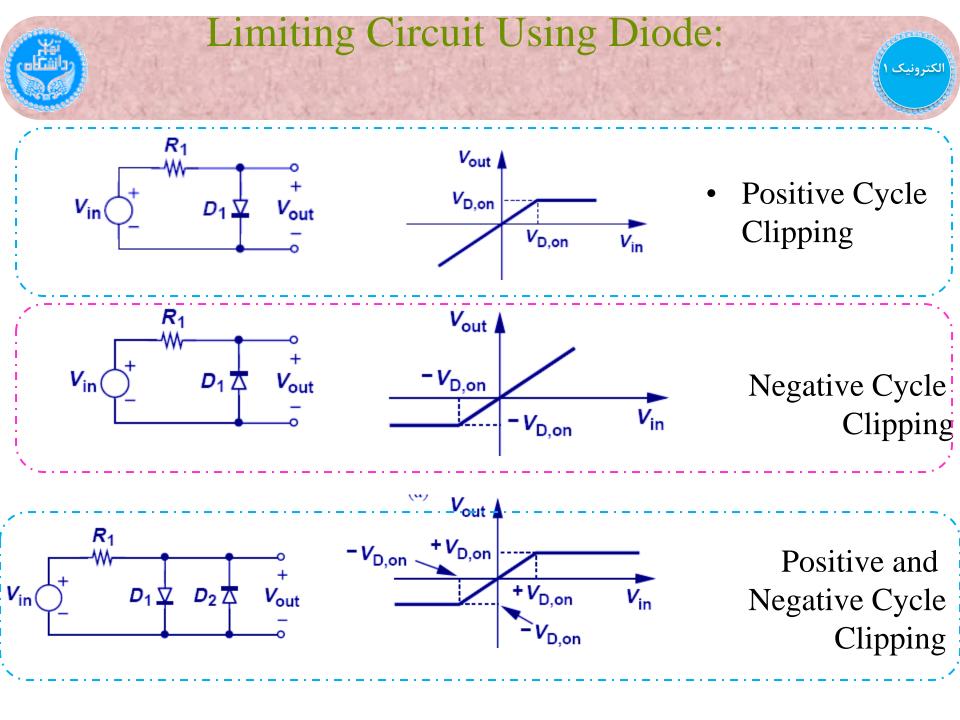

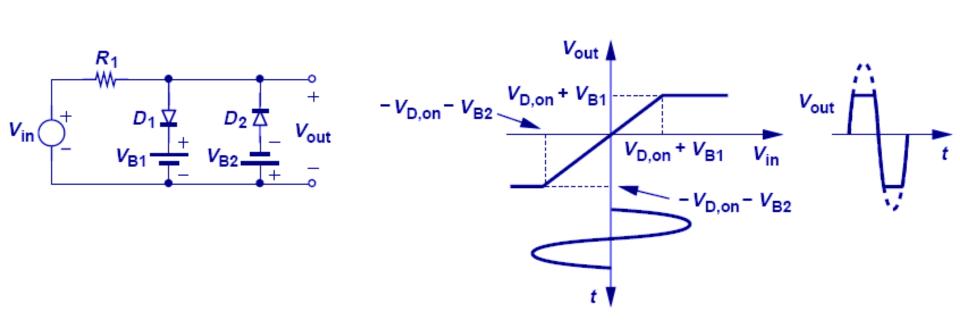

General Voltage Limiting Circuit

الكترونيك

• Two batteries in series with the antiparalle diodes control the limiting voltages.

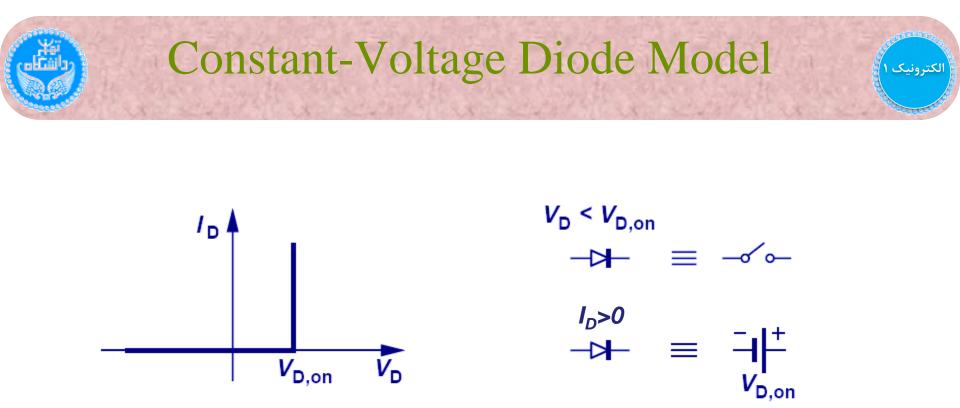

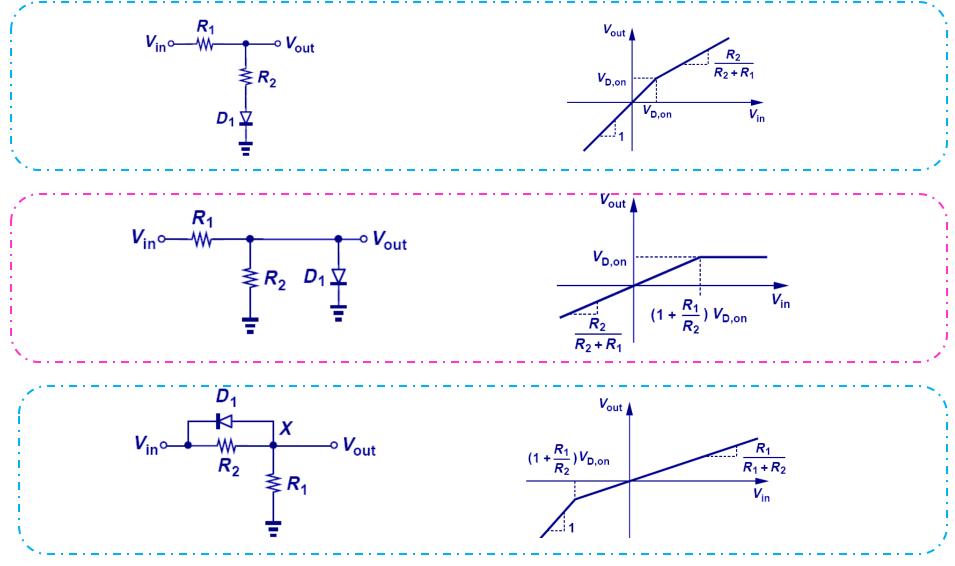

### Input/Output Characteristics with Ideal and Constant-Voltage Models

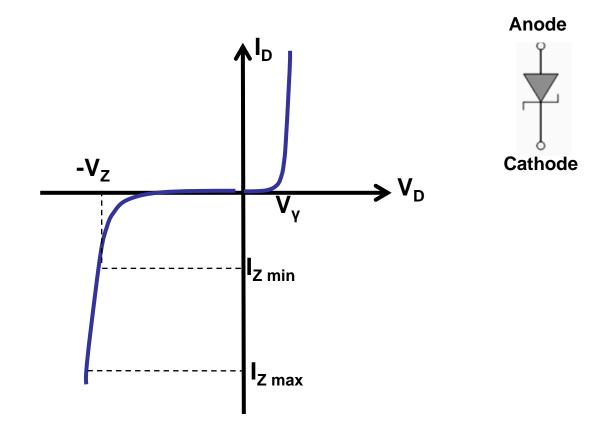

# Zener Diode

، الکترونیک ۱

# Zener Diode: Models

(a)

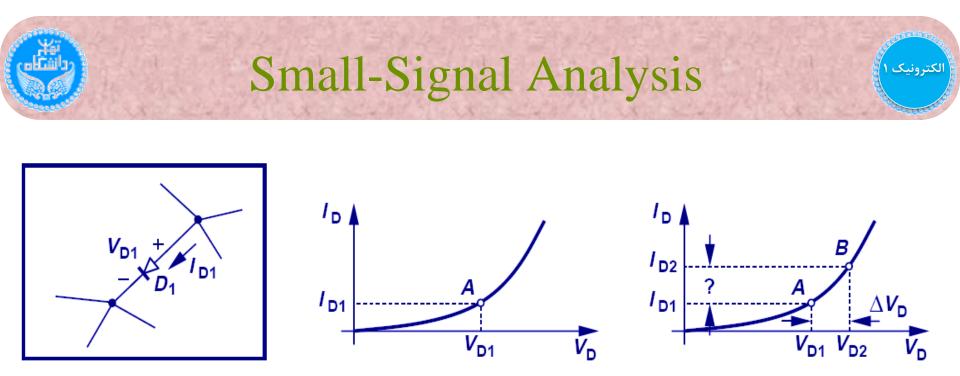

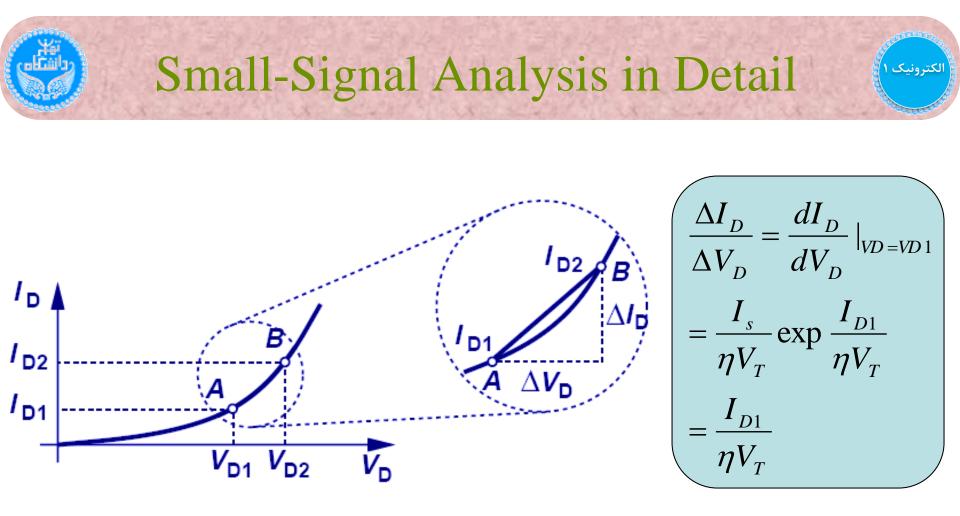

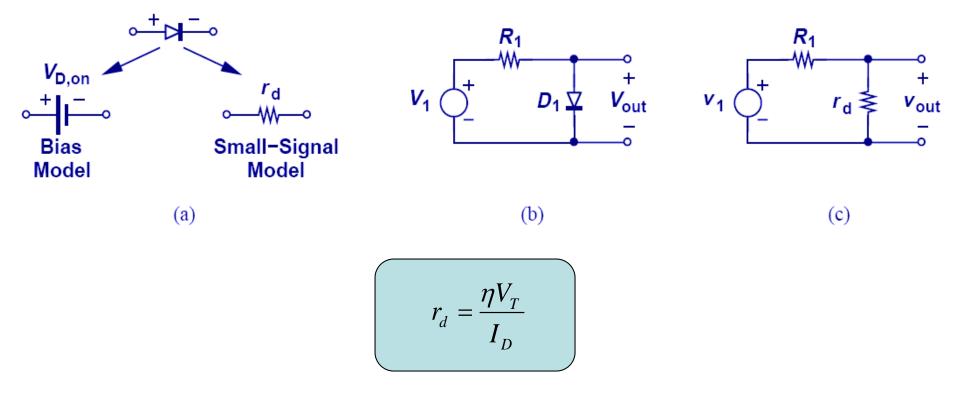

• Small-signal analysis is performed around a bias point by perturbing the voltage by a small amount and observing the resulting linear current perturbation.

(b)

(c)

• If two points on the IV curve of a diode are close enough, the trajectory connecting the first to the second point is like a line, with the slope being the proportionality factor between change in voltage and change in current.

• Since there's a linear relationship between the small signal current and voltage of a diode, the diode can be viewed as a linear resistor when only small changes are of interest.

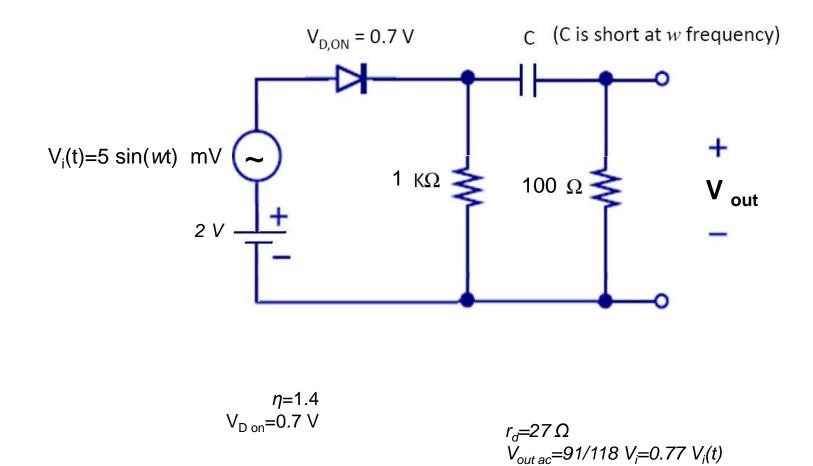

### Example: Small-Signal Analysis

. الکترونیک ۱

# **Course Overview**

- Semiconductor physics

- PN junction

- Physics

- dc analysis

- ac analysis

- BJT physics

- BJT Model

- Amplifiers

- MOSFET

24

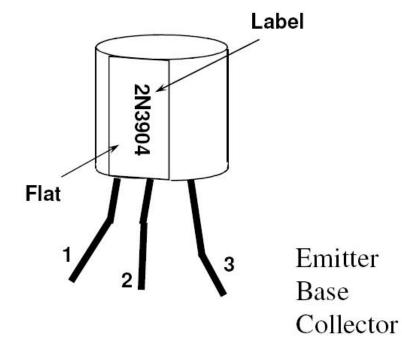

# **Bipolar Transistor**

The world's first transistor, built at Bell Labs in December, 1947.

Transistor inventors (from left), Dr. Walter Brattain, Dr. William Shockley, and Dr. John Bardeen.

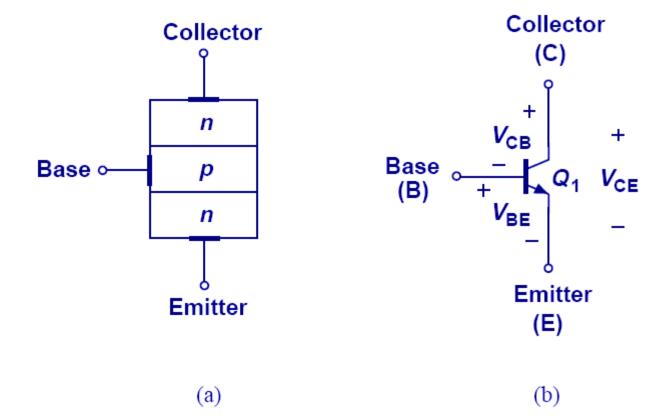

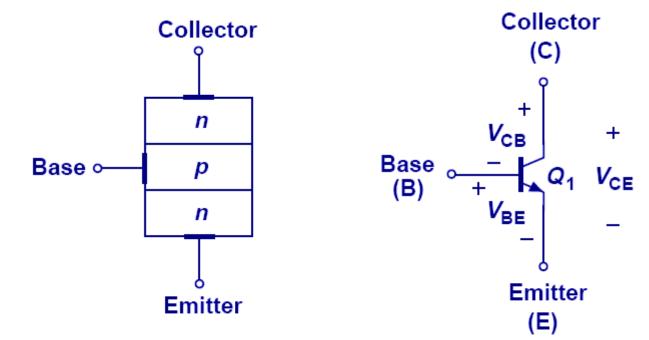

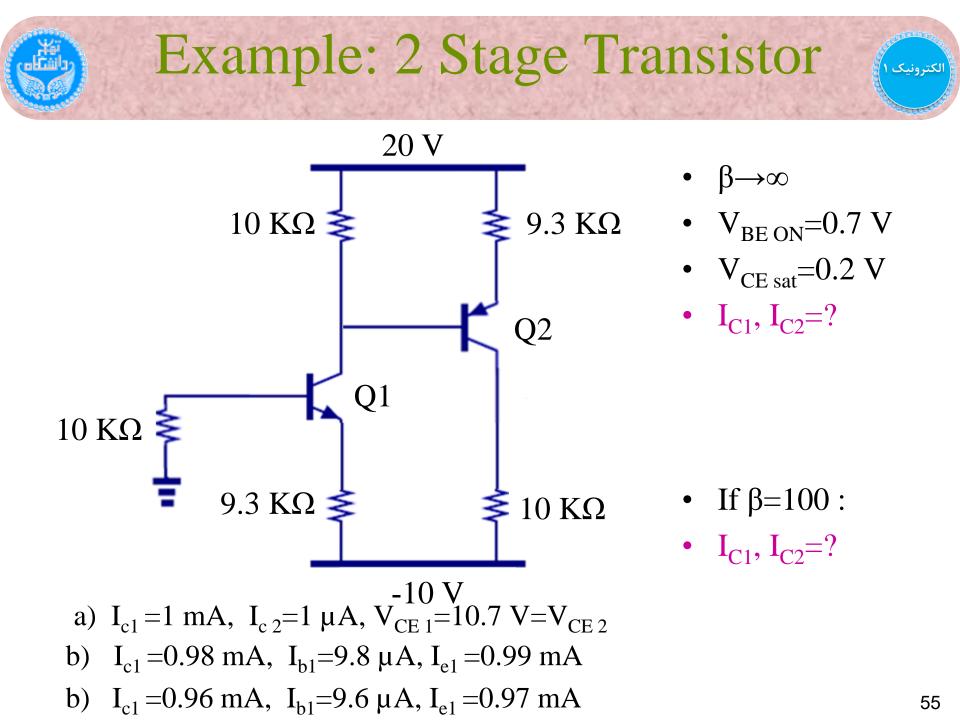

#### Structure and Symbol of Bipolar Transistor

• Bipolar transistor can be thought of as a sandwich of three doped Si regions. The outer two regions are doped with the same polarity, while the middle region is doped with opposite polarity.

#### Structure and Symbol of Bipolar Transistor

| <b>Base-Emitter</b> | <b>Collector-Base</b> | Transistor Mode |

|---------------------|-----------------------|-----------------|

| FB                  | RB                    | Forward active  |

| FB                  | FB                    | Saturation      |

| RB                  | RB                    | Off             |

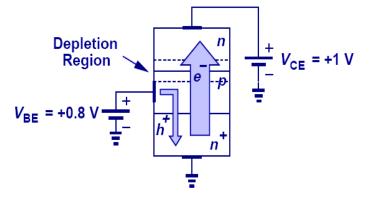

# Accurate Bipolar Representation

• Collector also carries current due to carrier injection from base.

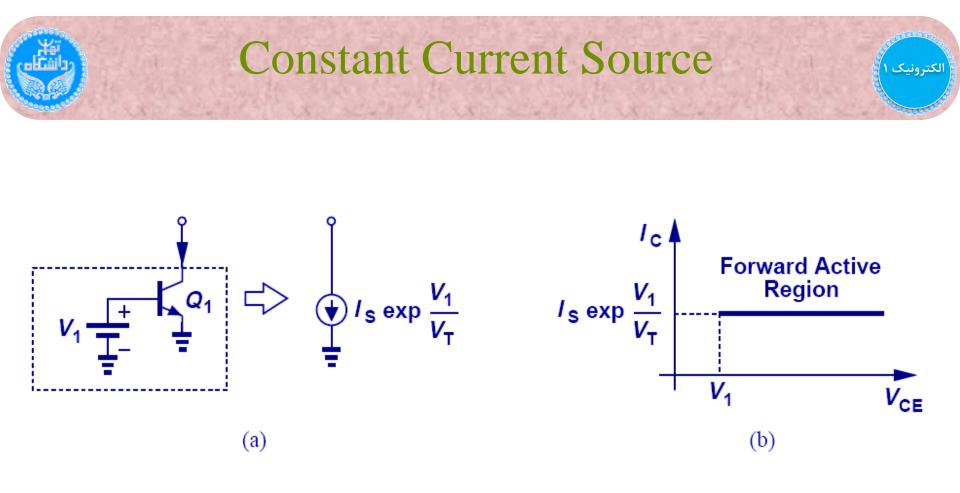

• Ideally, the collector current does not depend on the collector to emitter voltage. This property allows the transistor to behave as a constant current source when its base-emitter voltage is fixed.

#### Currents

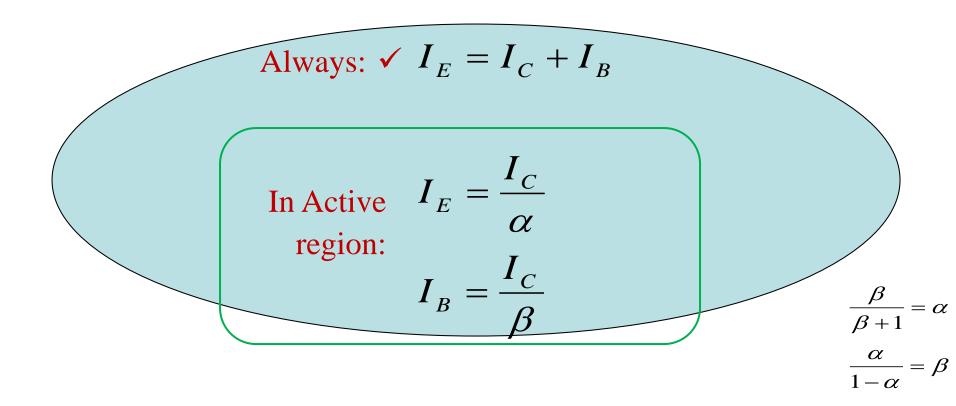

• Applying KCL to the transistor, we can easily find the emitter current.

β, α

الکترونیک ۱

$$\beta \\ \beta + 1 = \alpha$$

90.9 $\frac{\beta}{\beta + 1} = \alpha$ 190.95 $\frac{\alpha}{1 - \alpha} = \beta$ 990.994990.998

$10 \le \beta \le 500$

*Typically:*

$0.9 \le \alpha < 1$

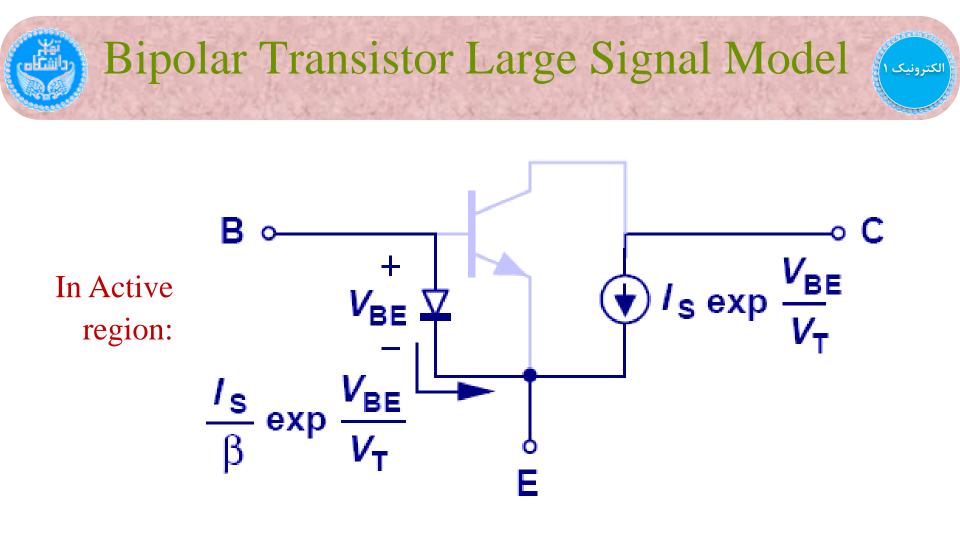

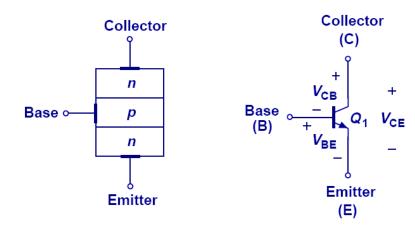

• A diode is placed between base and emitter and a voltage controlled current source is placed between the collector and emitter.

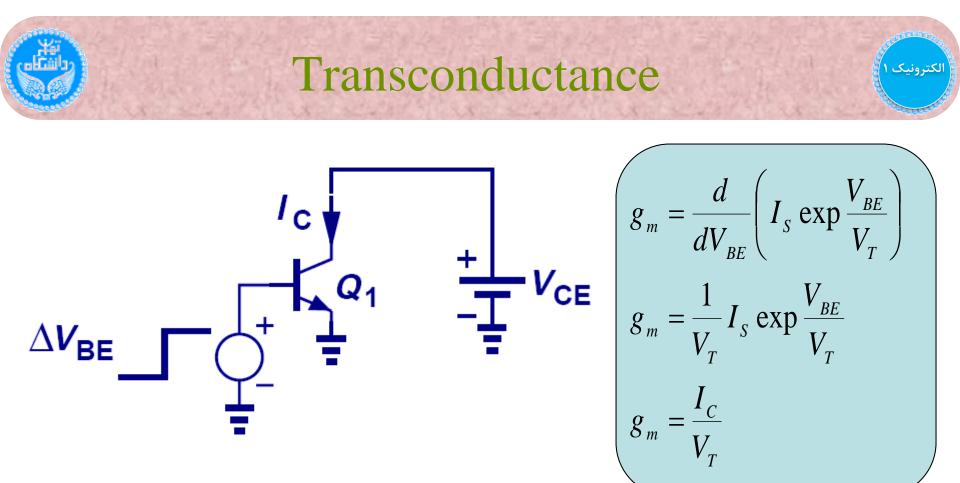

- Transconductance,  $g_m$  shows a measure of how well the transistor converts voltage to current.

- It will later be shown that  $g_m$  is one of the most important parameters in circuit design.

### Visualization of Transconductance ، الکترونیک ۱ 1<sub>c</sub> $m{g}_{\mathsf{m}}\,\Delta m{\mathcal{V}}$ 1<sub>C0</sub> $V_{\mathsf{BE0}}$ $V_{\mathsf{BE}}$ $g_m = \frac{dI_C}{dV_{BE}} \approx \frac{\Delta I_C}{\Delta V_{PE}} = \frac{I_C}{V_T}$ $\Lambda oldsymbol{ u}$ $\Delta I_C \approx g_m \cdot \Delta V_{BE}$

- $g_m$  can be visualized as the slope of  $I_C$  versus  $V_{BE}$ .

- A large  $I_C$  has a large slope and therefore a large  $g_{m.}$

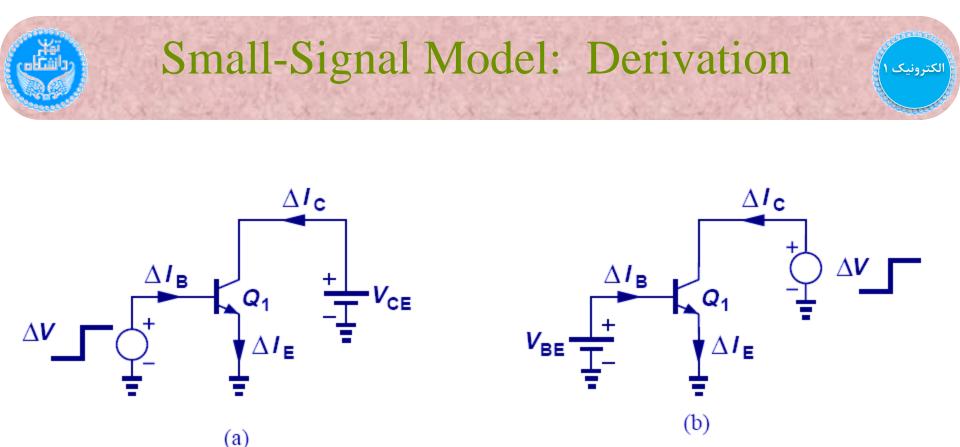

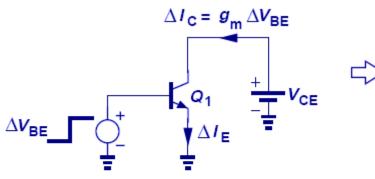

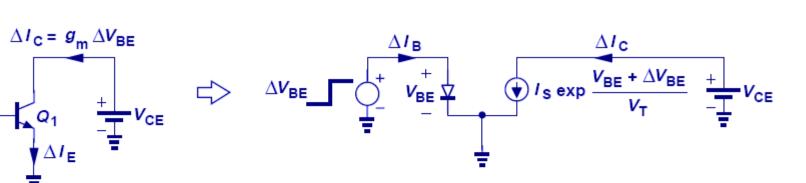

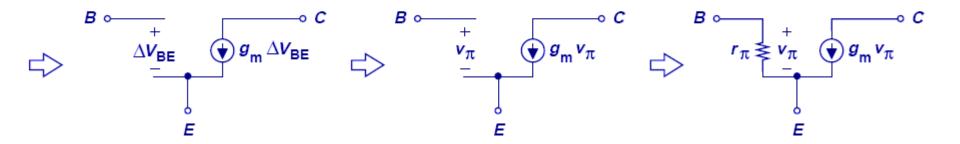

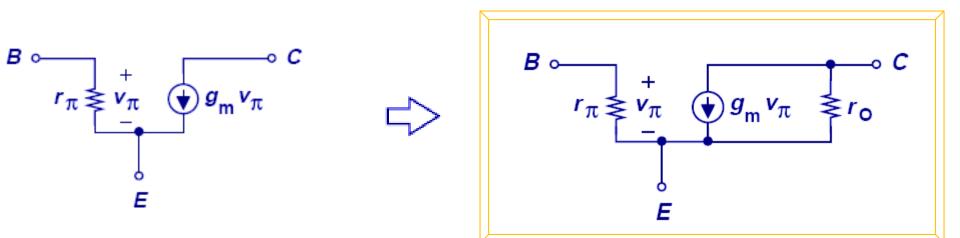

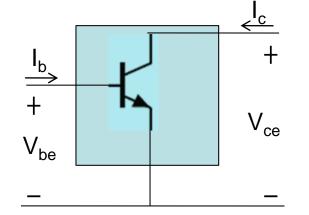

• Small signal model is derived by perturbing voltage difference every two terminals while fixing the third terminal and analyzing the change in current of all three terminals. We then represent these changes with controlled sources or resistors.

# Small-Signal Model: V<sub>BE</sub> Change

CH4 Physics of Bipolar Transistors

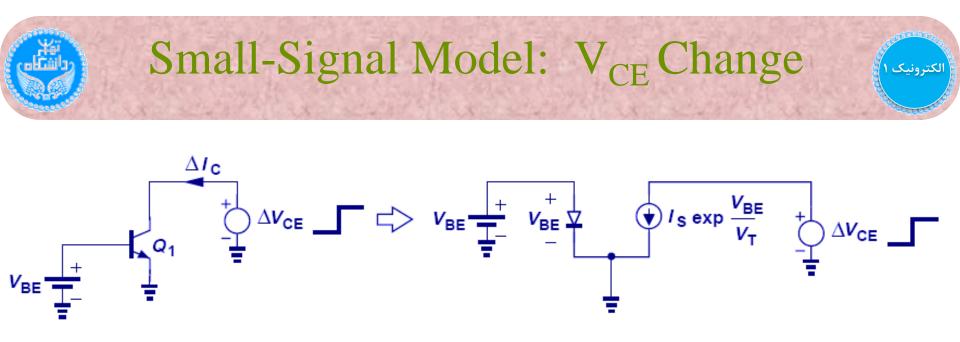

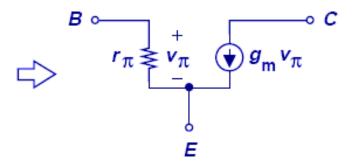

- Ideally,  $V_{CE}$  has no effect on the collector current. Thus, it will not contribute to the small signal model.

- It can be shown that  $V_{CB}$  has no effect on the small signal model, either.

CH4 Physics of Bipolar Transistors

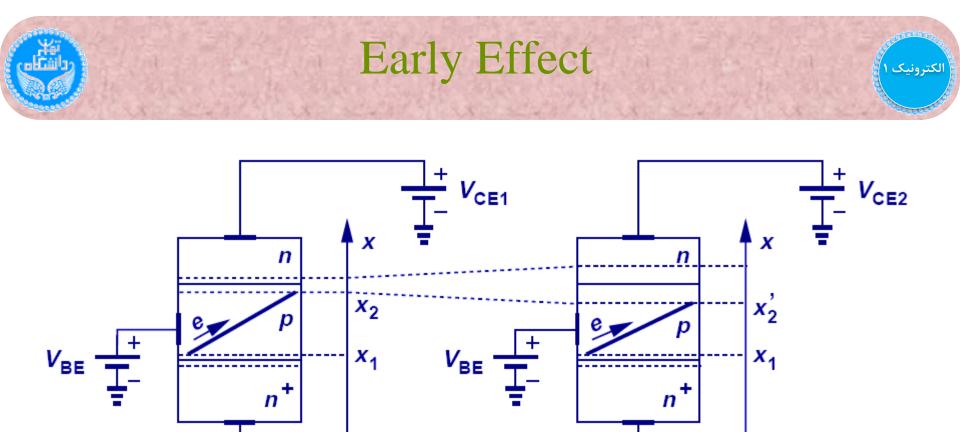

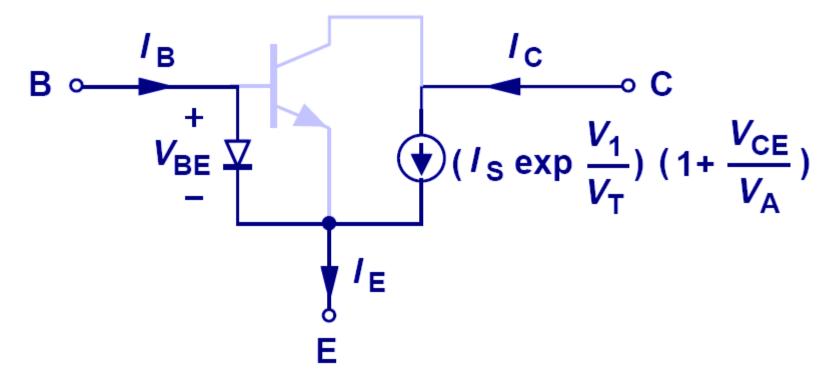

- The claim that collector current does not depend on  $V_{CE}$  is not accurate.

- As  $V_{CE}$  increases, the depletion region between base and collector increases. Therefore, the <u>effective base width</u> <u>decreases</u>, which leads to an increase in the collector current.

#### Early Effect Illustration

- With Early effect, collector current becomes larger than usual and a function of  $V_{\mbox{\scriptsize CE}}$

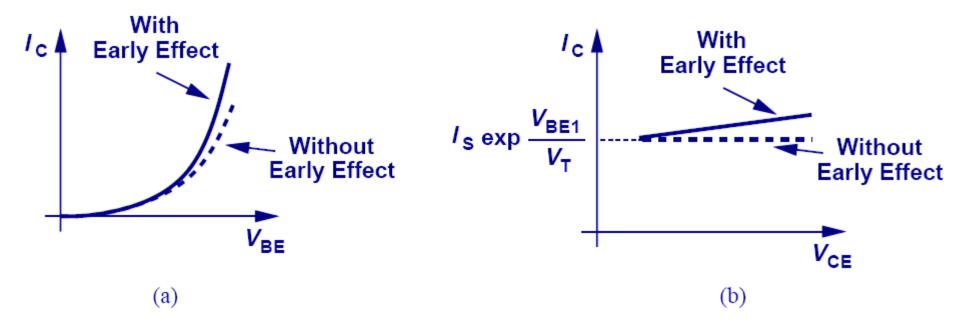

# Early Effect and Large-Signal Model

- Early effect can be accounted for in large-signal model by simply changing the collector current with a correction factor.

- In this mode, base current does not change.

Small-Signal Model of BJT

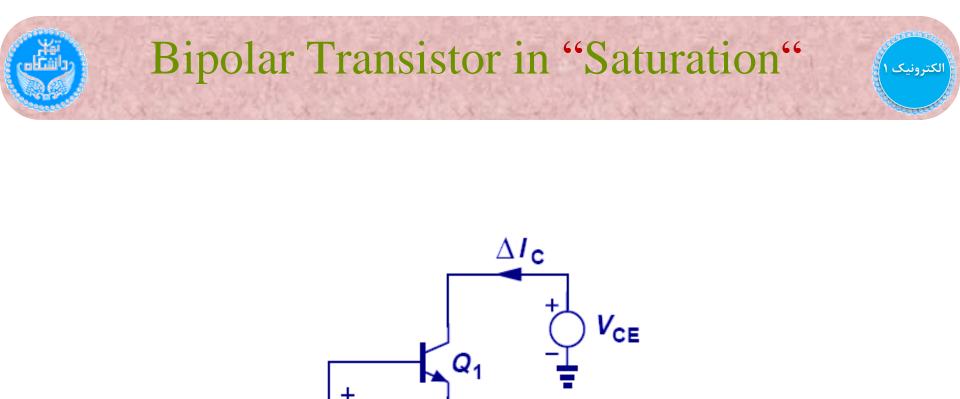

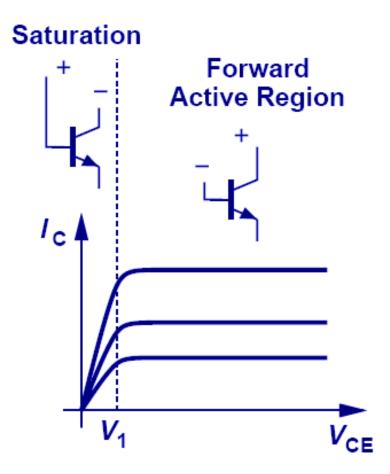

When collector voltage drops below base voltage and forward biases the collector-base junction, <u>base current</u> <u>increases</u> and decreases the current gain factor, β.

$V_{BE}$

#### **Overall I/V Characteristics**

# تکتربیک آ Deep Saturation

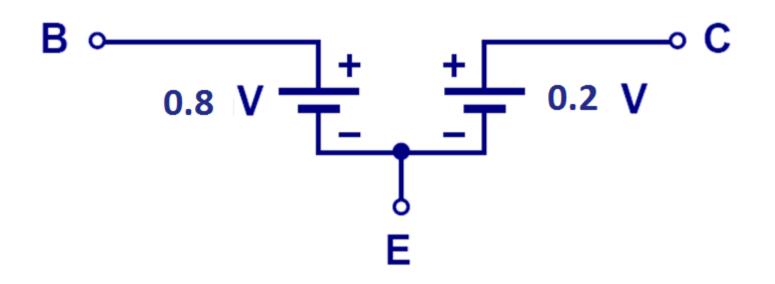

• In deep saturation region, the transistor loses its voltagecontrolled current capability and  $V_{CE}$  becomes constant.

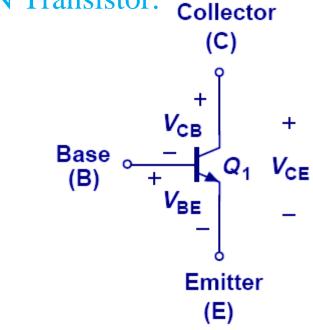

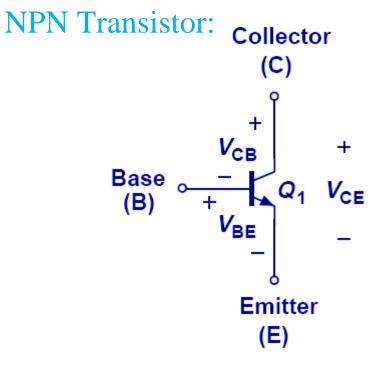

#### NPN Transistor: Active and Saturation المترونية Modes NPN Transistor: Collector

Active mode

$$\frac{V_{BE}=V_{BE ON} (\sim 0.8 V)}{V_{CE}>V_{CE sat} (\sim 0.2 V)}$$

Saturatio  $V_{BE} = V_{BE sat}$  (~ 0.8 V) mode:  $V_{CE} = V_{CE sat}$  (~ 0.2 V)

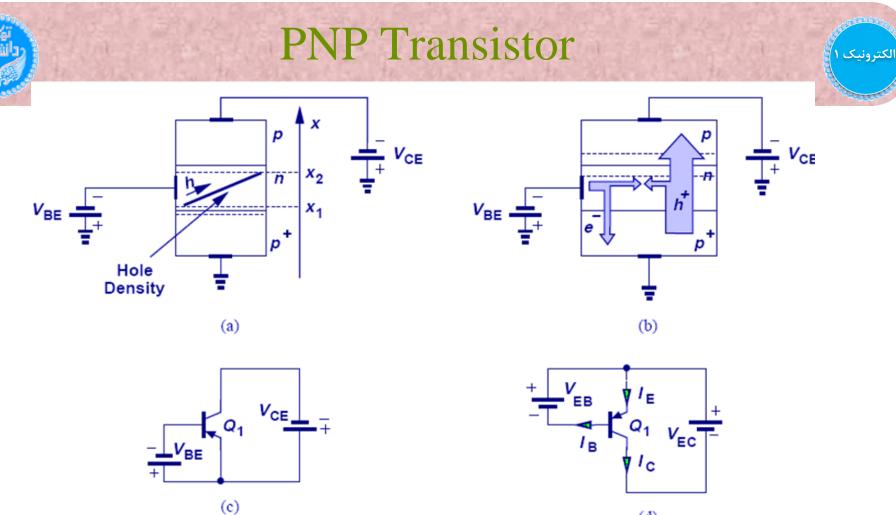

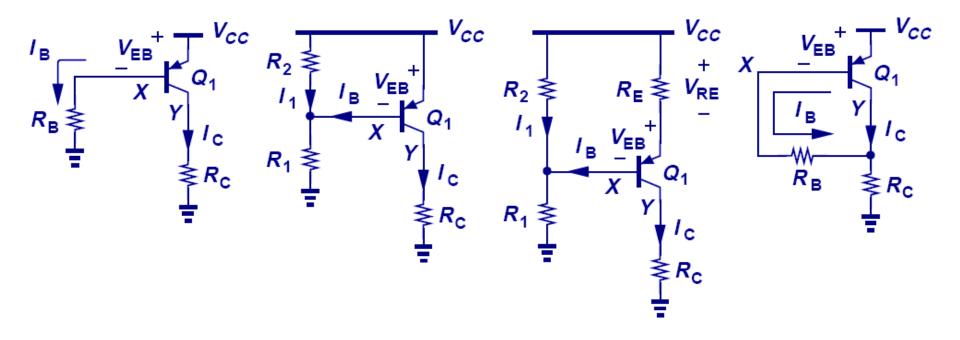

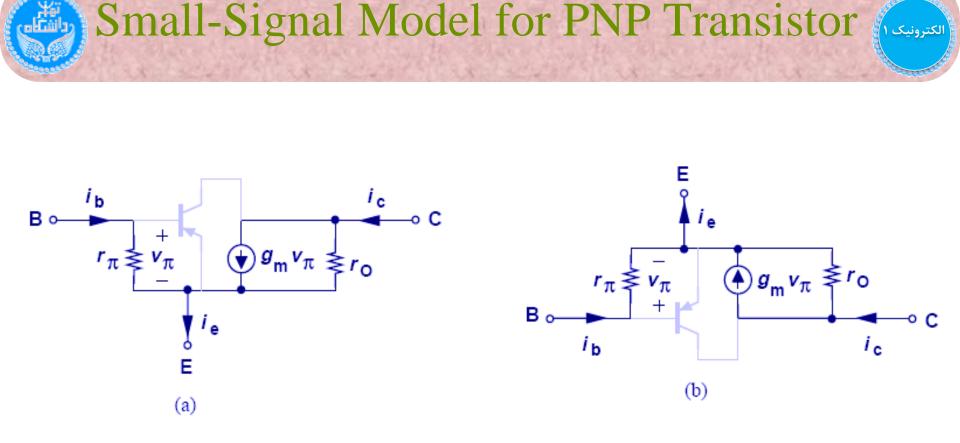

- (d) With the polarities of emitter, collector, and base reversed, a PNP transistor is formed.

- All the principles that applied to NPN's also apply to PNP's, with the exception that emitter is at a higher potential than base and base at a higher potential than collector.

## **PNP** Equations

لكترونيك

$I_{C} = I_{S} \exp \frac{V_{EB}}{V_{T}}$  $I_{B} = \frac{I_{S}}{\beta} \exp \frac{V_{EB}}{V_{T}}$  $I_{E} = \frac{\beta + 1}{\beta} I_{S} \exp \frac{V_{EB}}{V_{T}}$  $I_{C} = \left(I_{S} \exp \frac{V_{EB}}{V_{T}}\right) \left(1 + \frac{V_{EC}}{V_{A}}\right)$ Early Effect

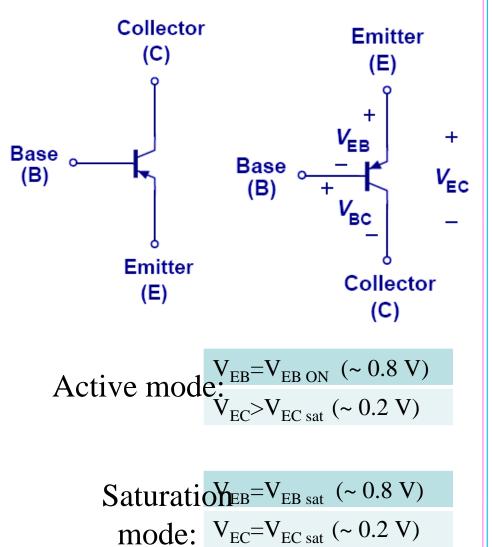

#### Summary of Active and Saturation Modes

#### **PNP** Transistor:

الكترونيك

Active mode

$$\underbrace{V_{BE}=V_{BE ON} (\sim 0.8 V)}_{V_{CE}>V_{CE sat} (\sim 0.2 V)}$$

Saturatio  $V_{BE} = V_{BE sat}$  (~ 0.8 V) mode:  $V_{CE} = V_{CE sat}$  (~ 0.2 V)

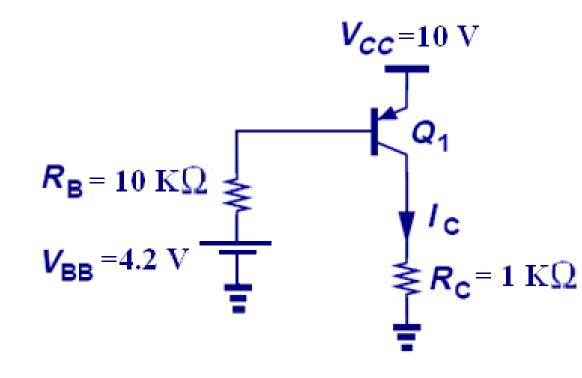

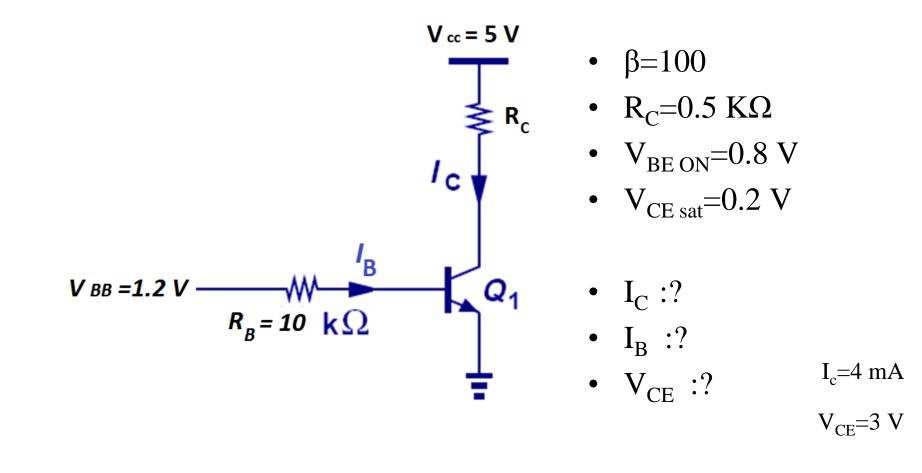

# **Bipolar DC Analysis**

- "dc analysis" or "bias analysis" :

- this step determines:

- The region of operation (active or saturation)

- $(I_E, I_C, I_B)$  and  $V_{CE}$

$$Q \text{ point} : \begin{cases} I_{CQ} \\ V_{CEQ} \end{cases}$$

#### Problem-Solving Technique: Bipolar DC Analysis

- 1. Assume that the transistor is biased in the forward-active mode in which case  $V_{BE} = V_{BE \text{ (on)}}$ ,  $I_B > 0$ , and  $I_C = \beta I_B$ .

- 2. Analyze the "linear" circuit with this assumption.

- 3. Evaluate the resulting state of the transistor. If the initial assumption is "active mode", and for NPN transistor  $V_{CE} > V_{CE \text{ sat}}$  is true(for PNP transistor,  $V_{EC} > V_{EC \text{ sat}}$ ), then the initial assumption is correct. However, if the calculation shows  $I_B < 0$ , then the transistor is probably "cut off", and if the calculation shows for NPN transistor  $V_{CE} < V_{CE \text{ sat}}$  (for PNP transistor,  $V_{EC} < V_{EC \text{ sat}}$ ), the transistor is likely biased in "saturation".

- 4. If the initial assumption is proven incorrect, then a new assumption must be made and the new "linear" circuit must be analyzed. Step 3 must then be repeated.

# **Example 1: PNP Transistor**

- $\beta = 10$  •

- $V_{EB\ ON} {=} 0.8\ V$   $\bullet$

- $V_{\text{EC sat}}=0.2 \text{ V}$

- $I_C :? \bullet$  $I_B :? \bullet$

- $V_{EC}$  :? •

$I_c = 5 \text{ mA}$

، الکترونیک (

$V_{EC}=5 V$

If  $R_C = 3 K\Omega$ ;  $I_C$ ,  $I_B$ ,  $V_{EC}$  :? • b)  $V_{EC}=0.2 V$ b)  $I_c = 3.3 \text{ mAs1}$

# **Example 2: NPN Transistor**

الکترونیک ۱

If

$$R_C = 2 \text{ K}\Omega$$

;  $I_C$ ,  $I_B$ ,  $V_{CE}$  :? • b)  $V_{CE} = 0.2 \text{ V}$

b)  $I_c = 2.4 \text{ m} \text{ }^{2}$

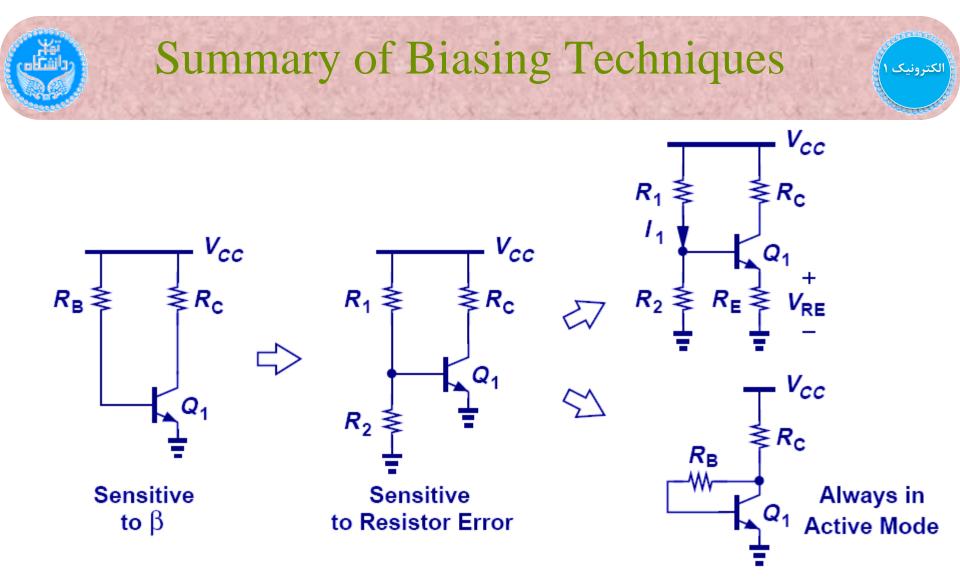

#### **PNP** Biasing Techniques

• Same principles that apply to NPN biasing also apply to PNP biasing with only polarity modifications.

#### **Cutoff Region**

Cutoff represents the off mode in switching applications. :open switch (one of the two states requires for binary logic circuits.)

BVCBO VCB

$$I_{C} = \alpha I_{E} + I_{CBO}$$

$$I_{C} = \beta I_{B} + (\beta + 1) I_{CBO}$$

$$\stackrel{I_{C}}{\longleftarrow} \stackrel{\text{Forward-active mode}}{\underset{i_{E} = I_{E1}}{\underset{i_{E} = I_{E2}}{}}}$$

$$\stackrel{I_{C}=I_{CBO} \quad i_{E} = 0}{\underset{Cut-off Region}{}}$$

For Silicon transistor and around room temperature we have:

# Course Overview

- Semiconductor physics

- PN junction

- BJT

- BJT physics

- dc analysis

- BJT : Small signal analysis

- Amplifiers

- MOSFET

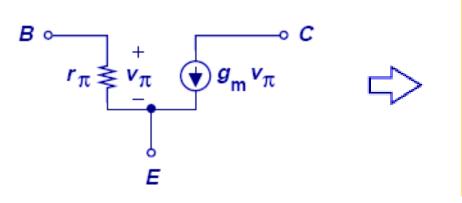

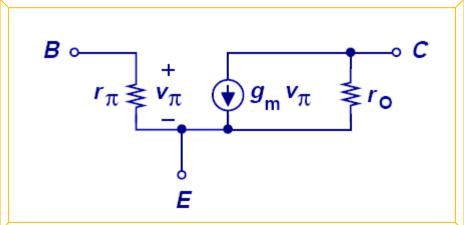

### Small-Signal Model

Small-Signal Model of BJT (Hybrid  $\pi$  Model)

• The small signal model for PNP transistor is exactly IDENTICAL to that of NPN. This is not a mistake because the current direction is taken care of by the polarity of  $V_{BE}$ .

#### Small Signal Model Example I

#### Small Signal Model Example II

• Small-signal model is identical to the previous ones.

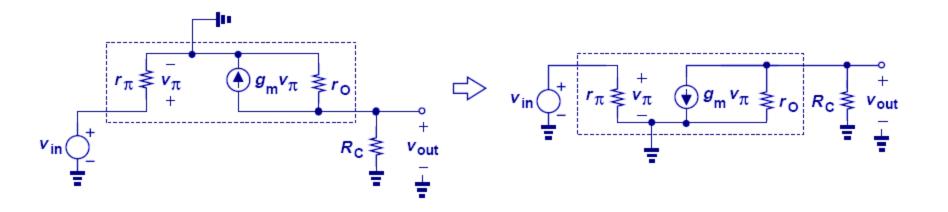

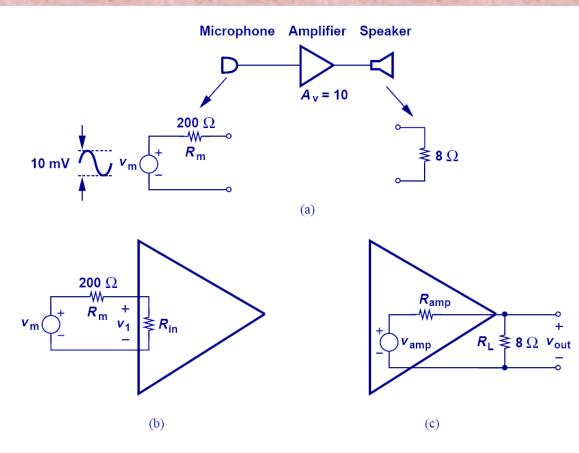

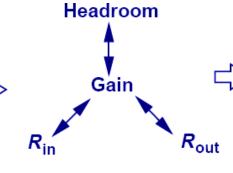

#### Voltage Amplifier

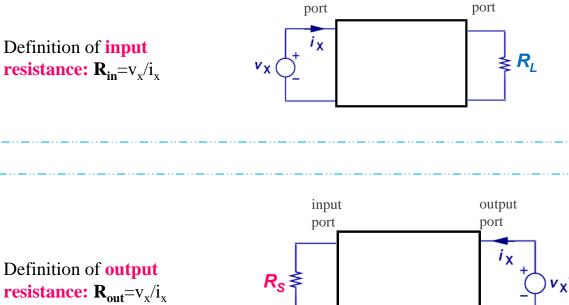

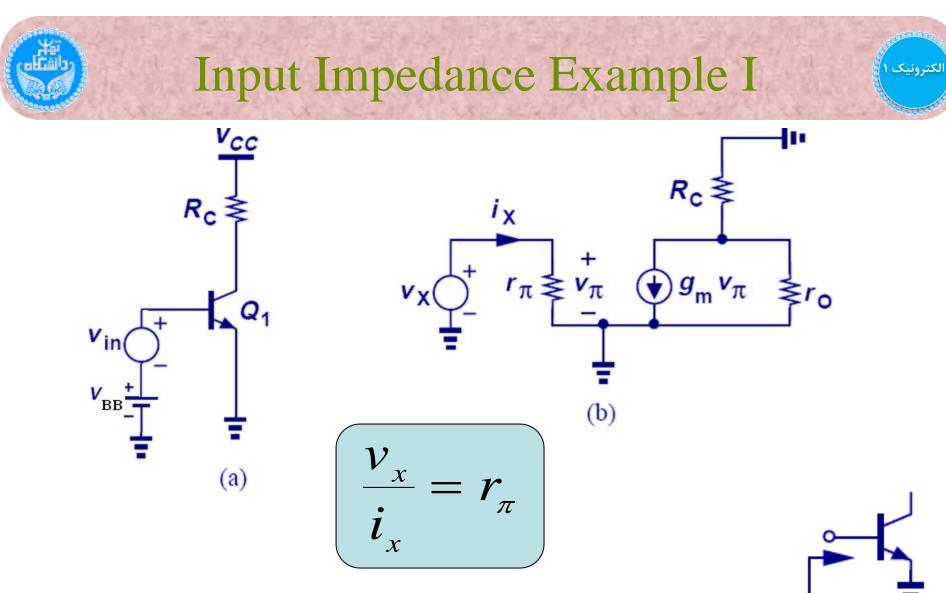

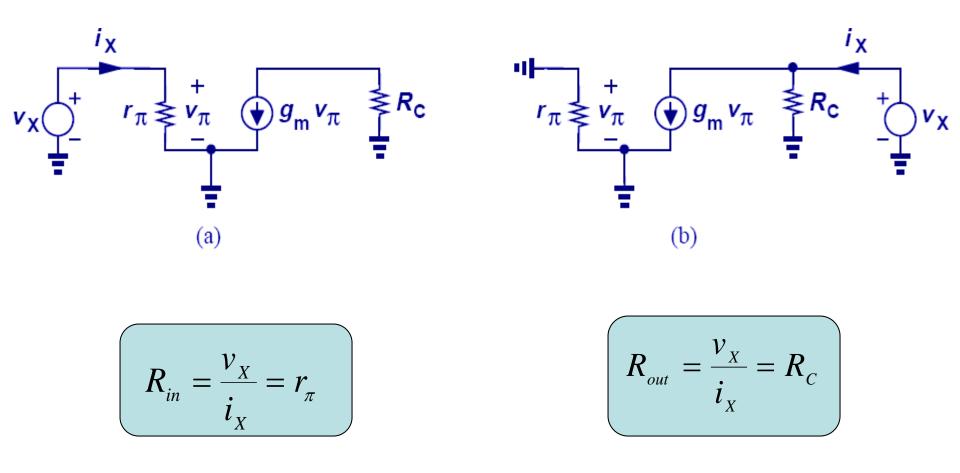

Input (output) impedance is measured between the input (output) nodes of the circuit while all independent sources in the circuit are set to <u>zero</u>.

- In an ideal voltage amplifier, the input impedance is infinite and the output impedance zero.

- But in reality, input or output impedances depart from their ideal values.

#### Input/Output Resistance

input

What is the input and output ٠ resistance for this circuit?

output

Definition of **input** •

•

$R_{x}$

• When calculating input/output impedance, small-signal analysis is assumed.

ac

$r_{\pi}$

#### Impedance at Collector

$V_{\text{in}} \xrightarrow{+}_{a} \xrightarrow{+}_{a}$

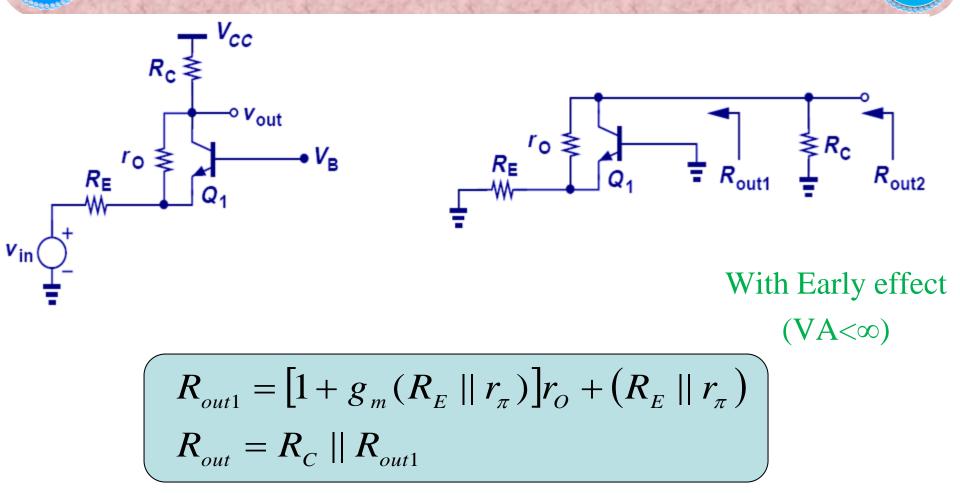

• With Early effect, the impedance seen at the collector is equal to the intrinsic output impedance of the transistor (if emitter is grounded).

ac

ac

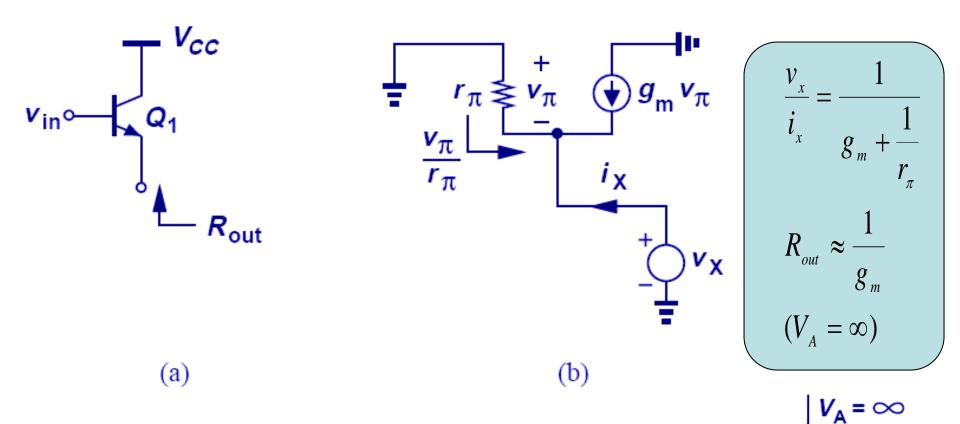

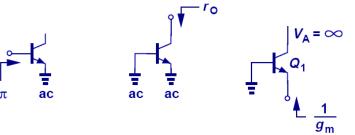

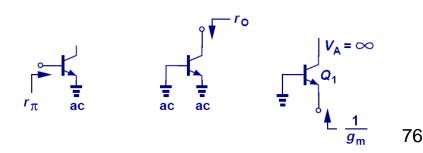

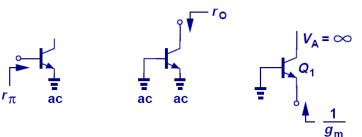

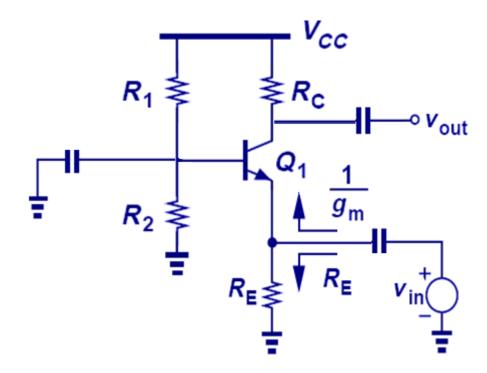

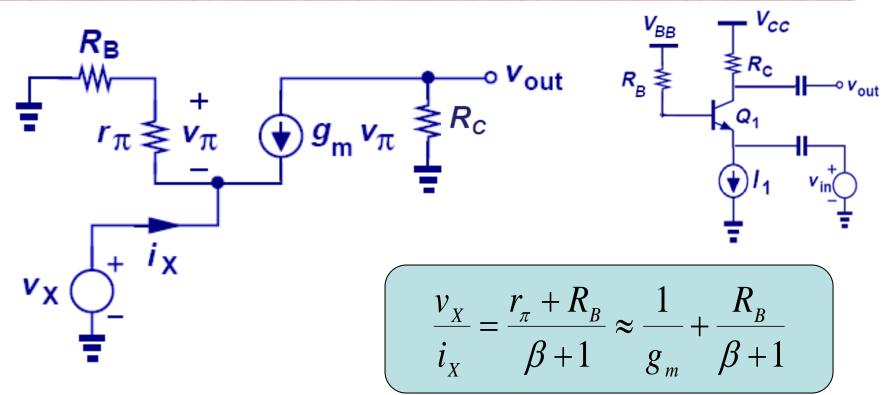

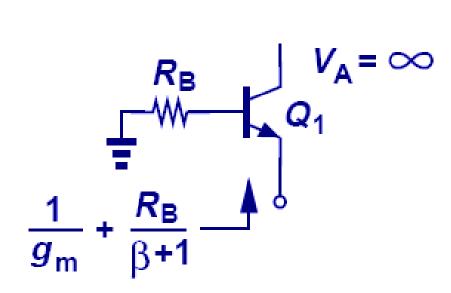

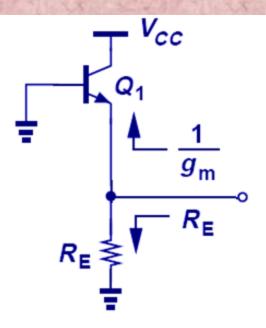

#### Impedance at Emitter

• The impedance seen at the emitter of a transistor is approximately equal to one over its transconductance (if the base is grounded).

$g_{\mathsf{m}}$

Q<sub>1</sub>

ِ الکترونیک ۱

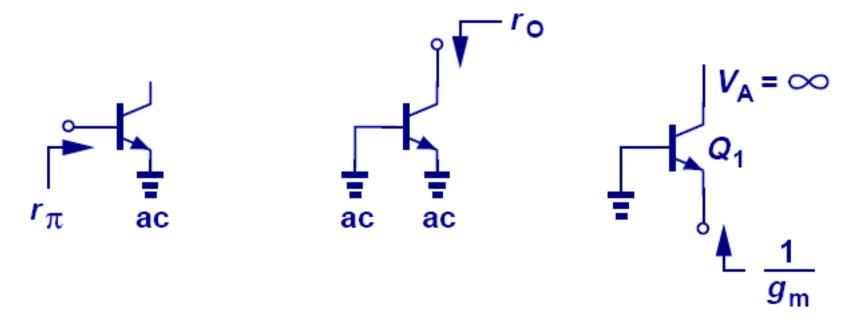

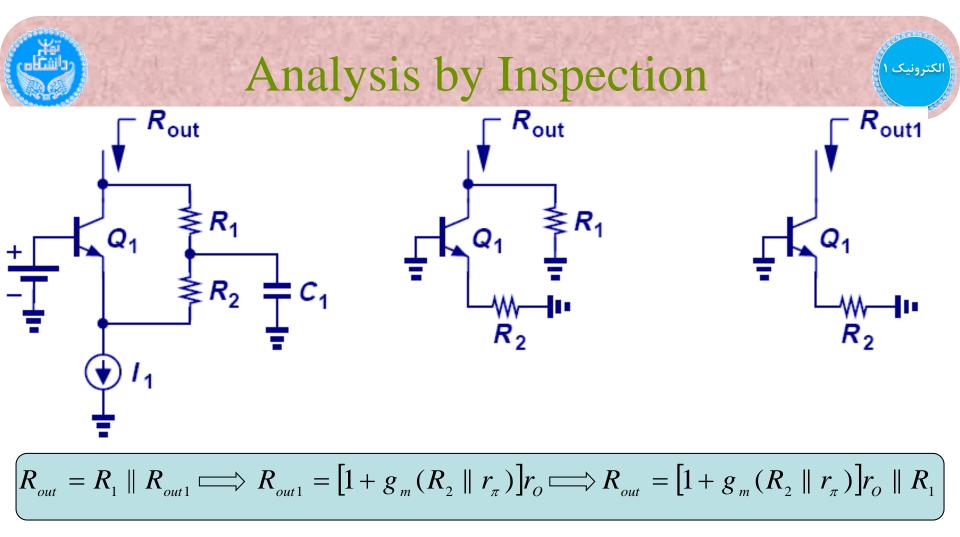

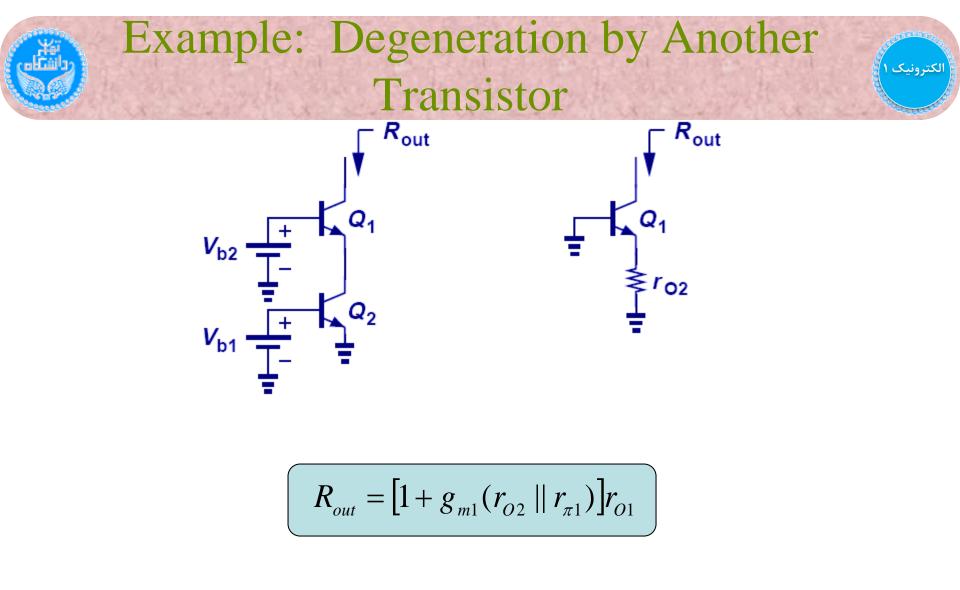

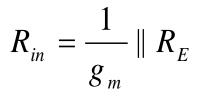

- Rule # 1: looking into the base, the impedance is  $r_{\pi}$  if emitter is (ac) grounded.

- Rule # 2: looking into the collector, the impedance is r<sub>o</sub> if emitter is (ac) grounded.

- Rule # 3: looking into the emitter, the impedance is  $1/g_m$  if base is (ac) grounded and Early effect is neglected.

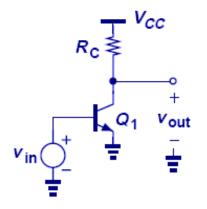

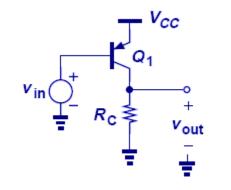

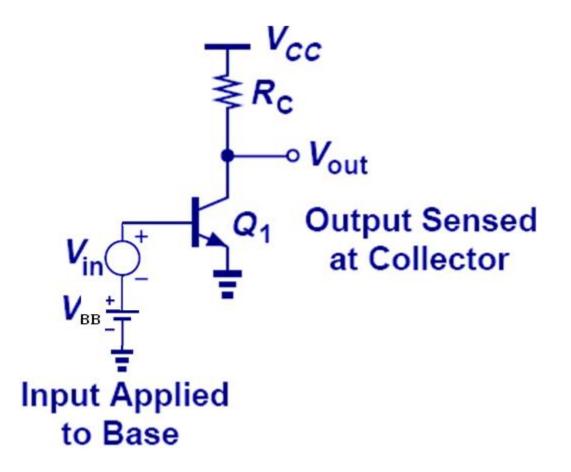

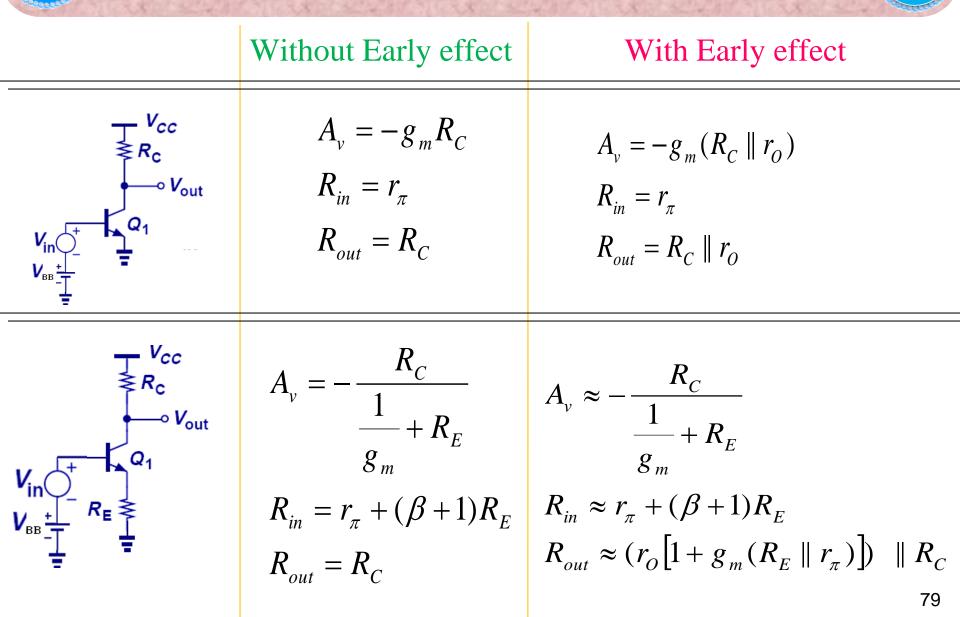

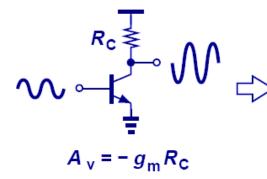

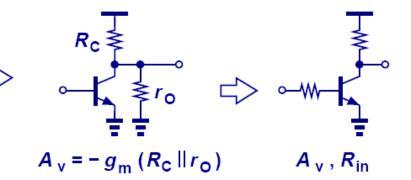

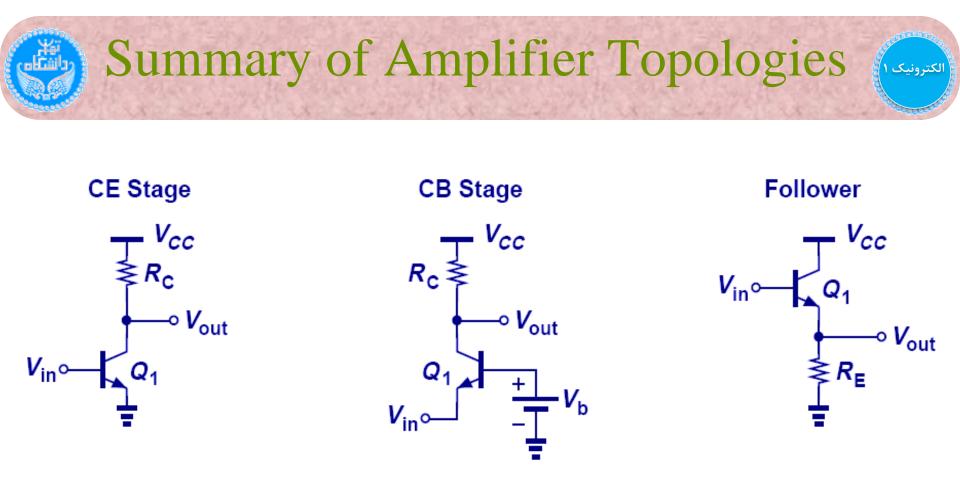

#### **Common-Emitter Topology**

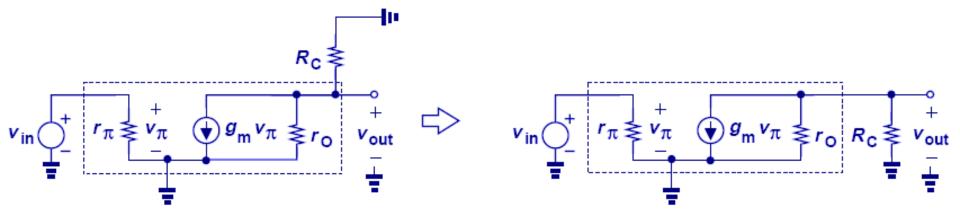

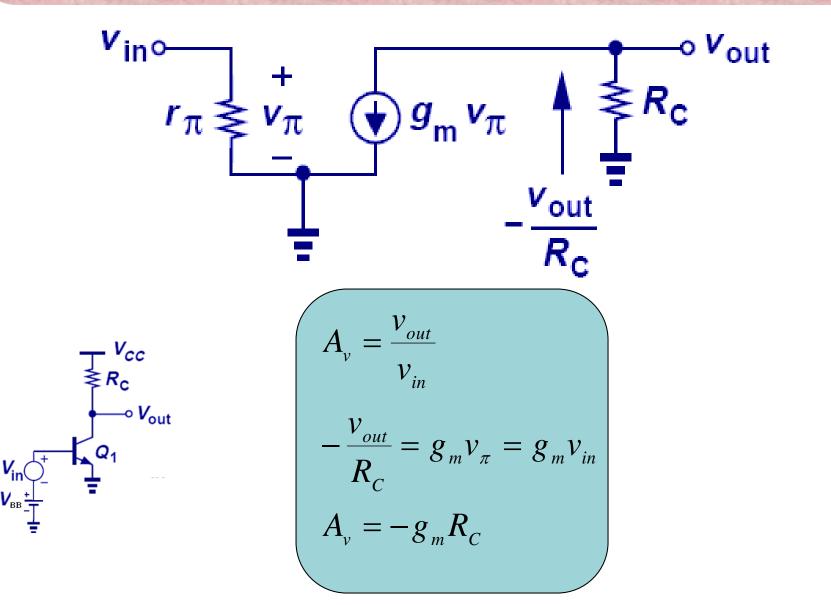

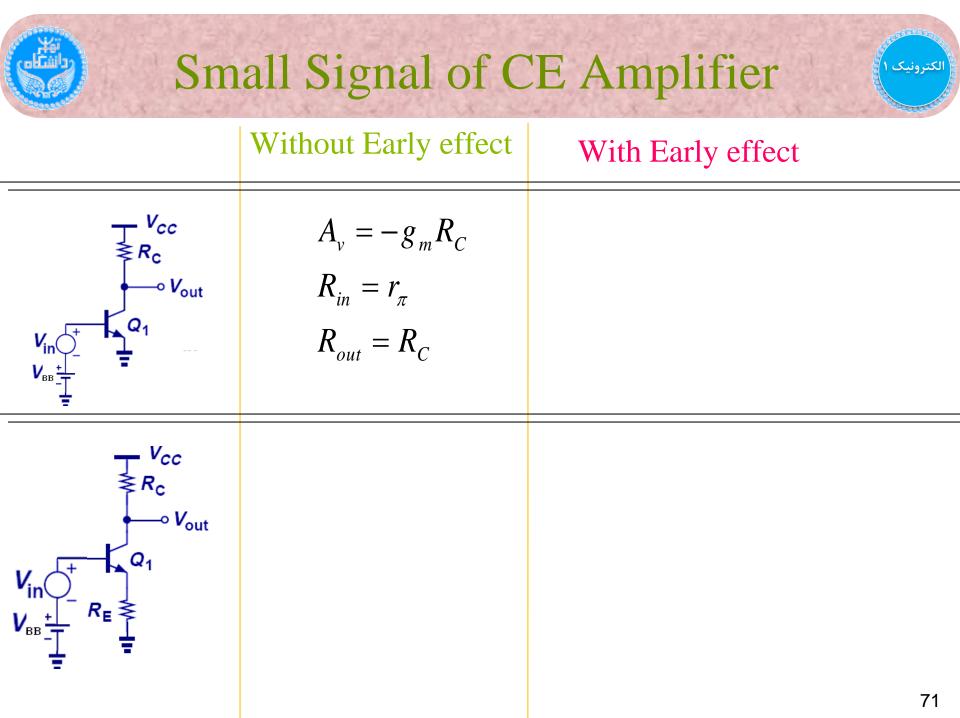

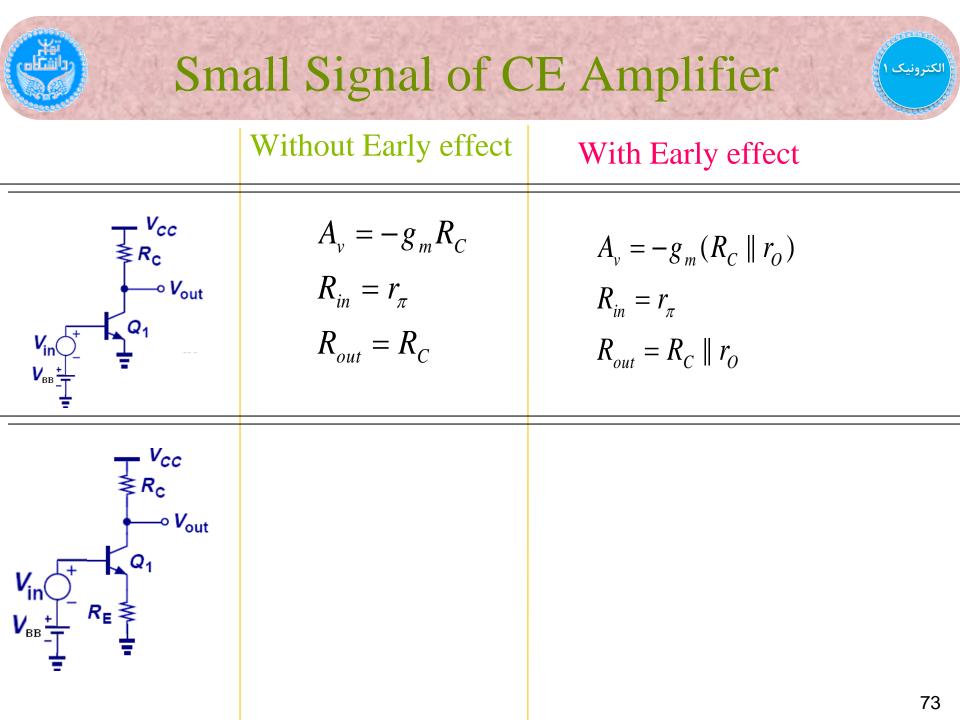

#### Small Signal of CE Amplifier

#### I/O Impedances of CE Stage

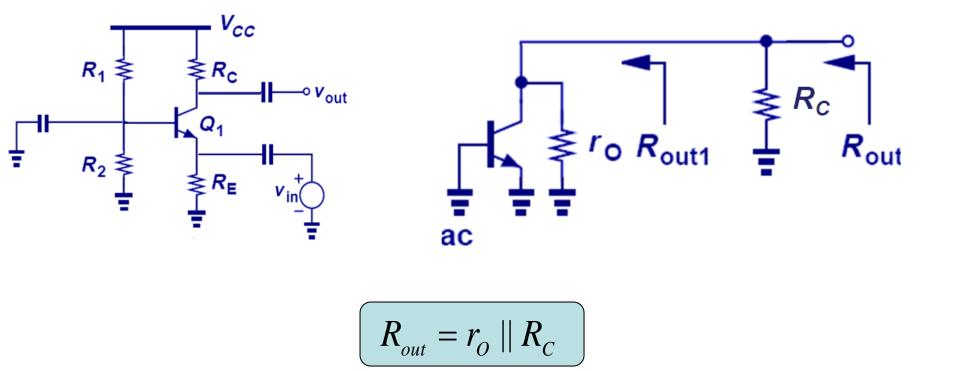

• When measuring output impedance, the input port has to be grounded so that  $V_{in} = 0$ .

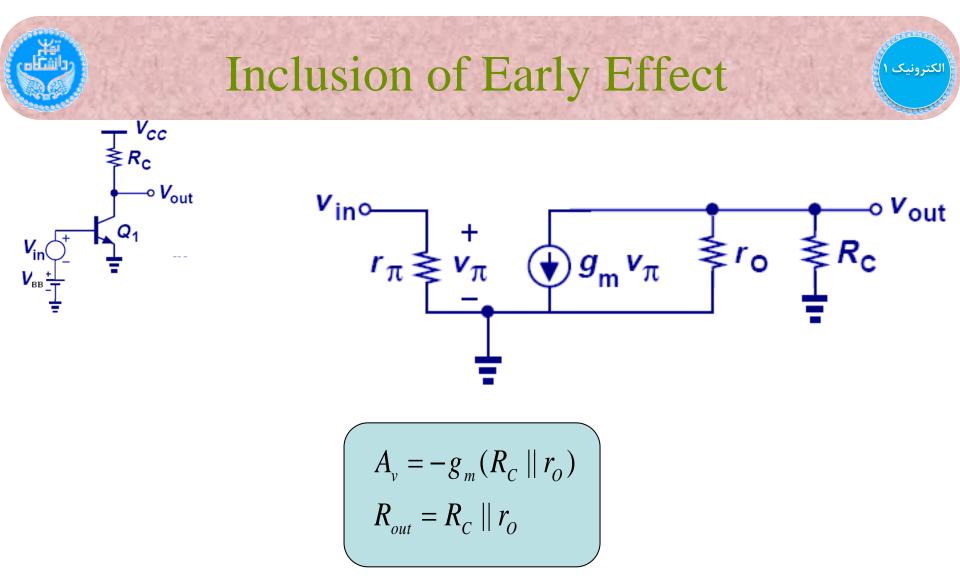

• Early effect will lower the gain of the CE amplifier, as it appears in parallel with  $R_c$ .

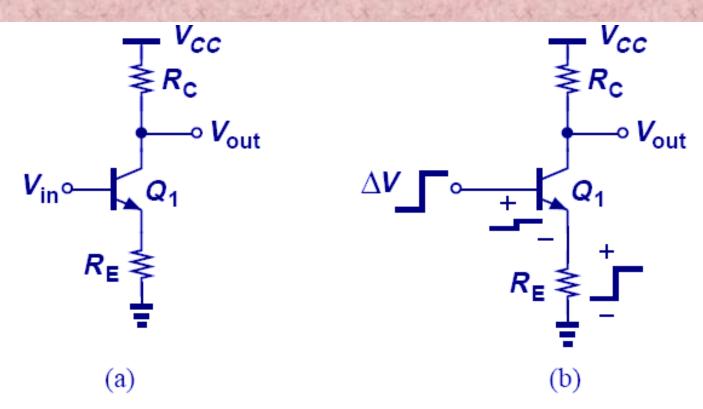

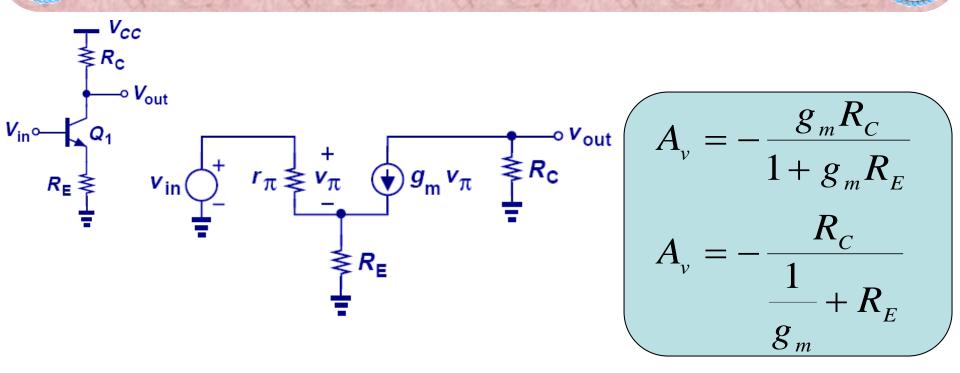

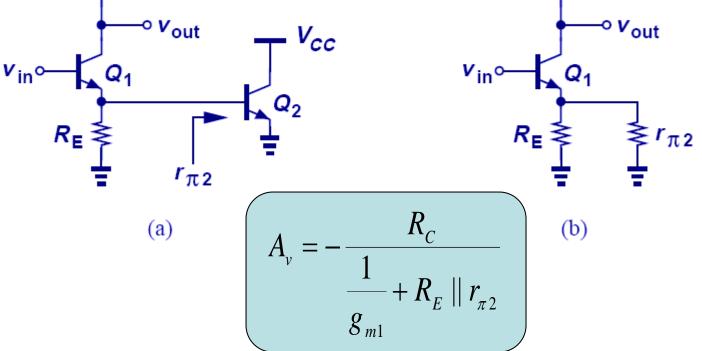

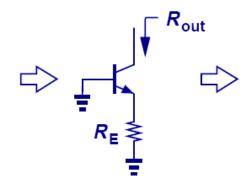

#### **Emitter Degeneration**

- By inserting a resistor in series with the emitter, we "degenerate" the CE stage.

- This topology will decrease the gain of the amplifier but improve other aspects, such as linearity, and input impedance.

#### **Emitter Degeneration**

• Interestingly, this gain is equal to the total load resistance to ground divided by  $1/g_m$  plus the total resistance placed in series with the emitter.

لكترونيك

75

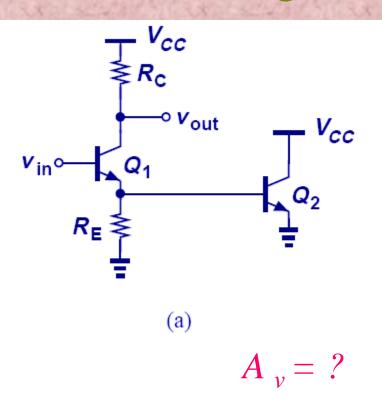

#### **Emitter Degeneration Example**

• The input impedance of  $Q_2$  can be combined in parallel with  $R_E$  to yield an equivalent impedance that degenerates  $Q_1$ .

#### **Emitter Degeneration Example**

$V_{cc}$  $R_{c}$  $v_{in} \circ V_{out}$

• The input impedance of  $Q_2$  can be combined in parallel with  $R_E$  to yield an equivalent impedance that degenerates  $Q_1$ .

V<sub>cc</sub>

R<sub>c</sub>

77

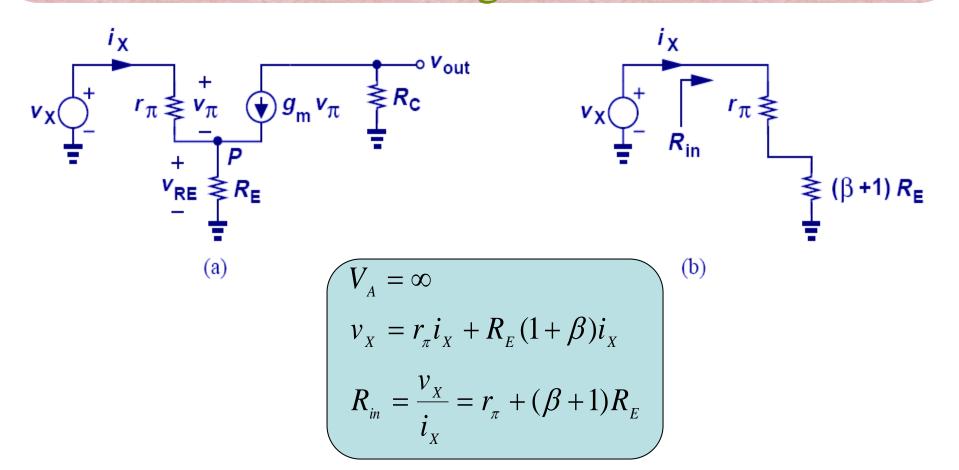

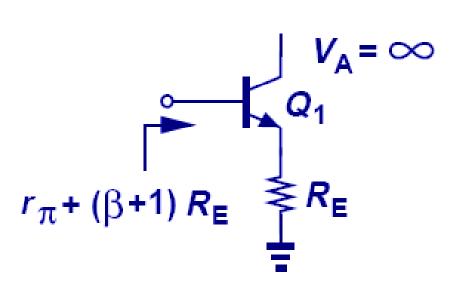

#### Input Impedance of Degenerated CE Stage

• With emitter degeneration, the input impedance is increased from  $r_{\pi}$  to  $r_{\pi} + (\beta+1)R_{E}$ ; a desirable effect.

### Small Signal of CE Amplifier

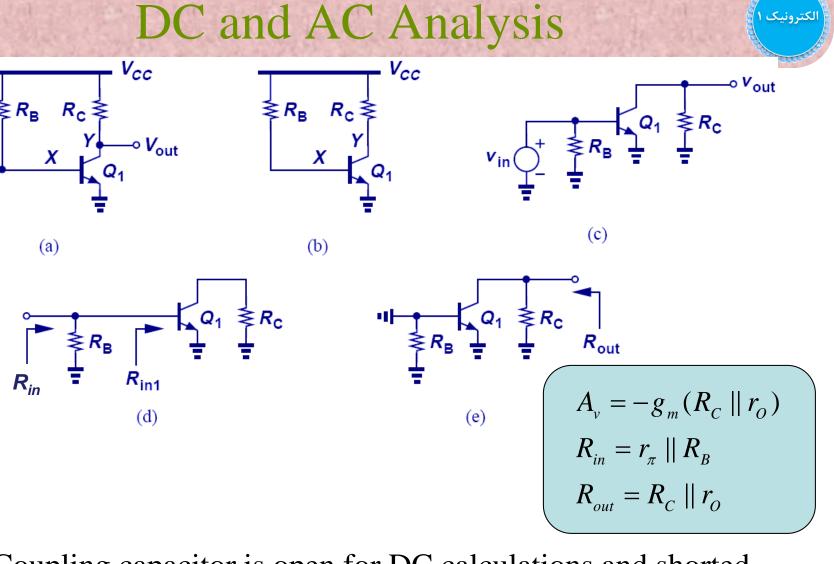

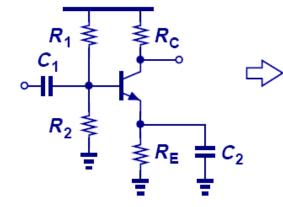

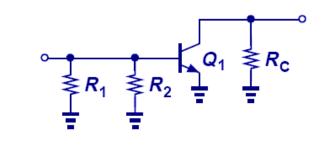

• This seemingly complicated circuit can be greatly simplified by first recognizing that the capacitor creates an AC short to ground, and gradually transforming the circuit to a known topology.

• Called a "cascode", the circuit offers many advantages..

#### **Bad Input Connection**

• Since the microphone has a very low resistance that connects from the base of  $Q_1$  to ground, it attenuates the base voltage and renders  $Q_1$  without a bias current.

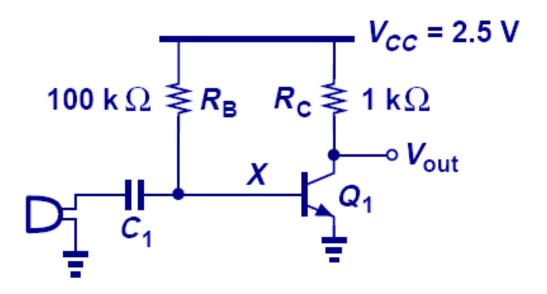

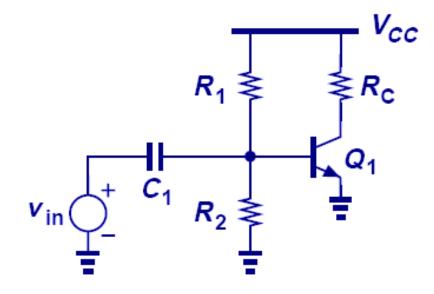

#### Use of Coupling Capacitor

• Capacitor isolates the bias network from the microphone at DC but shorts the microphone to the amplifier at higher frequencies.

Coupling capacitor is open for DC calculations and shorted ulletfor AC calculations.

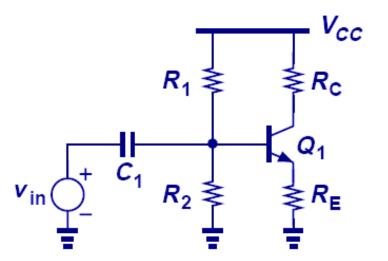

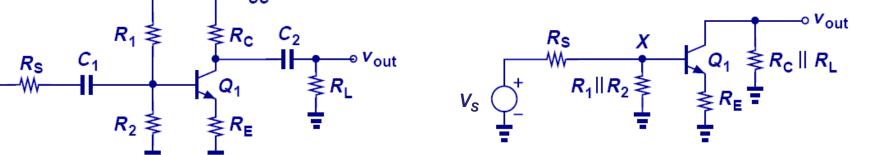

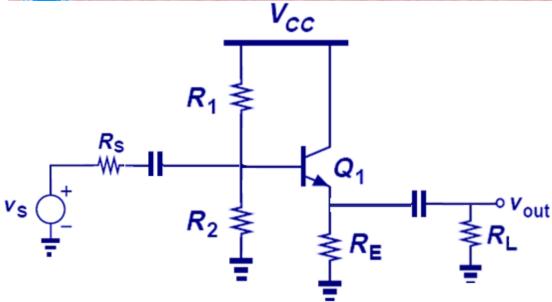

#### CE Stage with Biasing

$V_{cc}$   $R_{1} \stackrel{\swarrow}{\underset{=}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}{\overset{\sim}}}$

$$\begin{pmatrix} A_v = -g_m (R_C \parallel r_O) \\ R_{in} = r_\pi \parallel R_1 \parallel R_2 \\ R_{out} = R_C \parallel r_O \end{pmatrix}$$

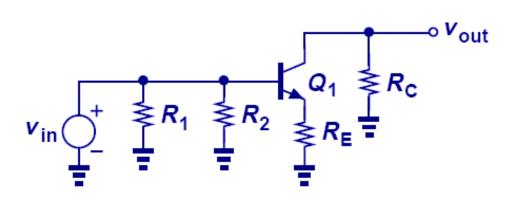

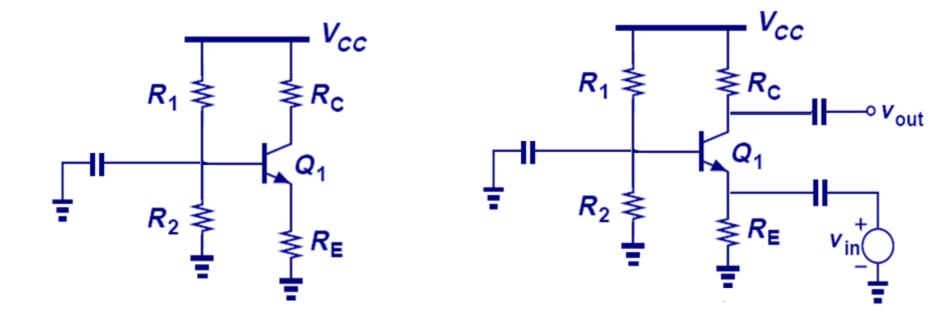

#### CE Stage with Robust Biasing

$$A_{v} = \frac{-R_{C}}{\frac{1}{g_{m}} + R_{E}}$$

$$R_{in} = [r_{\pi} + (\beta + 1)R_{E}] \parallel R_{1} \parallel R_{2}$$

$$R_{out} = R_{C}$$

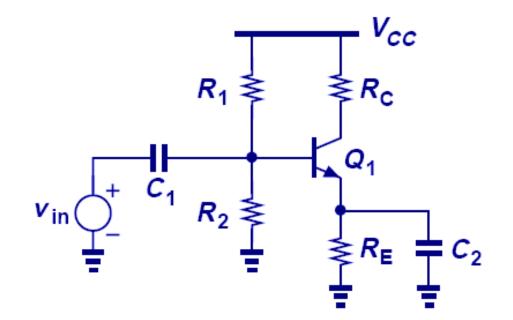

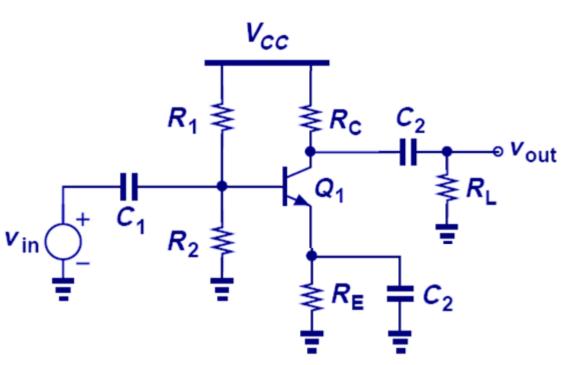

# Removal of Degeneration for Signals at AC

$$A_{v} = -g_{m}R_{C}$$

$$R_{in} = r_{\pi} \parallel R_{1} \parallel R_{2}$$

$$R_{out} = R_{C}$$

• Capacitor shorts out  $R_E$  at higher frequencies and removes degeneration.

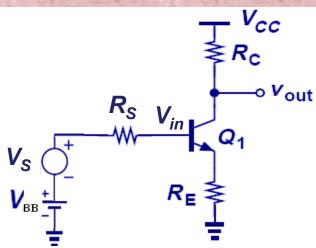

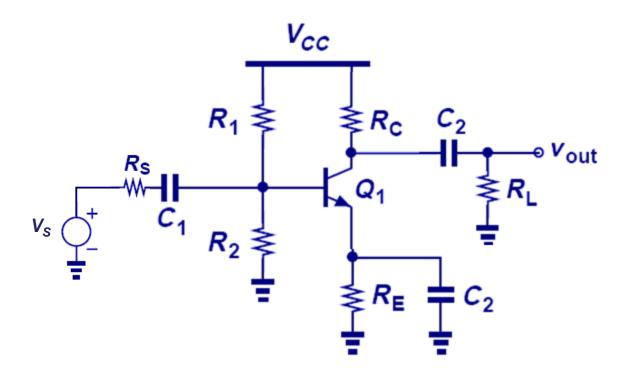

#### Source Resistance

ac:

V

$\frac{v_{out}}{v_s} = \frac{v_{in}}{v_s} \cdot \frac{v_{out}}{v_{in}}$

$\frac{v_{in}}{v_s} = \frac{R_{in}}{R_{in} + R_s}$

$$\begin{aligned} R_{in} &= r_{\pi} + (\beta + 1)R_E \\ R_{out} &= R_C \end{aligned}$$

$R_s V_{in}$ r<sub>π</sub>≹ R<sub>in</sub> ≰ (β +1) R<sub>E</sub>

$$V_{A} = \infty$$

$$\frac{V_{out}}{v_{s}} = \frac{V_{in}}{v_{s}} \cdot \frac{V_{out}}{v_{in}}$$

$$\frac{V_{out}}{v_{s}} = \frac{-\beta R_{C}}{r_{\pi} + (\beta + 1)R_{E} + R_{S}}$$

$$A_{v} = \frac{V_{out}}{v_{s}} \approx \frac{-R_{C}}{\frac{1}{g_{m}} + R_{E} + \frac{R_{S}}{\beta + 1}}$$

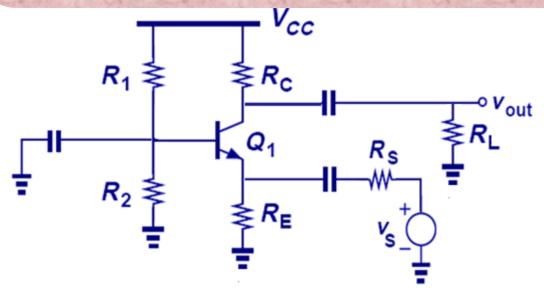

#### **Complete CE Stage**

$$R_{in} = [r_{\pi} + (\beta + 1)R_E] \parallel R_1 \parallel R_2 \qquad \qquad A_{\nu} = \frac{R_{in}}{R_{in} + R_S} \times \frac{-R_C \parallel R_L}{\frac{1}{g_m} + R_E}$$

$$R_{out} = R_C$$

The input signal source exhibits a finite resistance  $R_s$  and the output is tied to a load R<sub>L</sub>.

- A transistor is biased at a collector current of 1 mA. Determine the small-signal parameters if

- β=100

- V<sub>A</sub>=10 V

- β=100

- $V_{CC}=1.4V$

- $I_{CQ}=1 \text{ mA}$

- R<sub>C</sub>=0.5K Ω

- $R_1 = R_2 = 100 \text{ K} \Omega$

- V<sub>A</sub>=10 V

- $R_{in}, R_{out}, A_V$ :?

. الکترونیک

- β=100

- V<sub>BE ON</sub>=0.7 V

- V<sub>CC</sub>=5.4 V

- $R_1 = R_2 = 200 \text{ K } \Omega$

الکترونیک ۱

- $R_E = 1 K \Omega$

- R<sub>C</sub>=0.5K Ω

- R<sub>L</sub>=10K Ω

- V<sub>A</sub>=15V

- $R_{in}, R_{out}, A_V$ :?

- If  $R_S = 100 \Omega$ ,  $R_{in}$ ,  $R_{out}$ ,  $A_V$ :?

- β=100

- V<sub>BE ON</sub>=0.7 V

- V<sub>CC</sub>=5.4 V

- $R_1 = R_2 = 200 \text{ K } \Omega$

- $R_E = 1 K \Omega$

- R<sub>C</sub>=0.5K Ω

- $R_L = 10K \Omega$

- V<sub>A</sub>=15V

- $R_{in}, R_{out}, A_V$ ?

- If  $R_S = 100 \Omega$ ,  $R_{in}$ ,  $R_{out}$ ,  $A_V$ :?

- Max Vs : Q1:active

#### Summary of CE Concepts

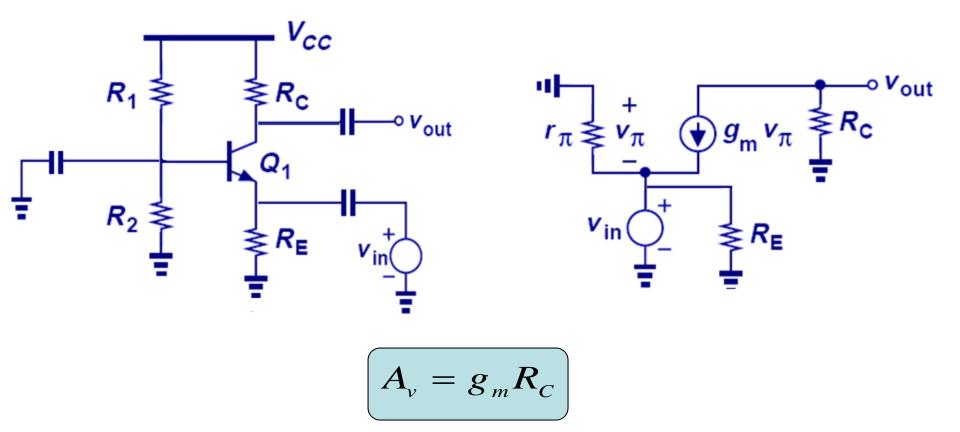

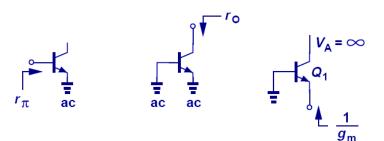

# Common Base (CB) Amplifier

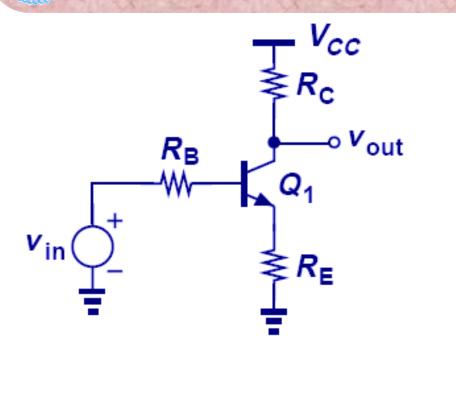

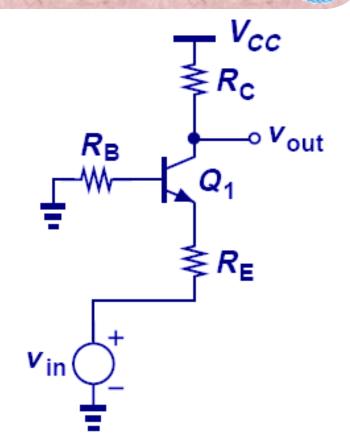

• In common base topology, where the base terminal is biased with a fixed voltage, emitter is fed with a signal, and collector is the output.

الکترونیک ۱

# A<sub>V</sub> for CB Stage

• The voltage gain of CB stage is  $g_m R_C$ , which is identical to that of CE stage in magnitude and opposite in phase.

#### Input Impedance for CB Stage

97

# Output Impedance of CB Stage

• The output impedance of CB stage is similar to that of CE stage.

# Realistic Output Impedance of CB Stage (العربيد)

• The output impedance of CB stage is equal to  $R_C$  in parallel with the impedance looking down into the collector.

#### 10

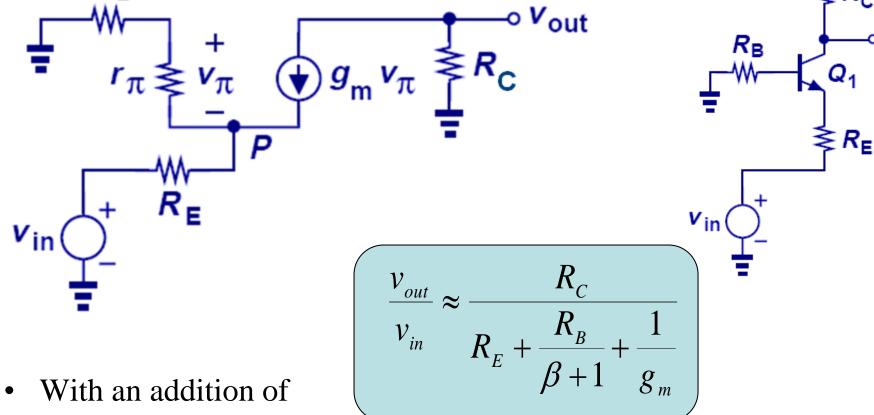

A<sub>v</sub> of CB with Base Resistance

base resistance, the voltage gain degrades.

CH5 Bipolar Amplifiers

Without Early effect

$(VA \rightarrow \infty)$

الكترونيك

V<sub>cc</sub>

Vout

Rв

#### Comparison of CE and CB Stages with Base Resistance

• The voltage gain of CB amplifier with base resistance is exactly the same as that of CE stage with base resistance and emitter degeneration, except for a negative sign.

CH5 Bipolar Amplifiers

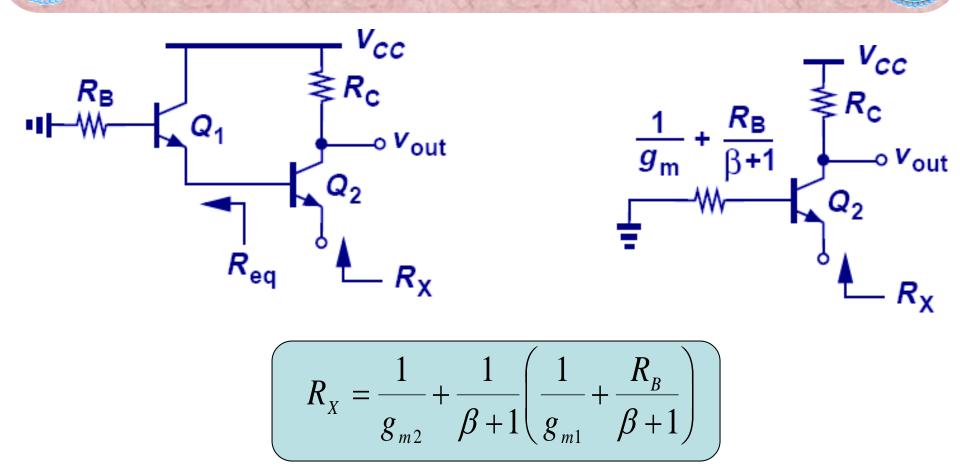

#### Input Impedance of CB Stage with Base Resistance

• The input impedance of CB with base resistance is equal to  $1/g_m$ plus R<sub>B</sub> divided by ( $\beta$ +1). This is in contrast to degenerated CE stage, in which the resistance in series with the emitter is *multiplied* by ( $\beta$ +1) when seen from the base. Without Early effect

$(VA \rightarrow \infty)$  10

## Input Impedance Seen at Emitter and Base

#### Input Impedance Example

• To find the  $R_X$ , we have to first find  $R_{eq}$ , treat it as the base resistance of  $Q_2$  and divide it by ( $\beta$ +1).

$$I_{C} = 4.8 \, mA \Longrightarrow V_{CEQ} = 12 - 2 \times 4.8 = 1.7 > 0.2 \, V \Longrightarrow active$$

$$g_{m} = 192 \, mS \Longrightarrow \frac{1}{g_{m}} = 5.1 \,\Omega$$

$$R_{in} = \frac{1}{g_{m}} \parallel R_{E} \approx 5.1 \,\Omega$$

$$R_{out} \approx R_{C} = 1 K \Omega$$

$$A_{v} = g_{m} R_{c \ total} = g_{m} (R_{c} \parallel R_{L}) \approx 96$$

$$A_{Vs} = \frac{R_{in}}{R_{in} + R_{s}} \times A_{V} \approx 32$$

$$A_{I} = \frac{R_{in} + R_{s}}{R_{L}} A_{Vs} = 0.48$$

- $\beta = 100$

- V<sub>BE ON</sub>=0.7 V

- V<sub>CE sat</sub>=0.2 V

- V<sub>CC</sub>=12 V

- $R_1 = R_2 = 20 \text{ K } \Omega$

- $R_E = 1 \text{ K}\Omega$

- $R_C=1 \text{ K } \Omega$

- $R_L=1K \Omega$

- $R_s=10 \Omega$

- $R_{in}, R_{out}, A_V, A_{Vs}, A_I$ ?

## Course Overview

- Semiconductor physics

- PN junction

- BJT

- BJT physics

- dc analysis

- ac/dc load lines

- Stability

- BJT : Small signal analysis

- CE amplifier

- CE amplifier

- CC stage (emitter follower)

• MOSFET

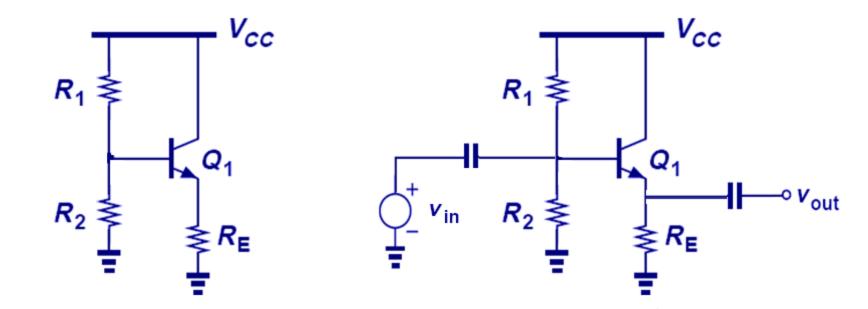

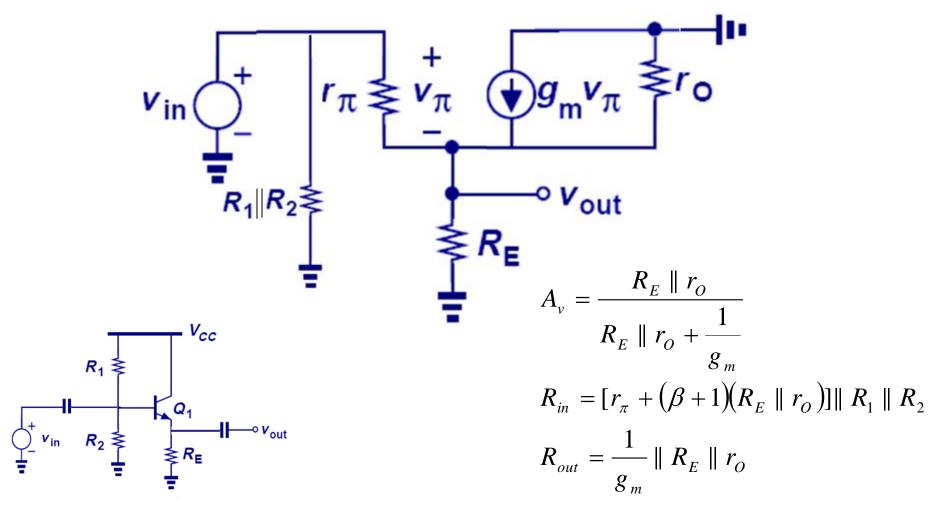

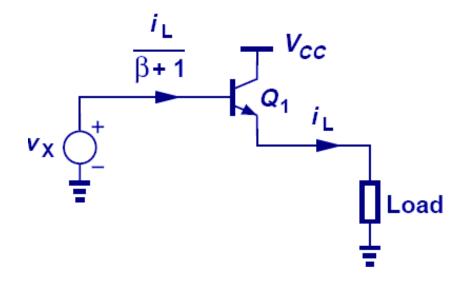

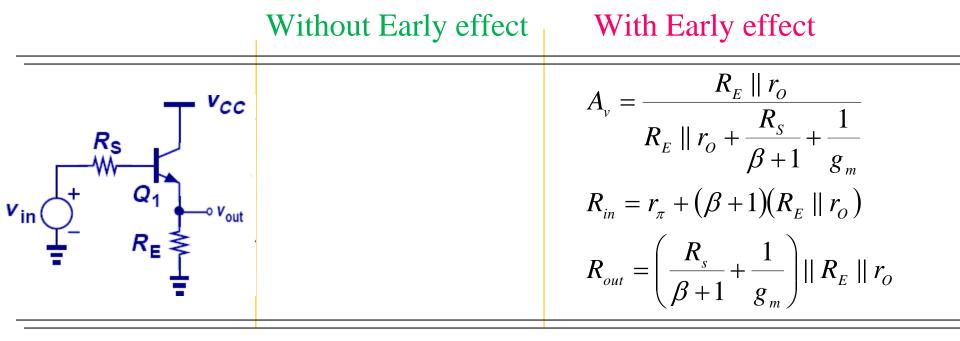

#### Emitter Follower (Common Collector Amplifier)

الکترونيک ۱

# Small Signal Model of CE

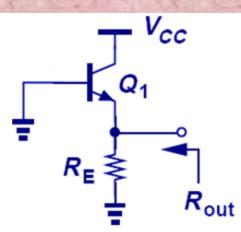

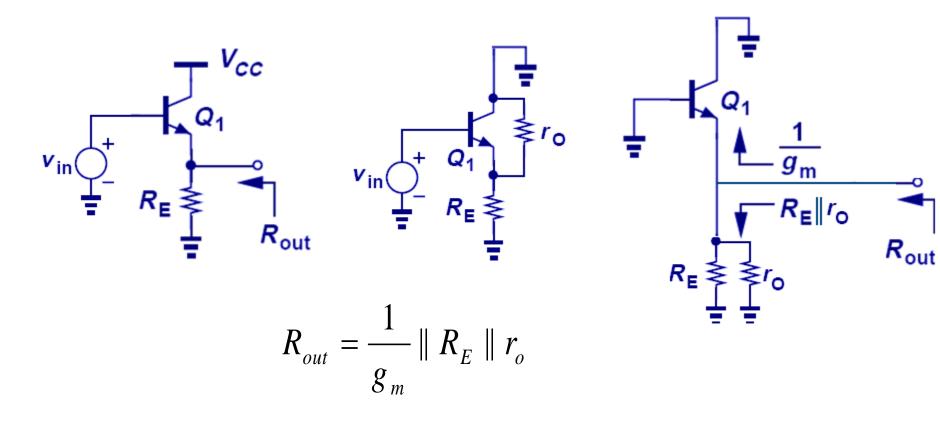

### **Output Impedance of Emitter Follower**

$$R_{out} = \frac{1}{g_m} \parallel R_E$$

(neglecting  $r_0$ )

# Output Impedance of Emitter Follower (with Early effect)

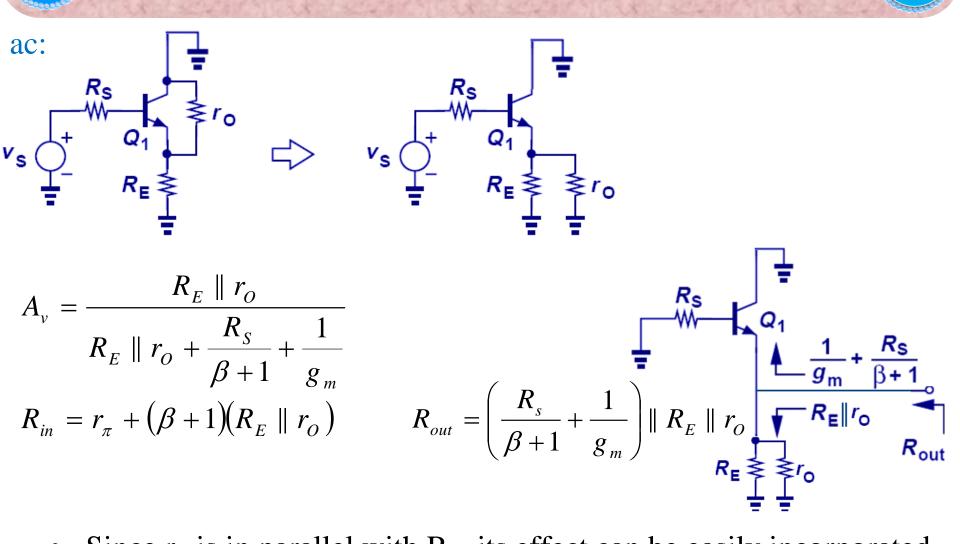

# تسربيك Emitter Follower with Source Resistance

Since r<sub>o</sub> is in parallel with R<sub>E</sub>, its effect can be easily incorporated into voltage gain and input and output impedance equations.

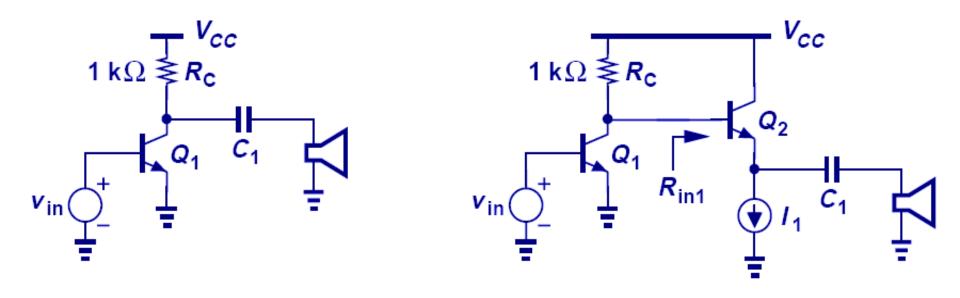

#### Emitter Follower as Buffer

• Since the emitter follower increases the load resistance to a much higher value, it is suited as a buffer between a CE stage and a heavy load resistance to alleviate the problem of gain degradation.

- There is a current gain of  $(\beta+1)$  from base to emitter.

- Effectively speaking, the load resistance is multiplied by (β+1) as seen from the base.

### Example

$$R_{in} = [r_{\pi} + (\beta + 1)(R_E || R_L)] || R_1 || R_2 = 60.2 \ K\Omega$$

$$R_{out} = (\frac{1}{g_m} + \frac{R_1 || R_2 || R_s}{\beta + 1}) || R_E \approx 11.9 \Omega$$

$$A_{\nu} = \frac{R_E || R_L}{R_E || R_L + \frac{1}{g_m}} \approx 0.98$$

$$A_{\nu s} = \frac{R_{in}}{R_{in} + R_s} A_{\nu} \approx 0.978$$

- $\beta = 50$

- V<sub>BE ON</sub>=0.7 V

- V<sub>CE sat</sub>=0.2 V

- $V_{CC} = 5 V$

- $R_1 || R_2 = 500 \text{ K } \Omega$

- $R_E = 1 K\Omega$

- $R_L = 2 K\Omega$

- $R_s = 100 \Omega$

- r<sub>π</sub>=1.1 KΩ

•

$$R_{in}, R_{out}, A_V, A_I$$

:?

. الکترونیک ۱

- The three amplifier topologies studied so far have different properties and are used on different occasions.

- CE and CB have voltage gain with magnitude greater than one, while follower's voltage gain is at most one.

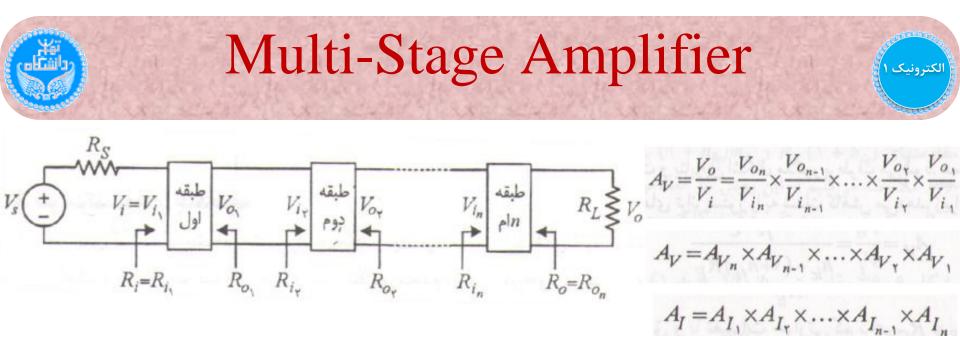

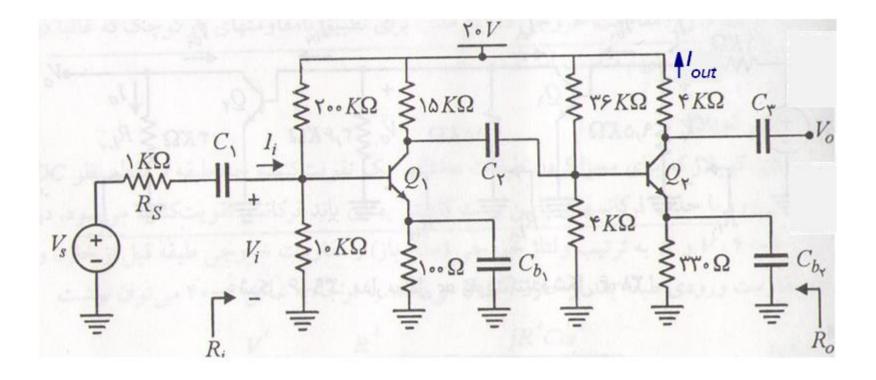

# Multi-Stage Amplifier

•  $\beta = 50$ ,  $r_0 = 40 \text{ k}\Omega$

- $R_{in}, R_{out}, A_V, A_I$ ?

- Max symmetric V<sub>o</sub> swing?

- Max Vs swing?

# Course Overview

- Semiconductor physics

- PN junction

- BJT

- BJT : Small signal analysis

- **MOSFET** ← Chapter 6 : Physics of MOS Transistors

# The MOSFET

- □ No other human artifact has been fabricated in larger numbers ..

- "...some consider it one of the most important technological breakthroughs in human history..." (Wikipedia)

M. Fischetti, 2009

- Conceived ~ 1930

- First successful fabrication: late 1950s

- Mid 1980s: Power problem  $\rightarrow$  low power device  $\rightarrow$ CMOS

- Today *CMOS technology* is the dominant technology in electronics industry.

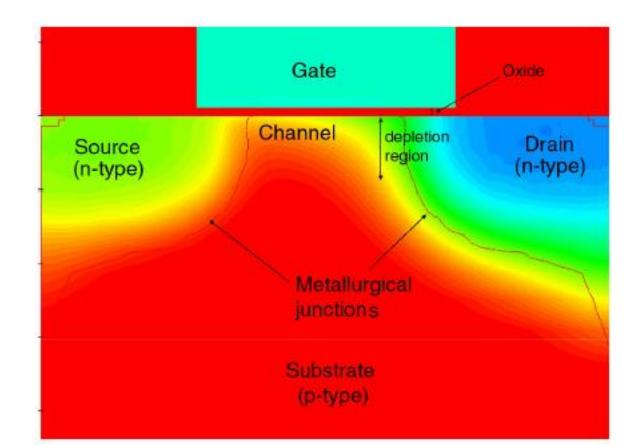

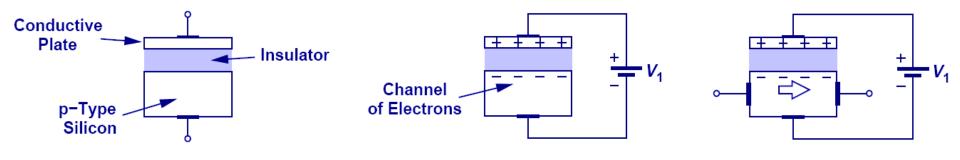

# Metal-Oxide-Semiconductor (MOS) Capacitor

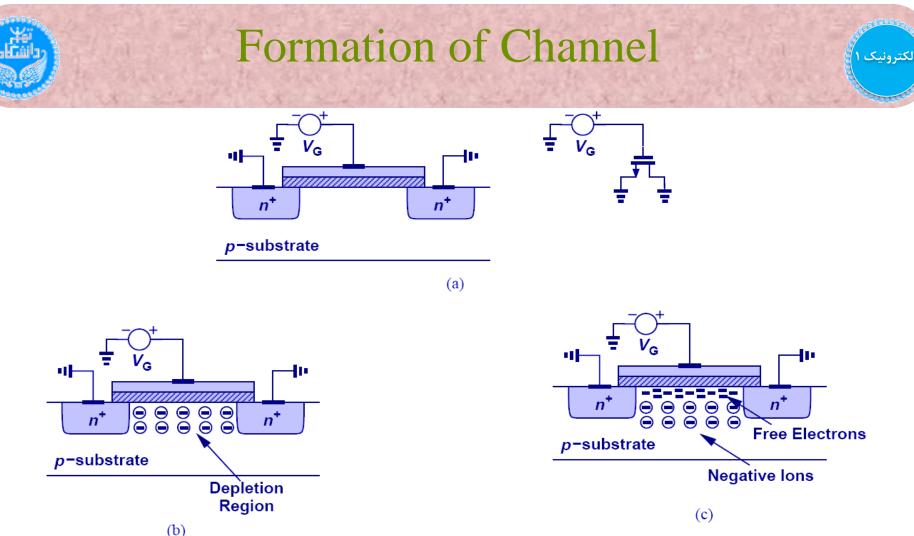

• The MOS structure can be thought of as a parallel-plate capacitor, with the top plate being the positive plate, oxide being the dielectric, and Si substrate being the negative plate. (We are assuming P-substrate.)

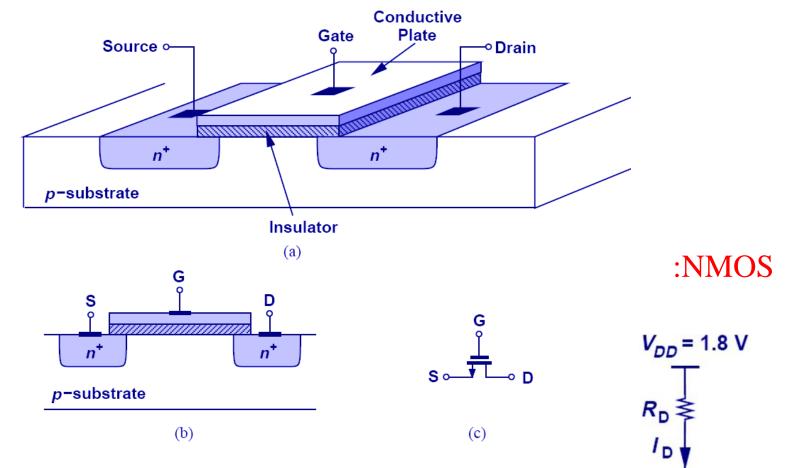

# Structure and Symbol of MOSFET

• This device is symmetric, so either of the n+ regions can be source or drain.

M1

، الکترونیک ۱

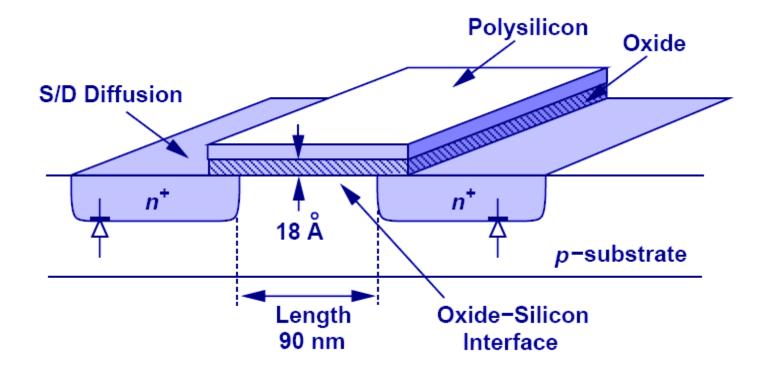

• The gate is formed by polysilicon, and the insulator by Silicon dioxide.

• First, the holes are repelled by the positive gate voltage, leaving behind negative ions and forming a depletion region. Next, electrons are attracted to the interface, creating a channel ("inversion layer").

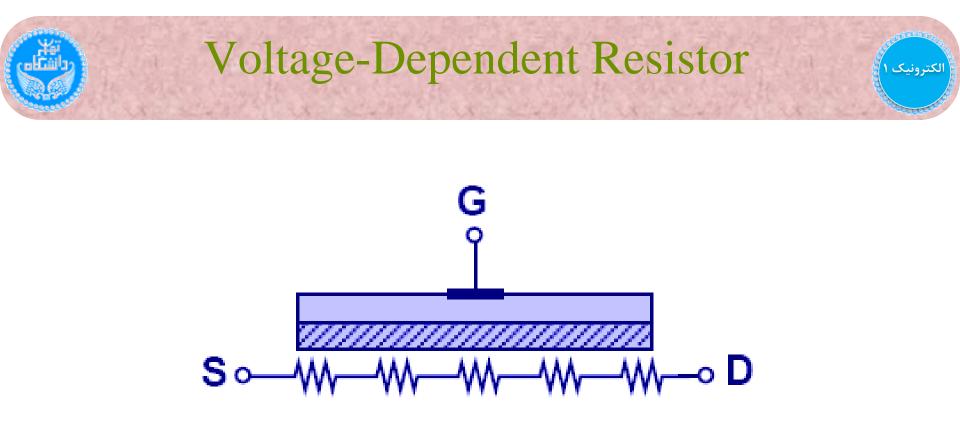

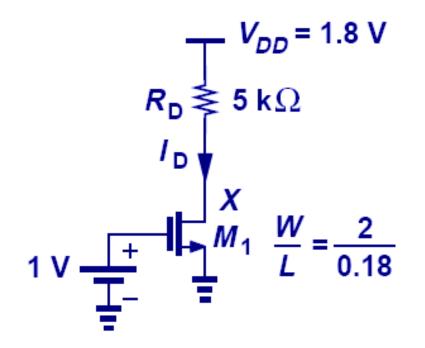

- The inversion channel of a MOSFET can be seen as a resistor.

- Since the charge density inside the channel depends on the gate voltage, this resistance is also voltage-dependent.

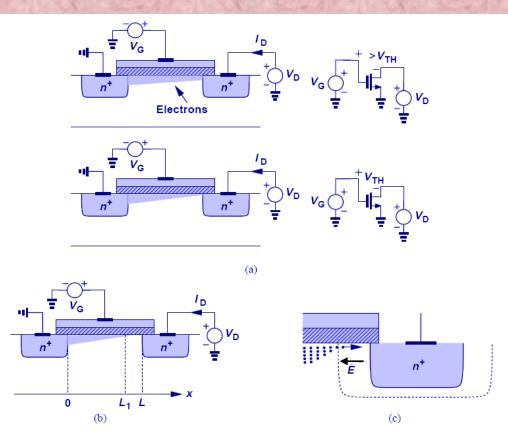

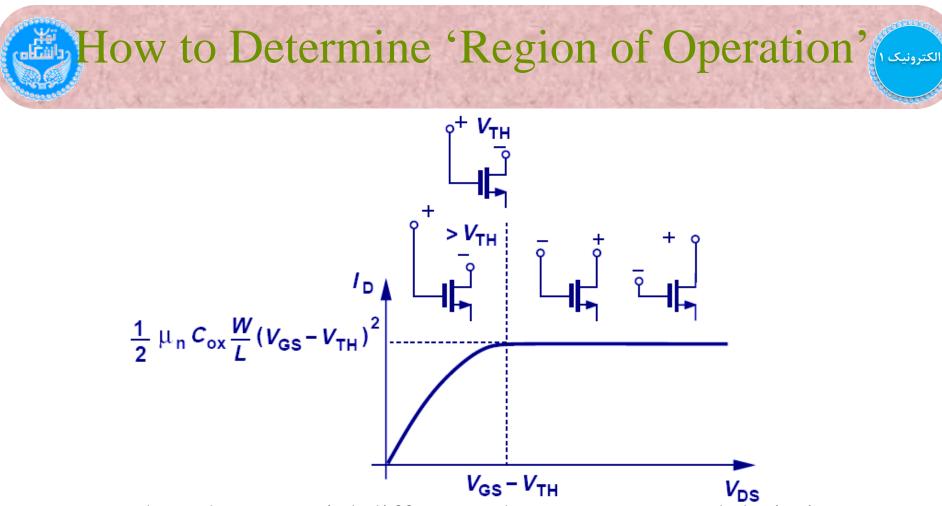

### **Channel Pinch-Off**

- As the potential difference between drain and gate becomes more positive, the inversion layer beneath the interface starts to pinch off around drain.

- When  $V_D V_G = V_{th}$ , the channel at drain totally pinches off, and when  $V_D V_G > V_{th}$ , the channel length starts to decrease.

CH 6 Physics of MOS Transistors

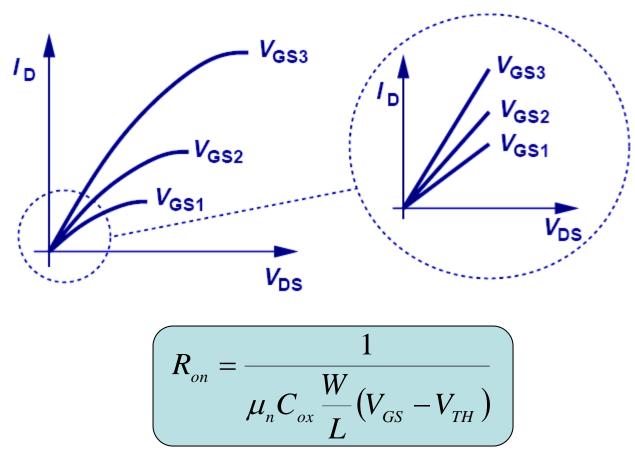

#### Linear Resistance

- At small  $V_{DS}$ , the transistor can be viewed as a resistor, with the resistance depending on the gate voltage.

- It finds application as an electronic switch.

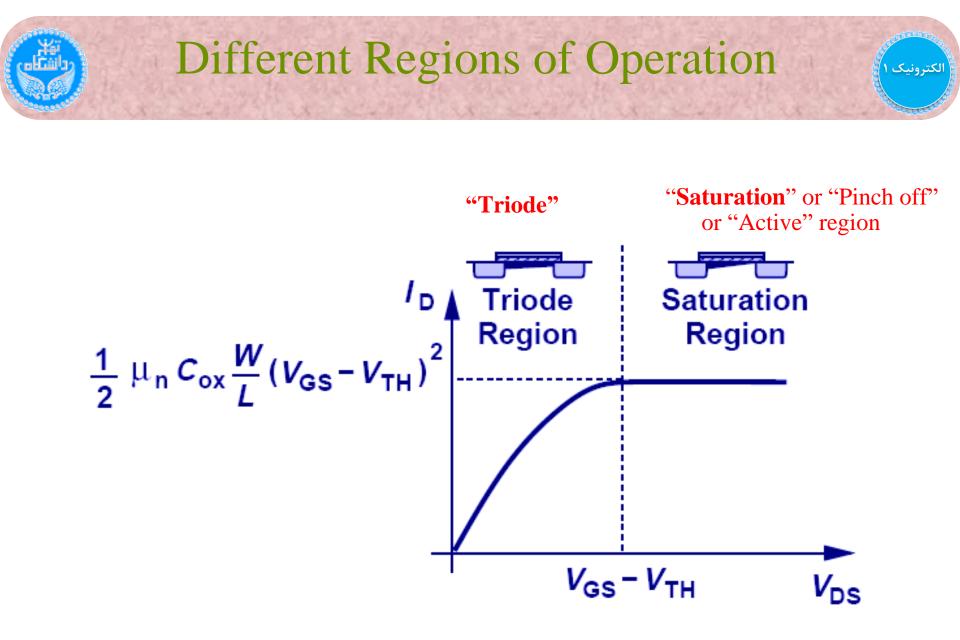

- When the potential difference between gate and drain is greater than  $V_{TH}$ , the MOSFET is in triode region.

- When the potential difference between gate and drain becomes equal to or less than  $V_{TH}$ , the MOSFET enters saturation region.

#### Triode or Saturation?

Assume  $\mu_n C_{ox} = 100 \,\mu\text{A}/\text{V}^2$  and  $V_{TH} = 0.4 \,\text{V}$

• When the region of operation is not known, a region is assumed (with an intelligent guess). Then, the final answer is checked against the assumption.

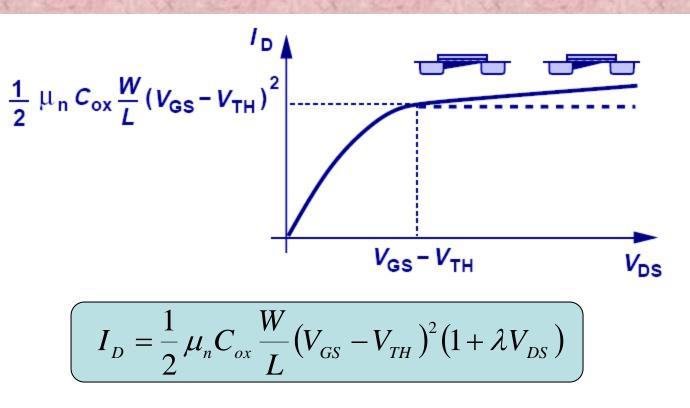

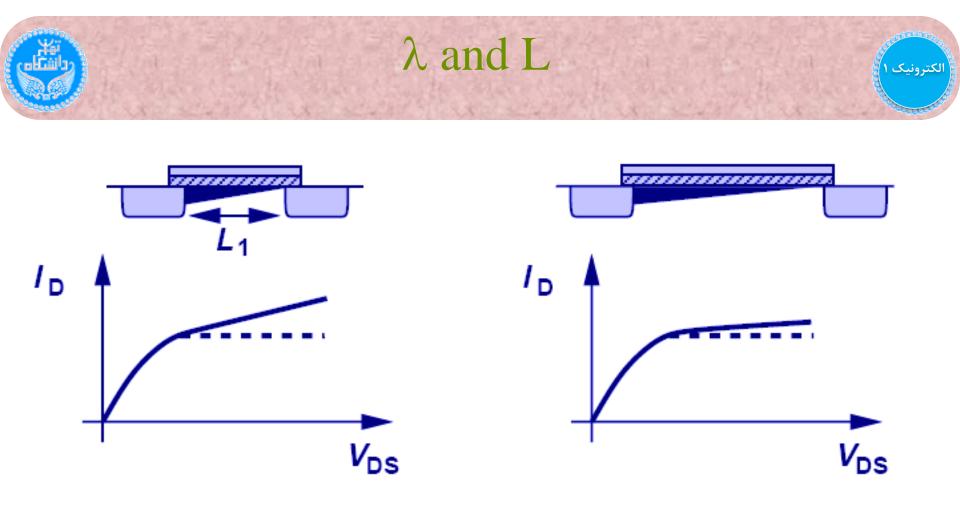

## **Channel-Length Modulation**

• The original observation that the current is constant in the saturation region is not quite correct. The end point of the channel actually moves toward the source as V<sub>D</sub> increases, increasing I<sub>D</sub>. Therefore, the current in the saturation region is a weak function of the drain voltage.

کترونیک

- Unlike the Early voltage in BJT, the channel- length modulation factor can be controlled by the circuit designer.

- For long L, the channel-length modulation effect is less than that of short L.

$$g_m = \frac{\partial I_D}{\partial V_{GS}}$$

• Transconductance is a measure of how strong the drain current changes when the gate voltage changes

### Transconductance

$$\int g_{m} = \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{TH}) \qquad g_{m} = \sqrt{2\mu_{n} C_{ox} \frac{W}{L} I_{D}} \qquad g_{m} = \frac{2I_{D}}{V_{GS} - V_{TH}}$$

CH 6 Physics of MOS Transistors

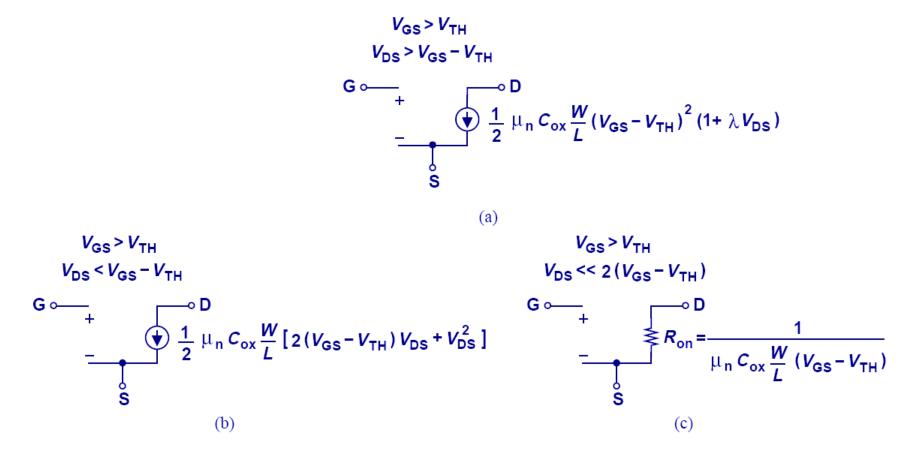

### Large-Signal Models

• Based on the value of  $V_{DS}$ , MOSFET can be represented with different large-signal models.

CH 6 Physics of MOS Transistors

کترونیک

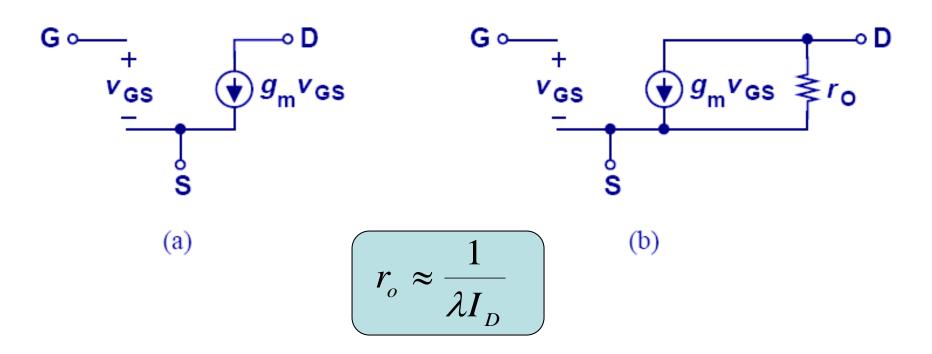

# Small-Signal Model

- When the bias point is not perturbed significantly, small-signal model can be used to facilitate calculations.

- To represent channel-length modulation, an output resistance is inserted into the model.

$\lambda I_r$

$$I_{D} = \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^{2} (1 + \lambda V_{DS}) \qquad \Longrightarrow \qquad r_{o} \approx$$

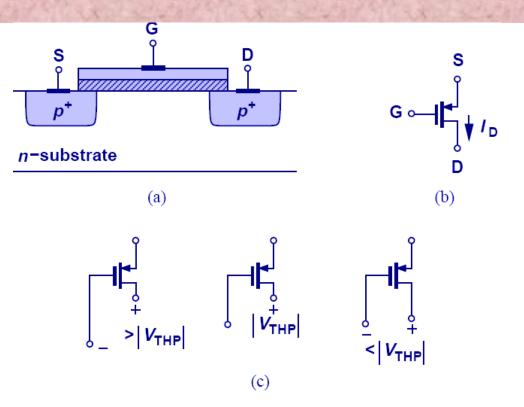

## **PMOS** Transistor

- Just like the PNP transistor in bipolar technology, it is possible to create a MOS device where holes are the dominant carriers. It is called the PMOS transistor.

- It behaves like an NMOS device with all the polarities reversed.

## **PMOS** Equations

S G ⊶ L J D

$$I_{D,sat} = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 (1 - \lambda V_{DS})$$

$$I_{D,tri} = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} [2(V_{GS} - V_{TH})V_{DS} - V_{DS}^2]$$

$$I_{D,sat} = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} (|V_{GS}| - |V_{TH}|)^2 (1 + \lambda |V_{DS}|)$$

$$I_{D,tri} = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} [2(|V_{GS}| - |V_{TH}|)V_{DS} - V_{DS}^2]$$

CH 6 Physics of MOS Transistors

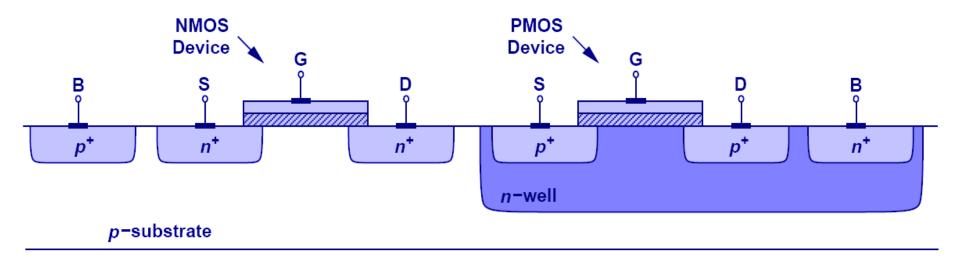

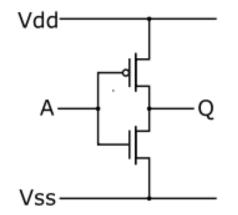

# **CMOS** Technology

- It possible to grow an n-well inside a p-substrate to create a technology where both NMOS and PMOS can coexist.

- It is known as CMOS, or "Complementary MOS".

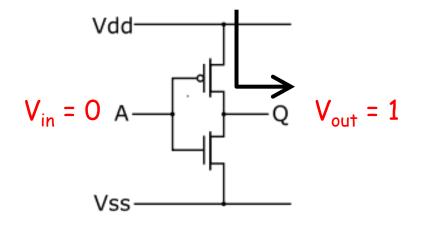

Negative gate turns pMOS on

More importantly, since one is open and one is shut at steadystate, <u>no current except during turn-on/turn-off</u>

$\rightarrow$  Low power dissipation

## Comparison of Bipolar and MOS Transistors

| Bipolar Transistor              | MOSFET                                                          |

|---------------------------------|-----------------------------------------------------------------|

| Exponential Characteristic      | Quadratic Characteristic                                        |

| Active: V <sub>CB</sub> > 0     | Saturation: V <sub>DS</sub> > V <sub>GS</sub> – V <sub>TH</sub> |

| Saturation: V <sub>CB</sub> < 0 | Triode: V <sub>DS</sub> < V <sub>GS</sub> – V <sub>TH</sub>     |

| Finite Base Current             | Zero Gate Current                                               |

| Early Effect                    | Channel-Length Modulation                                       |

| Diffusion Current               | Drift Current                                                   |

| –                               | Voltage-Dependent Resistor                                      |

• Bipolar devices have a higher  $g_m$  than MOSFETs for a given bias current due to its exponential IV characteristics.