## Rigital Logic Resign Lecture 6

## Dr. Navabi

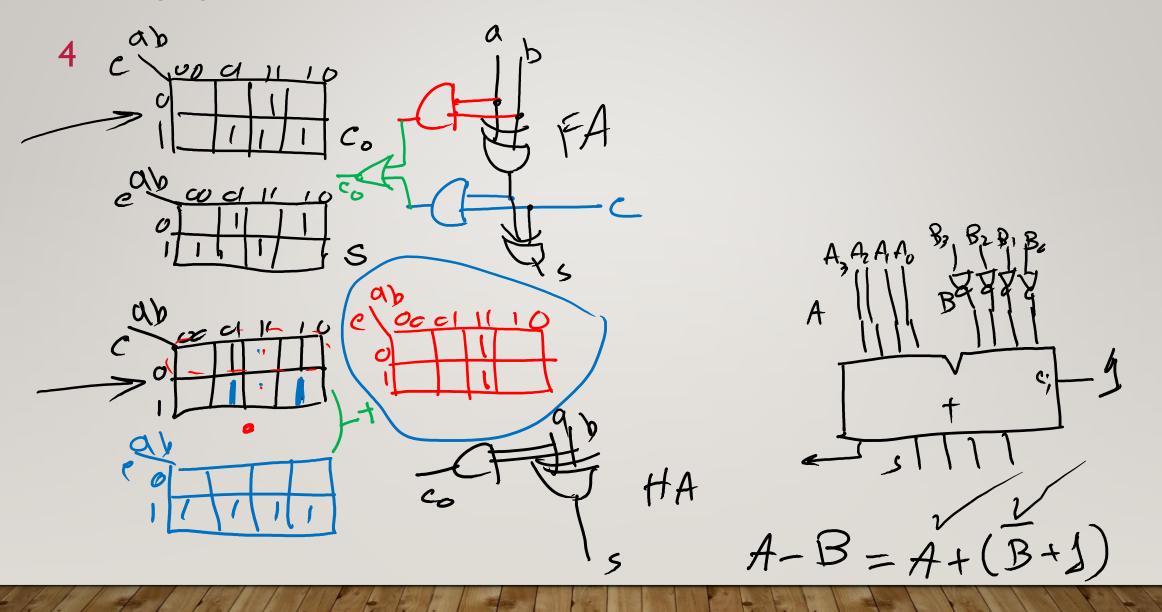

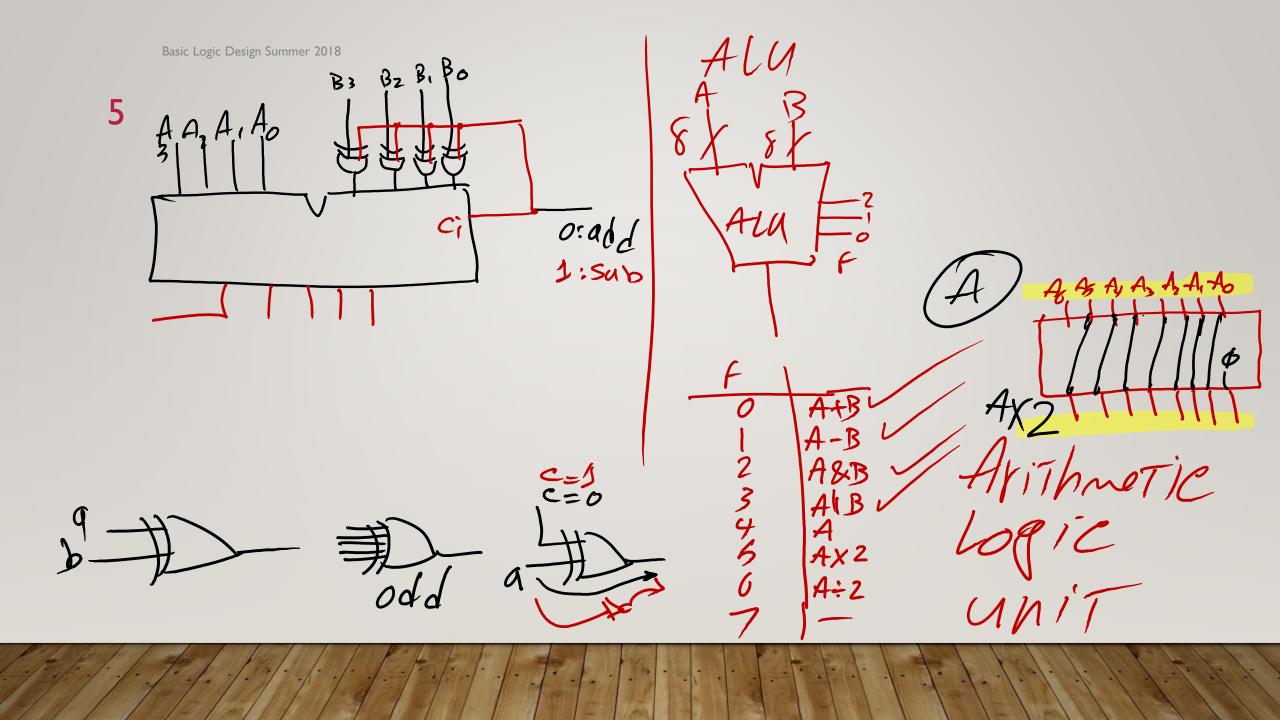

BZ A, BI A. Bo Basic Logic Design Summer 2018 3 52 Co HjBj  $C_{o}, S;$ 00 01/11 C; C; A; B; $C_{i}$ 0 bc +ac 0 200 Ai Q 0 0 *A;B;* B 0 C = goboc O abetabetabe tabé C = CCit a=A1 Aa(betbe) = adber =B. bctbc) 5 = 51 bac Co b OC

1

Basic Logic Design Summer 2018

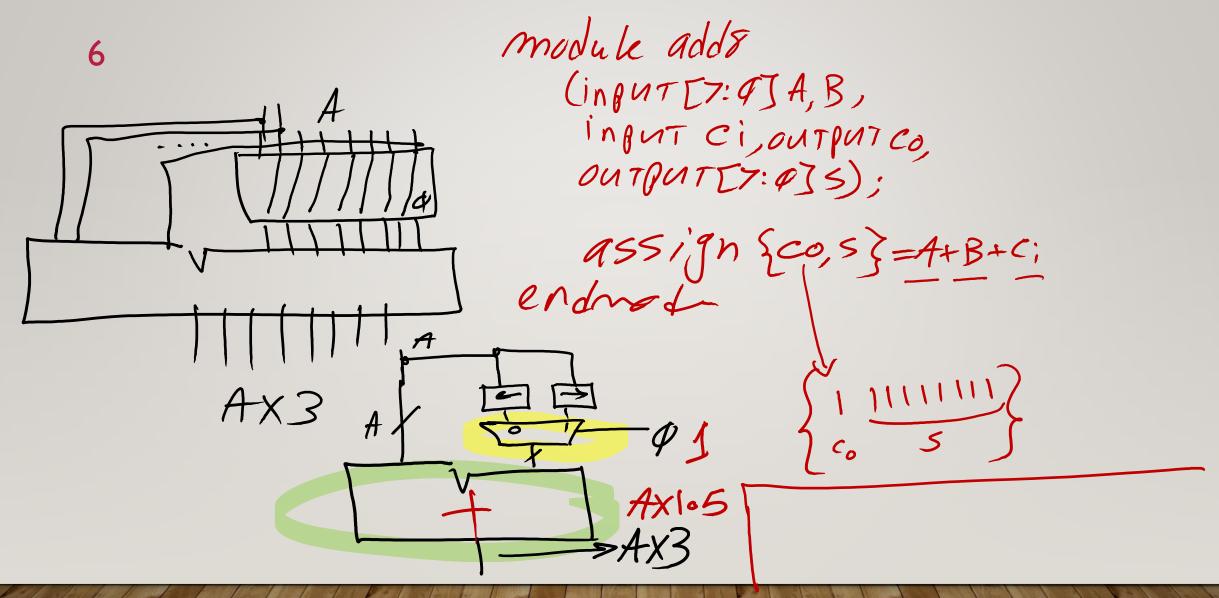

module FA (inputa, b, c outputéo, s); assign Sco, s} = a+b+c; alway sa(9,b,c) begin endnodu =q+b+C;assign 5 = a b b c; assign c= a & b | a & c | b & c; of

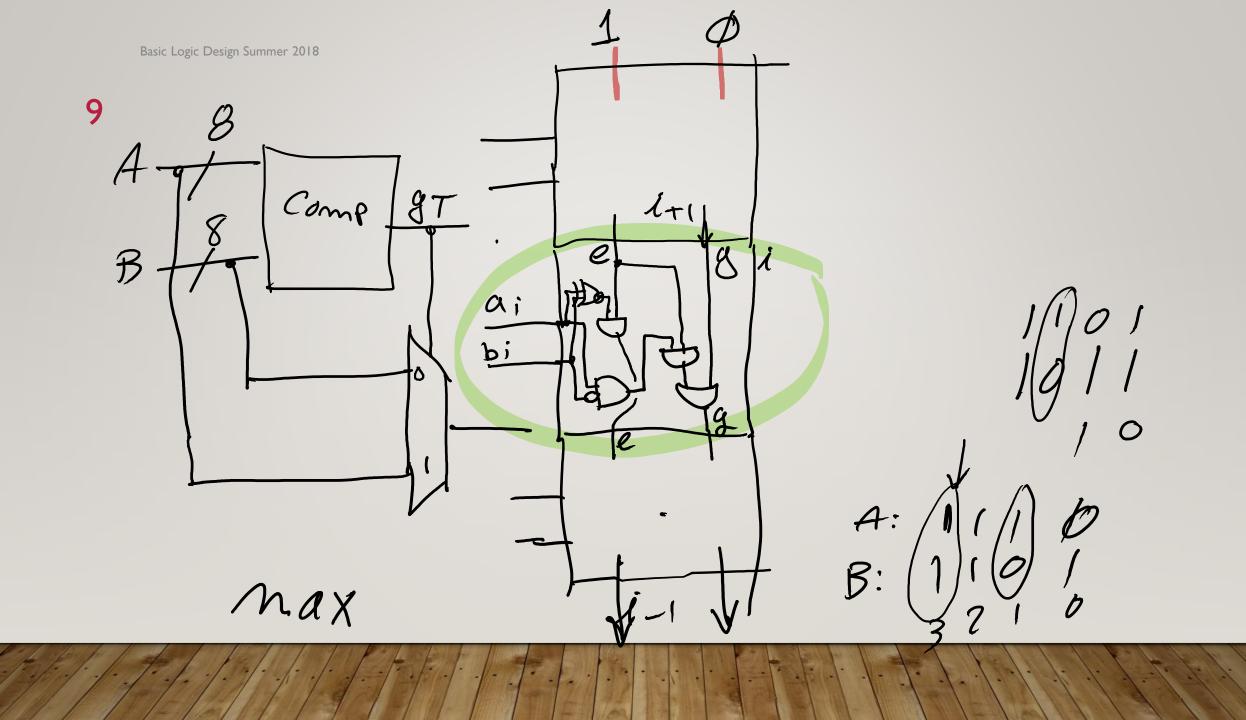

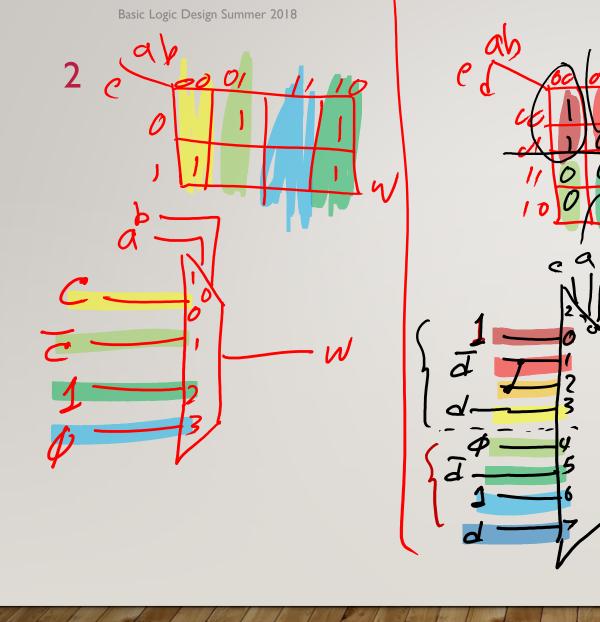

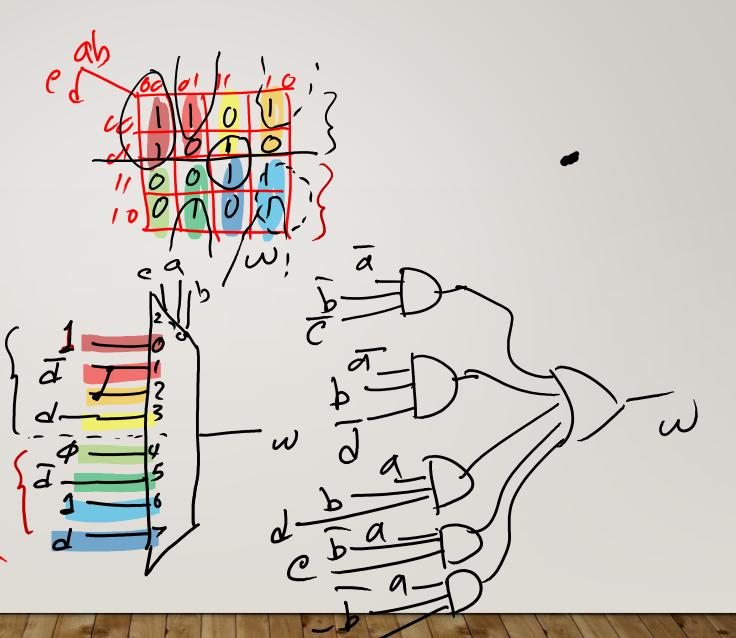

Basic Logic Design Summer 2018 INPUT Rule X incle all signals being vode on the always sensitivity list \$:A+B 1: A + 0.6B 2) OUTPUT BULE indiscriminity sellall outputs to re 2:Max(A,B)3: A& B inactive bales at The begining of module alus (input [7:0]A,B, input [:0]F, output [0, output [7:0] (w); The alway always@(A, B, F)begin endcase Case (F. end endmodule,  $z'b\phi\phi: \{co, w\} = A+B;$ (0, w) = A + 0.5B2'501: W=A: else W= R: