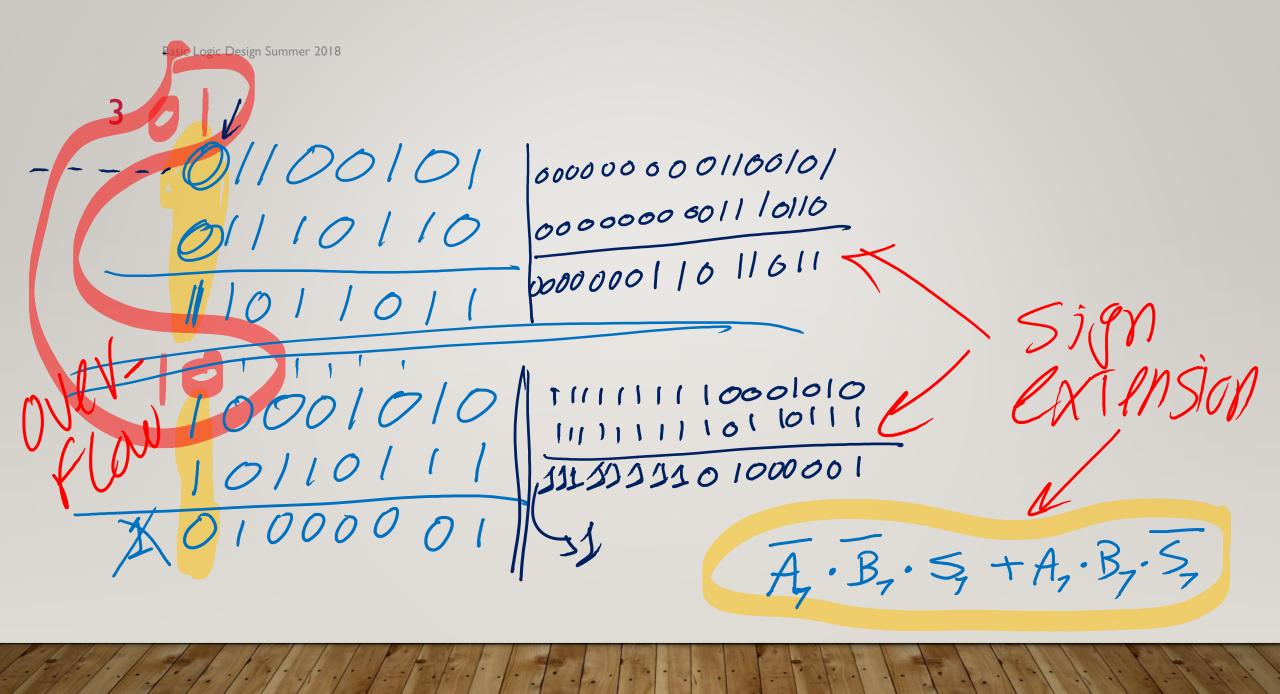

## Pigital Logic Pesign Lecture 2

Dr. Navabi

#7 0/2

TOS, TOP, TOZ

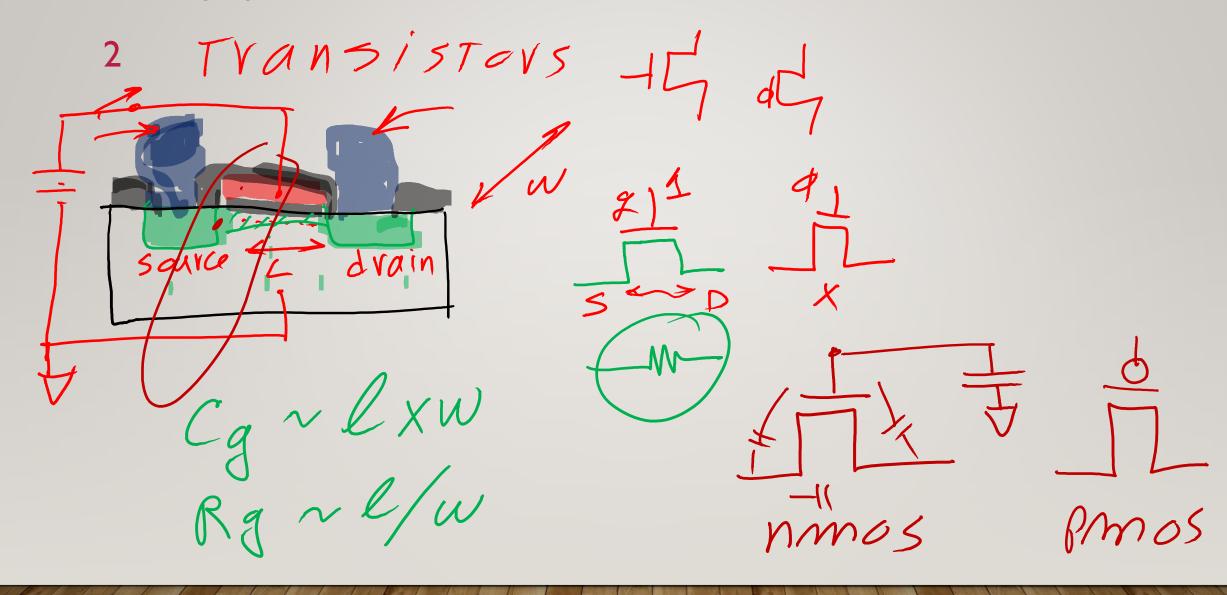

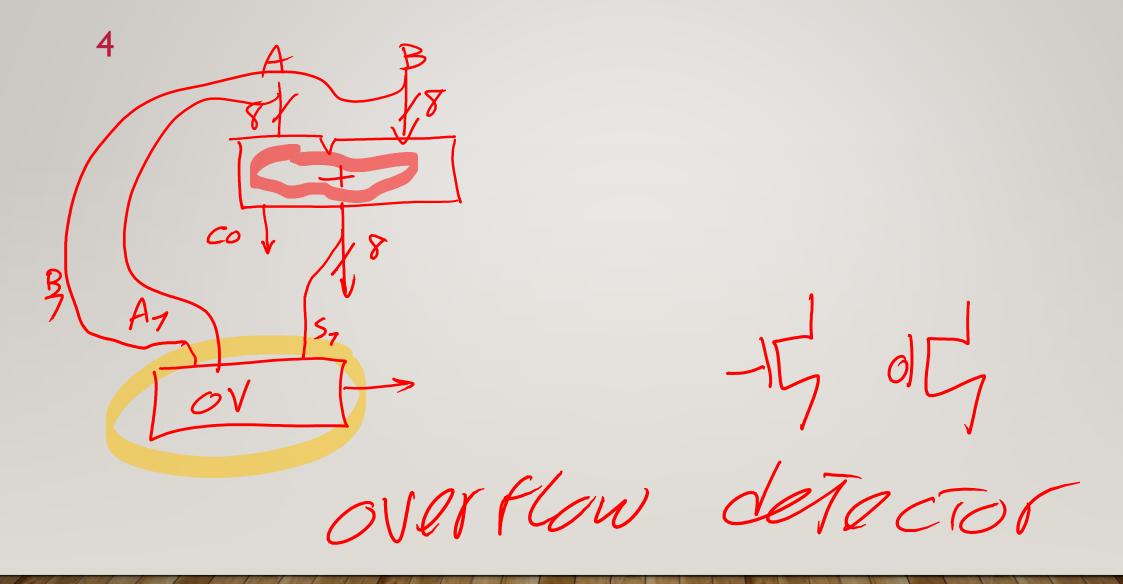

Basic Logic Design Summer 2018 Build Inversor module myinv (input a, output w); Supply OGnd; lmos #7 (w, Vdd,a); Mmos #5 (W, Gnd, a) WOIST CASO: 7 Basic Logic Design Summer 2018

w = a . b  $=a \uparrow b$ = ~ (a8b) nand#(10,1);

module mynand (infuta,b, wive J; output w); supplys vdd; supplyo Gnd; Pmos #7 T/(w, vdd, a); Amas #7 72 (w, vdd, b); nmos#TY (J, Gnd, b); nmas #5T3 (W, T, a); endmodale