## Pigital Logic Pesign Lecture

Dr. Navabi

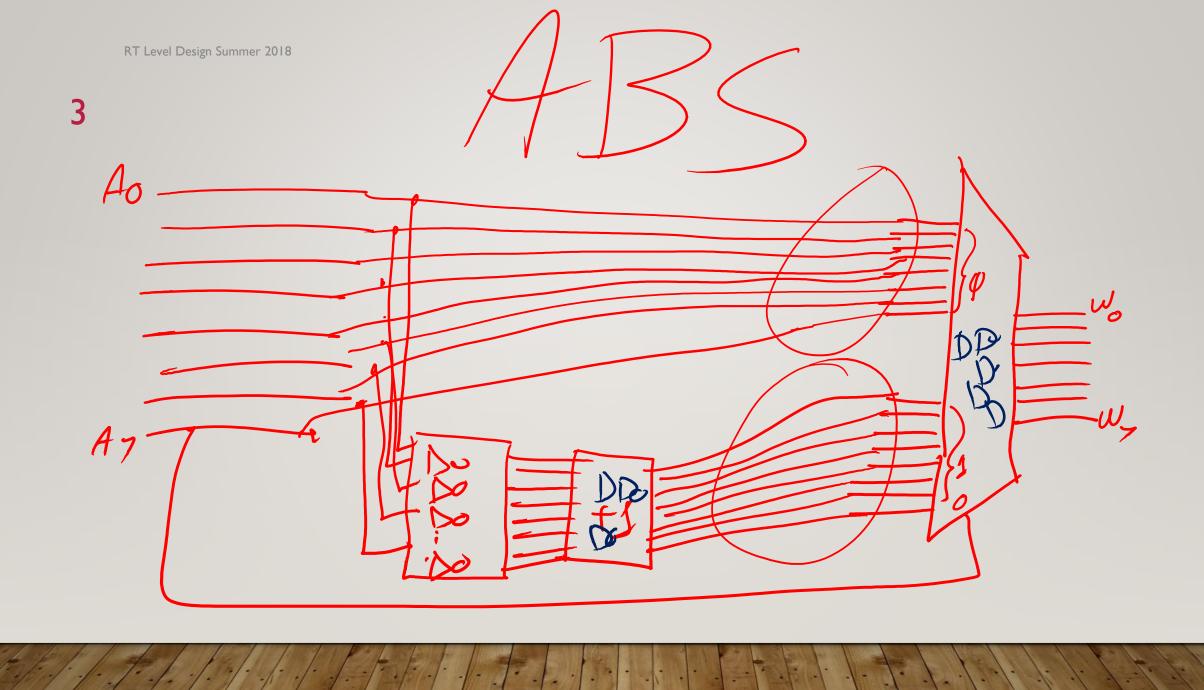

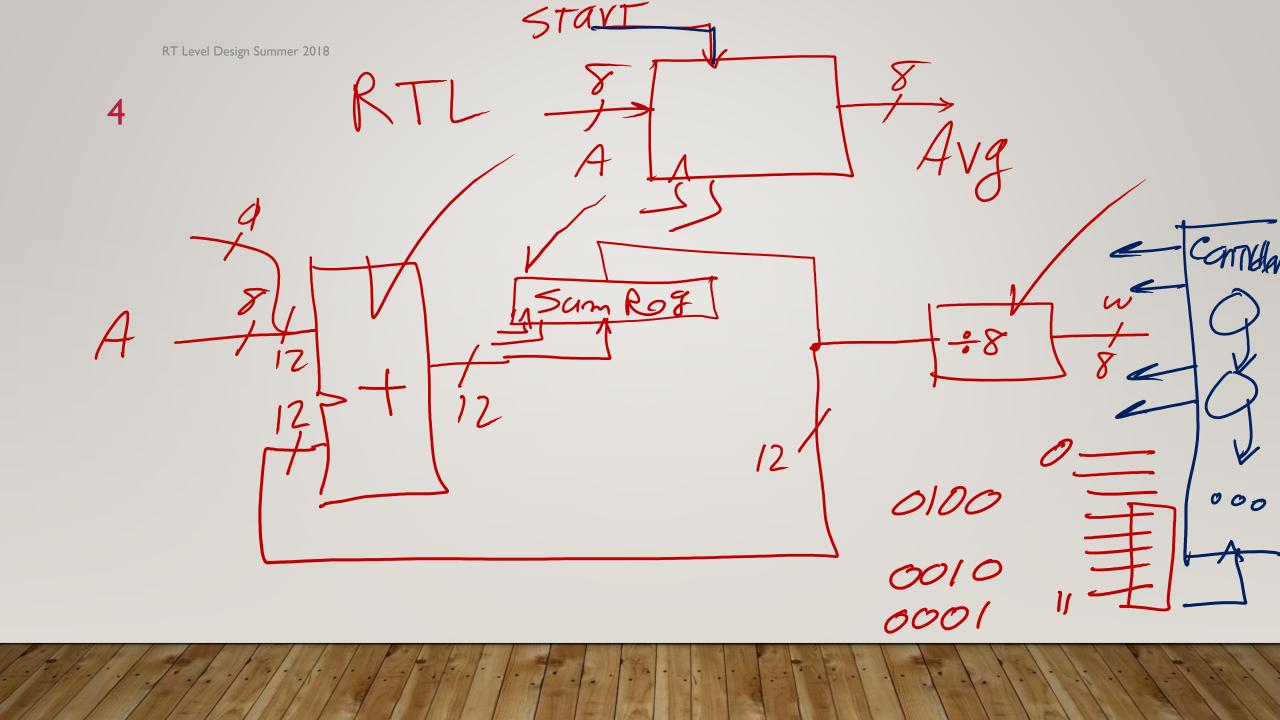

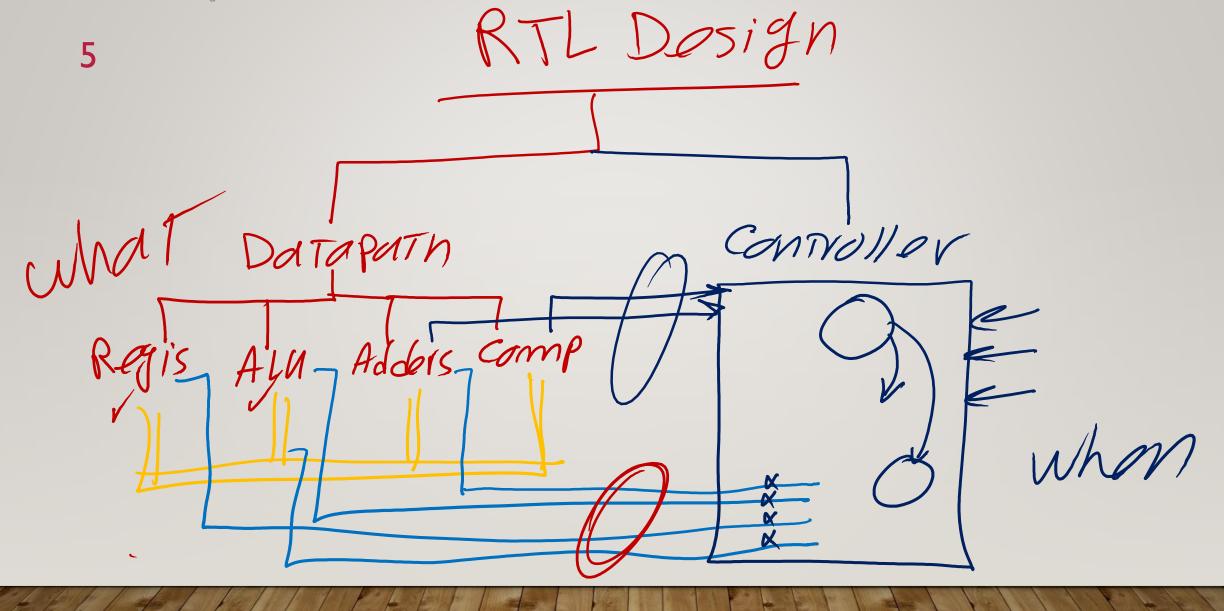

2 Lectures RTL Régister Transfer Leval A - 1 > ABS 8 - W A: 10110010 W:01001110

ConNoller Sin(n \* GaTes XRTL Comp Adder MUX DCD Cam P ALU Inc

CNTY Shiffleg \* BUSSing

STATE Machines FSM MUCTIPLE S.M.

8 RTL Comp. \* RTL Method. A ShTer-RTL Comm. \* Wrappers

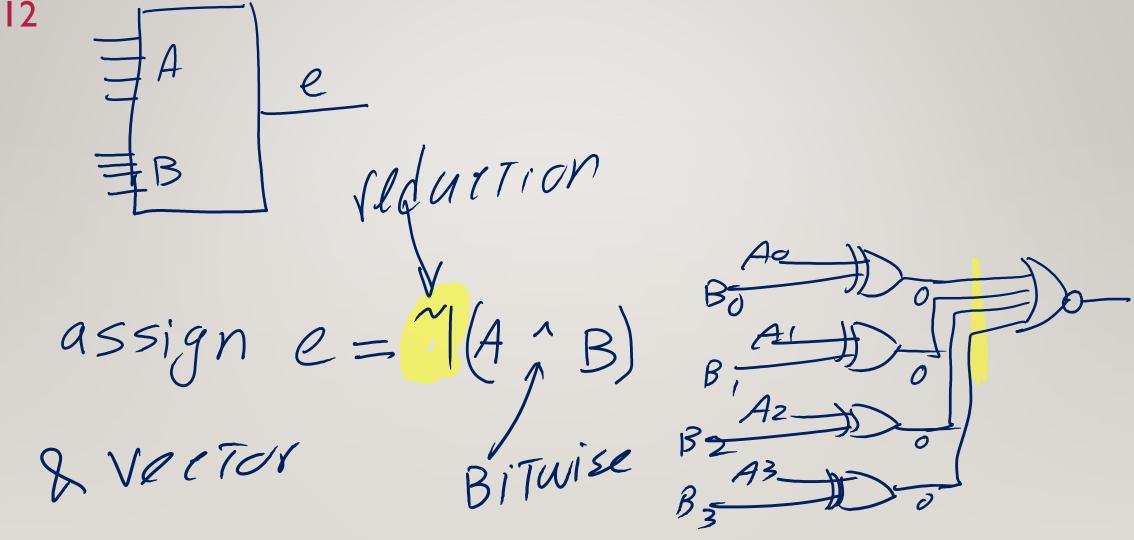

9 GATCS 3D-w=abb;

modale myand (input a, b, output w); and #(3,5) Us (w, b, a); endmadale > assign #(3,5) w = a & b;

w= a&b C&d

RT Level Design Summer 2018 hand (w,a,b,c). nand #(4)(w,a,b,c,d);nand #(35)(w,a,b);assign #(35) w = (a & b); RT Level Design Summer 2018 XoY ( $\omega$ ,  $\alpha$ , b, c);  $w = a \wedge b;$

13

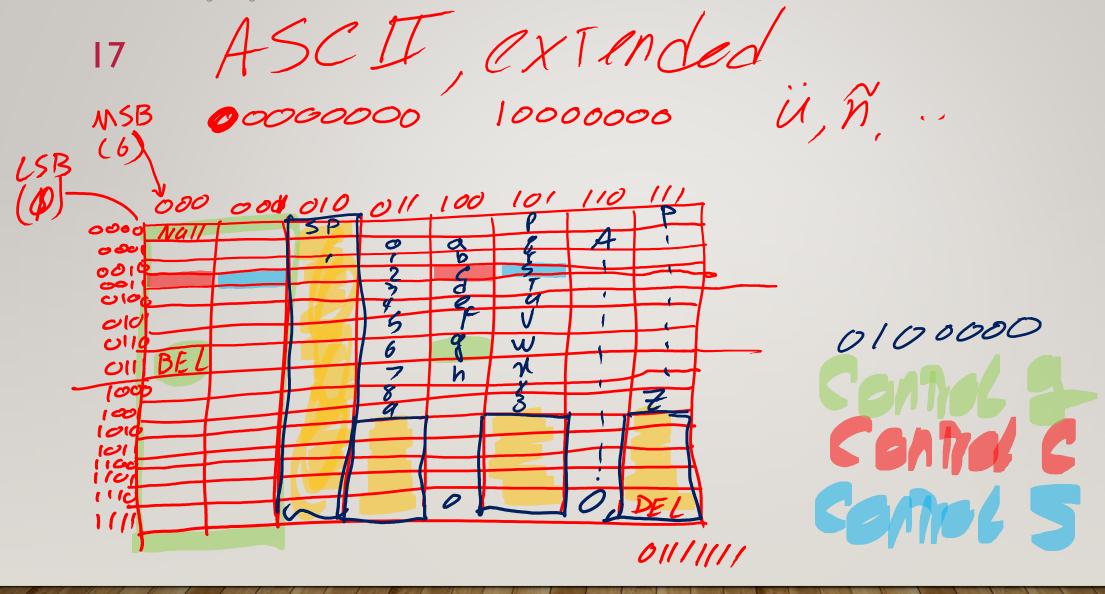

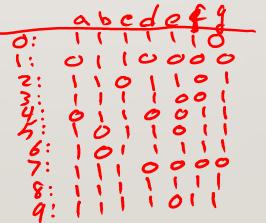

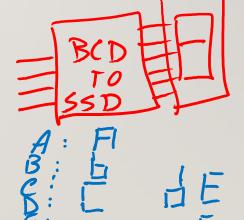

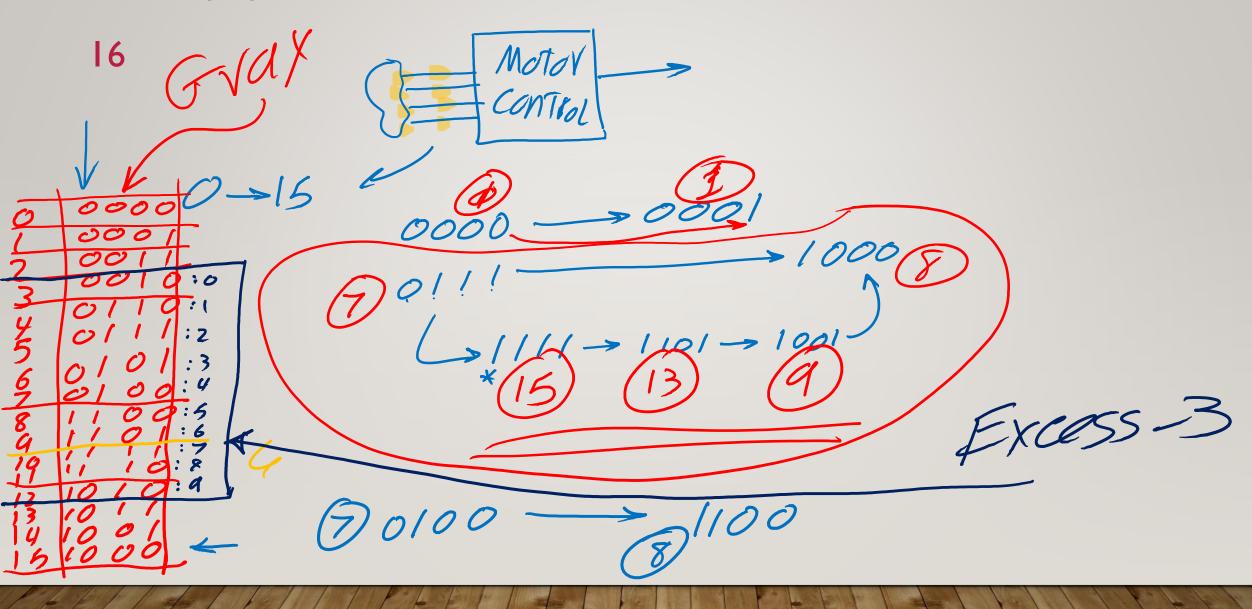

modale Simple Compliant [3:4] A, B, Output e); assign  $e="(A^1B);$ endmodab 14 Codes (leTure JB Binary (Int Frac, signed) BCD Gray ASCIT

0101

BCD: Binary Coded Decimal

0000:0 0001:1

0010:2

0011:3

0100:4

0101:5 0110:6

0111:7

1000:8

1001:9

Basic Logic Design Summer 2018