- Procedural Languages for Hardware Modeling

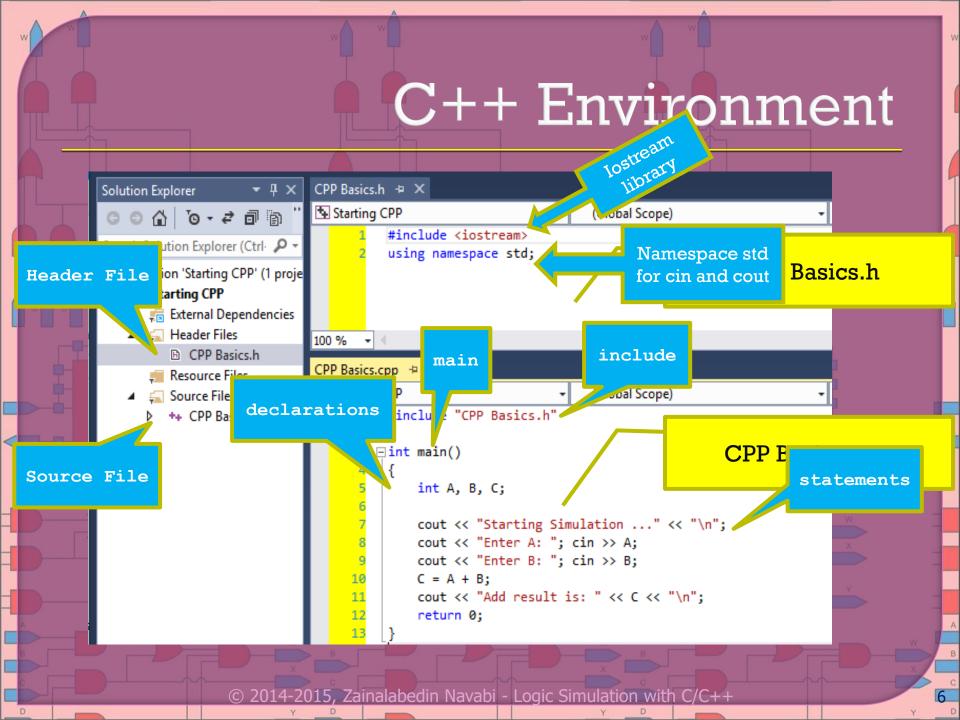

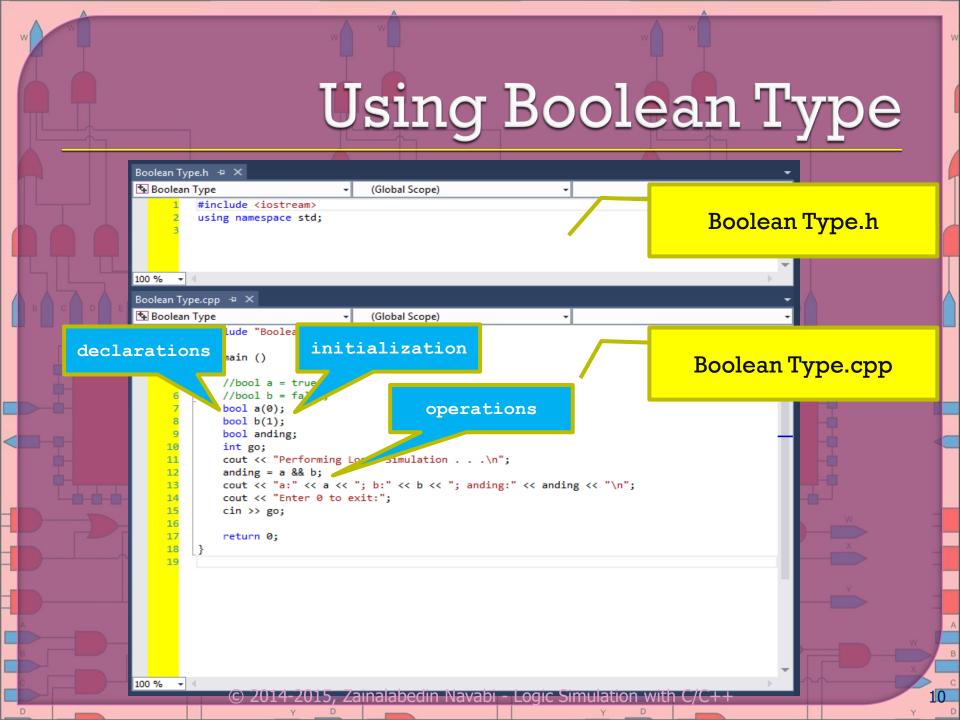

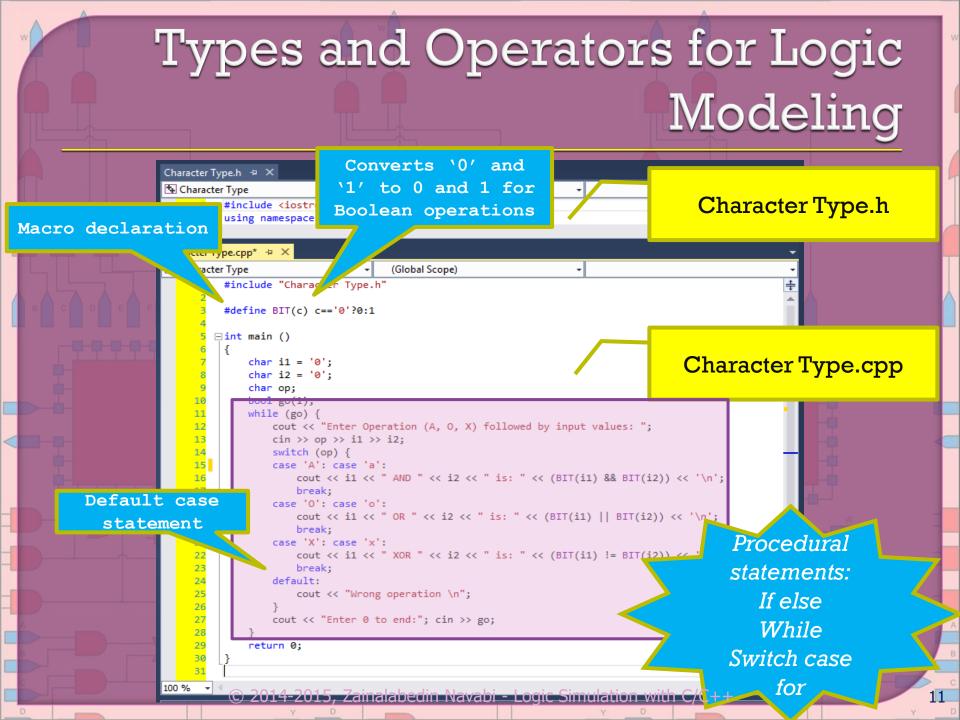

- Types and Operators for Logic Modeling

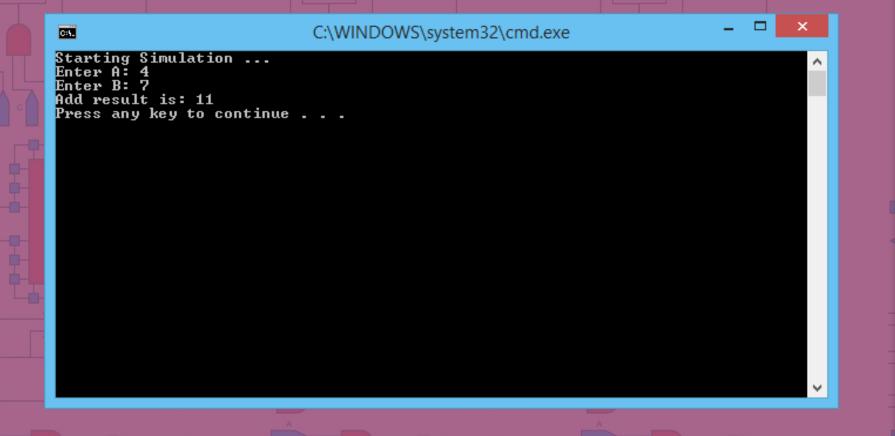

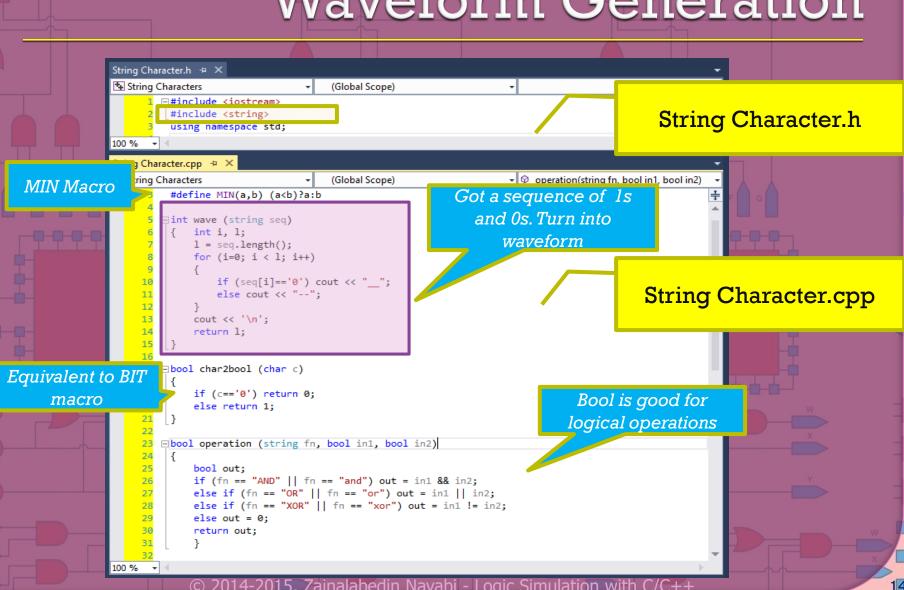

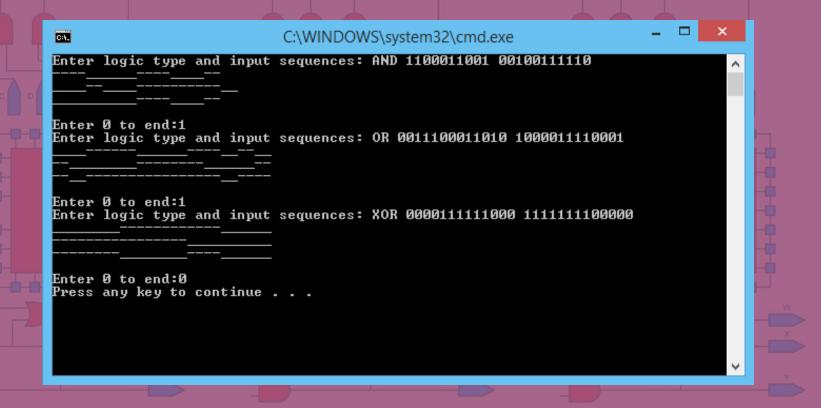

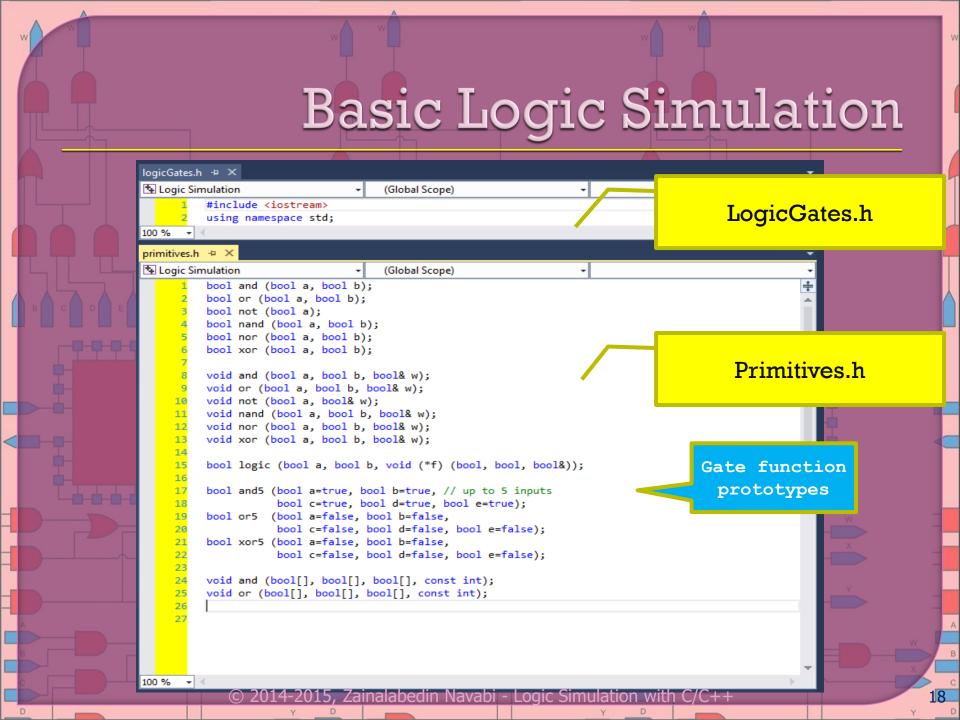

- Basic Logic Simulation

- Logic functions

- Function overloading

- Passing logic functions

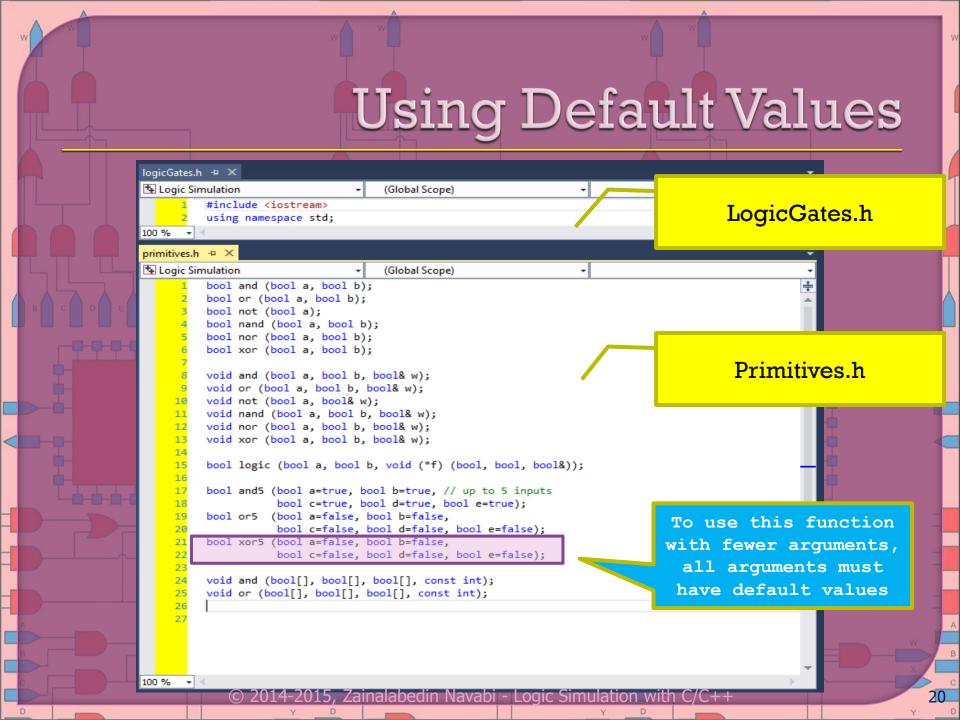

- Using default values

- Building higher level structures

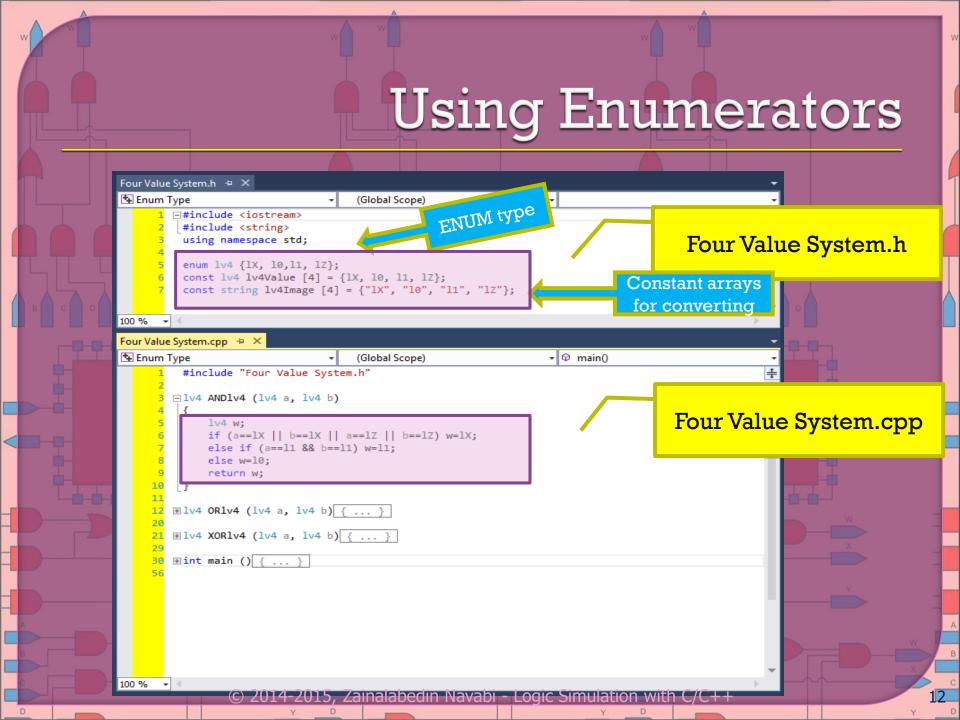

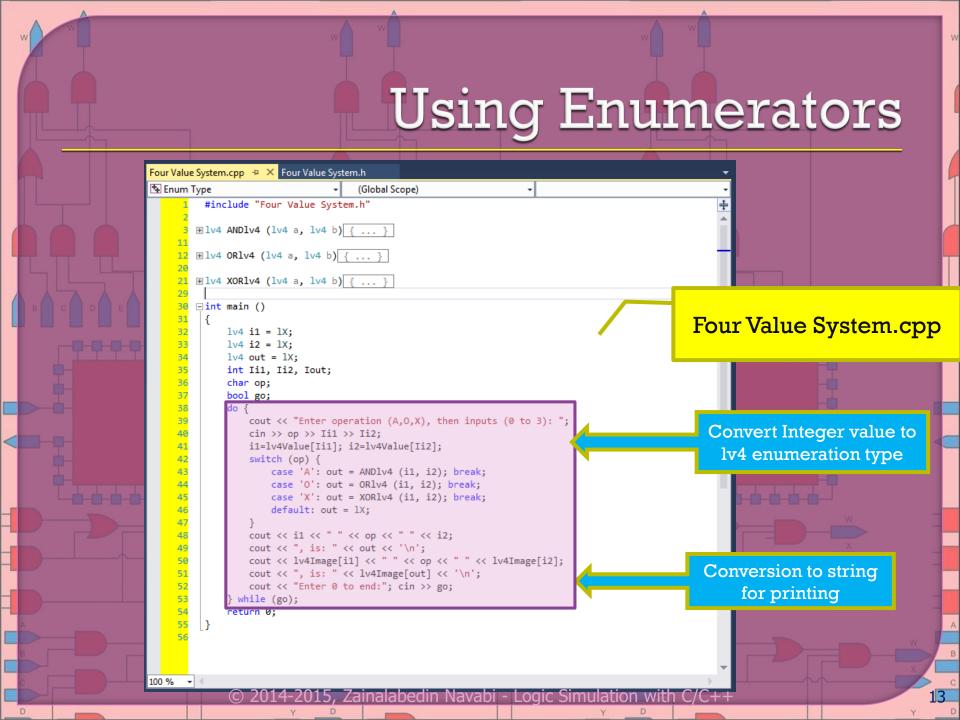

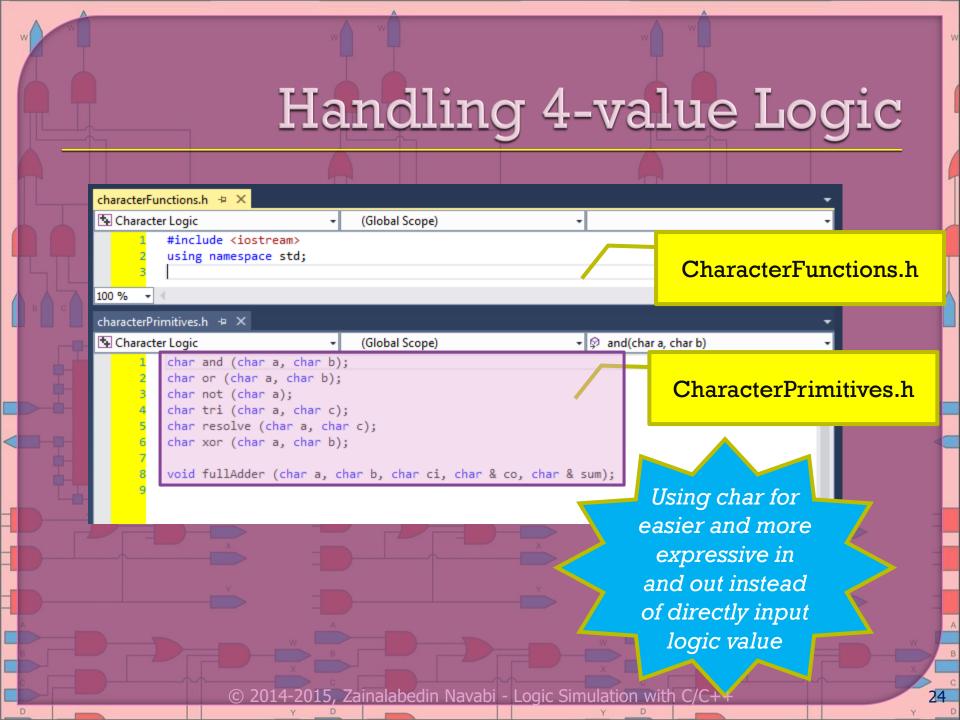

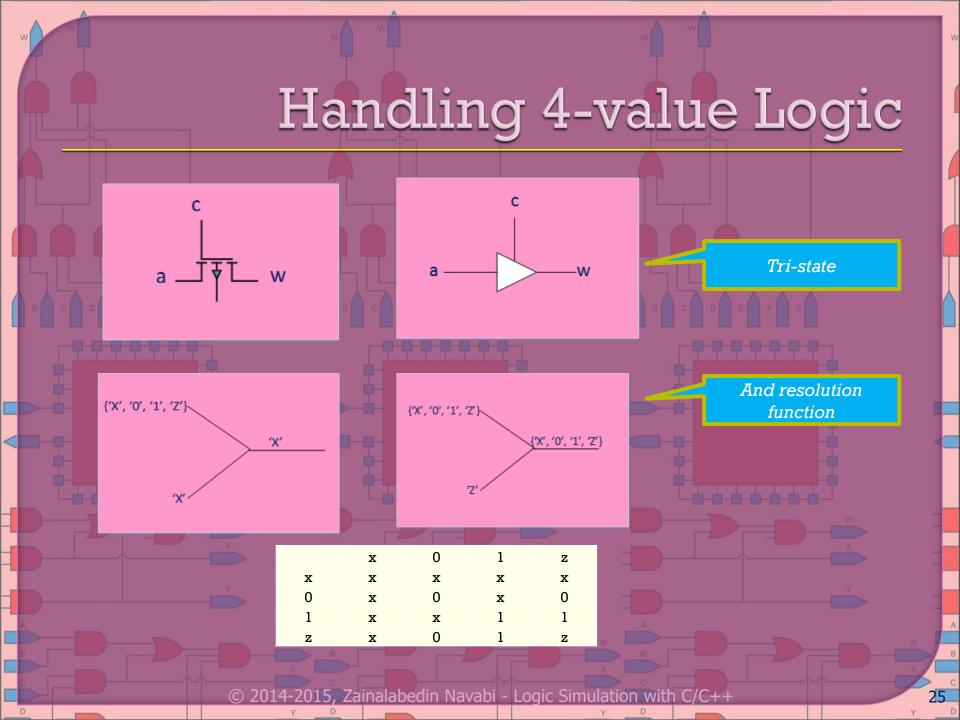

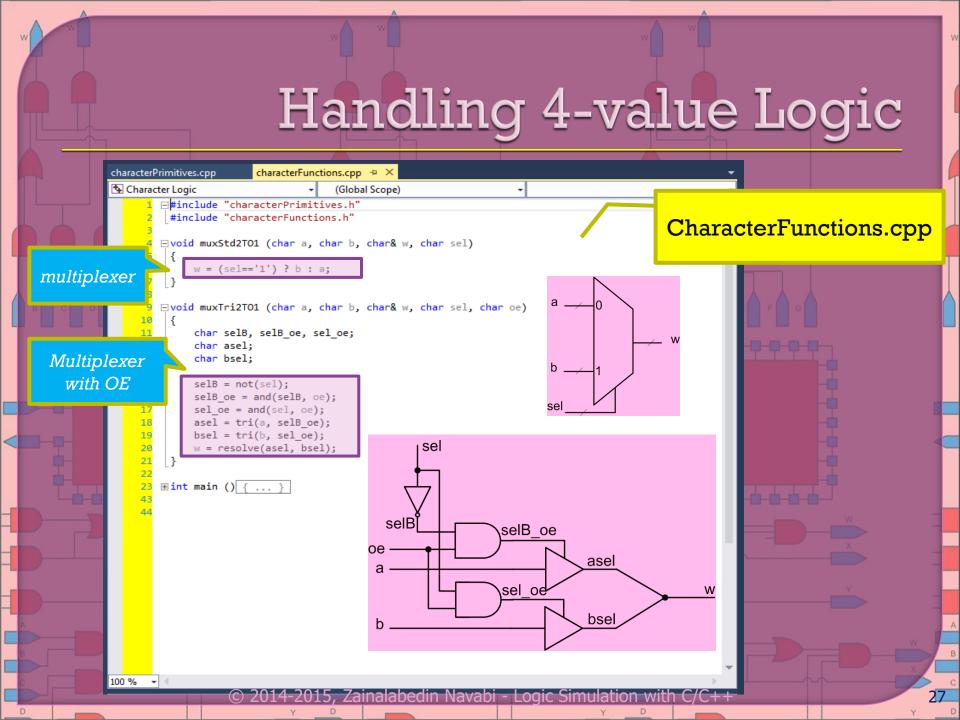

- Handling 4-value logic

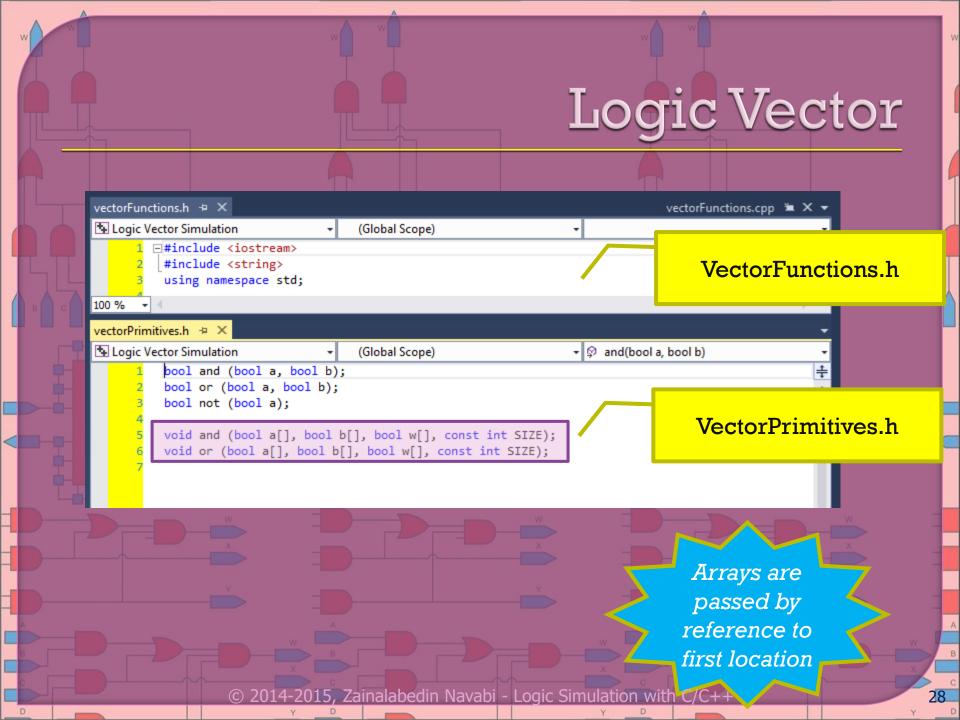

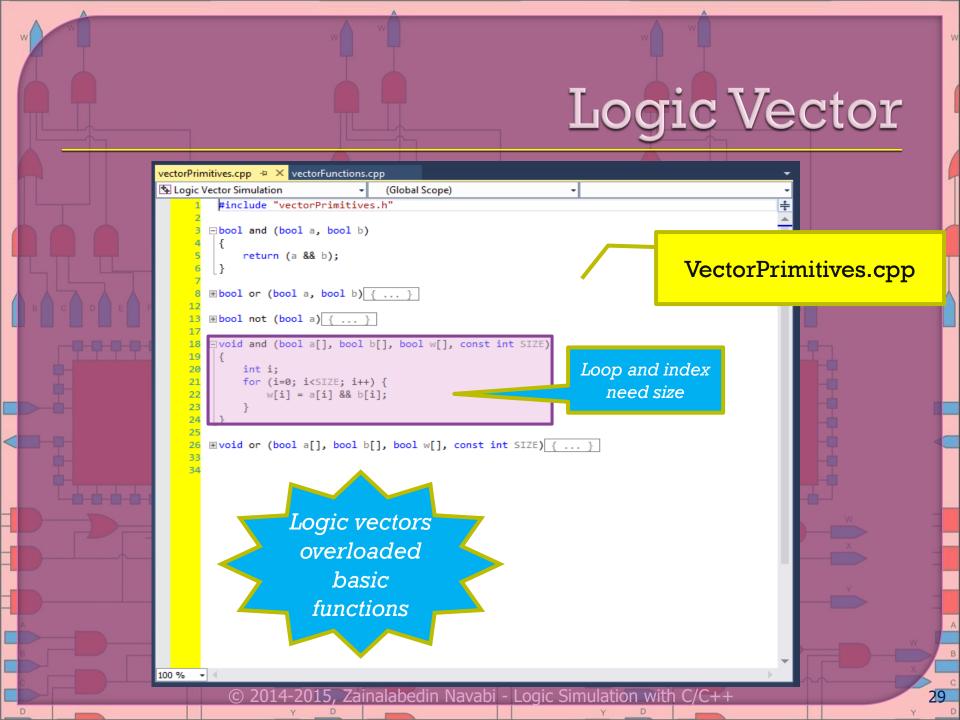

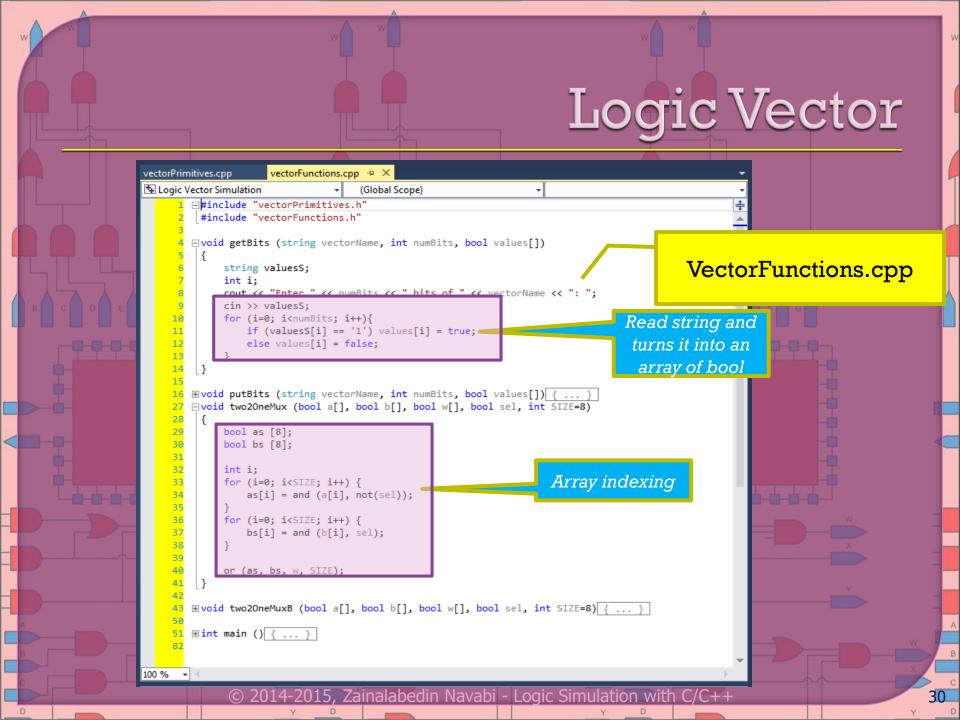

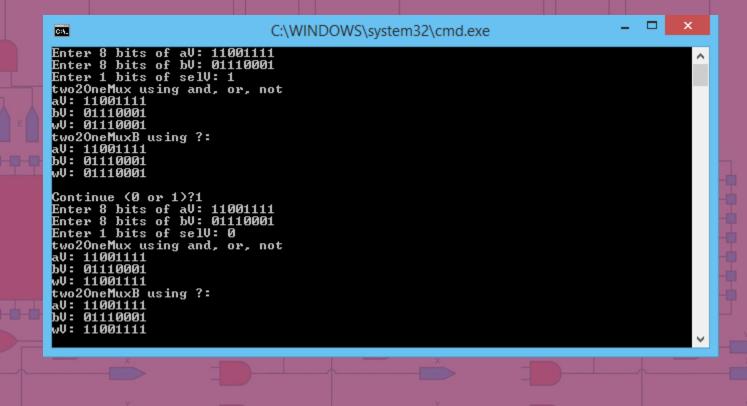

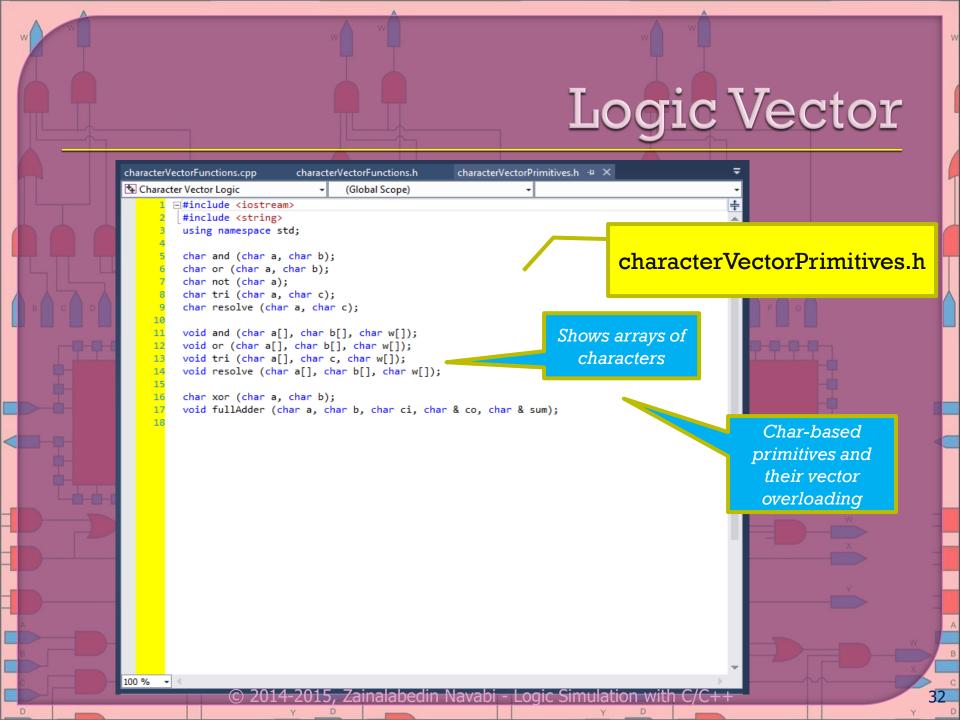

- Logic vector

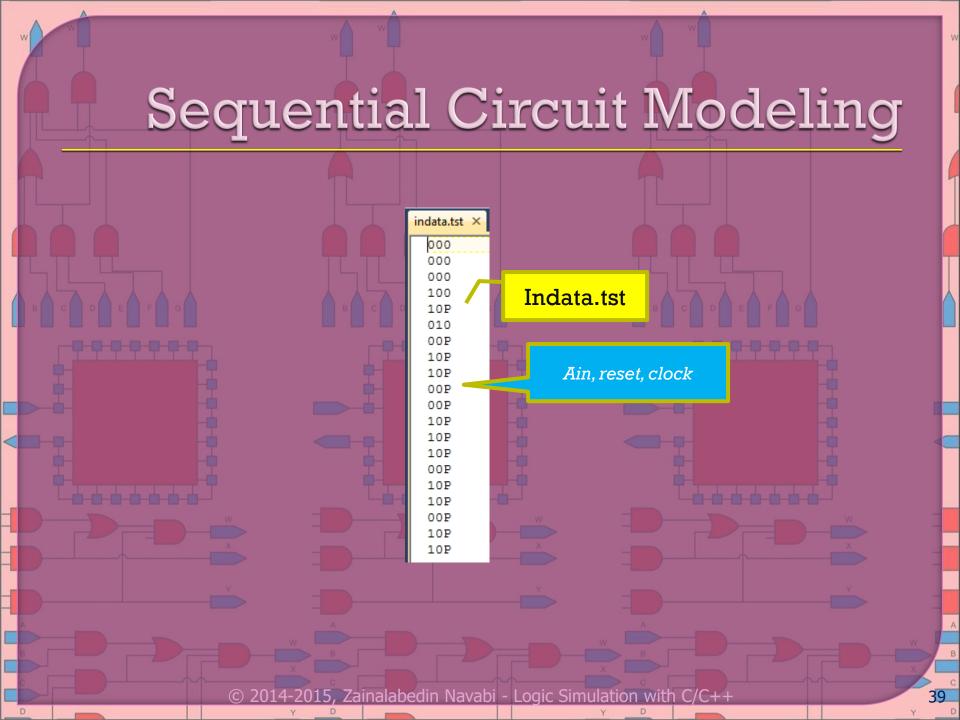

- Sequential circuit modeling

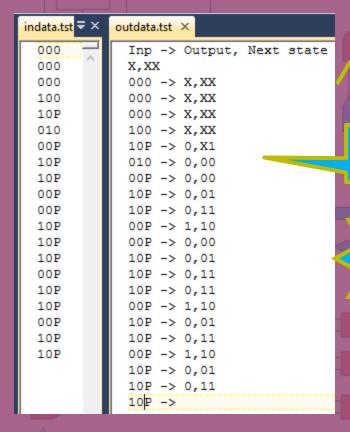

- Using pointers for logic vectors

- Enhanced logic simulation with timing

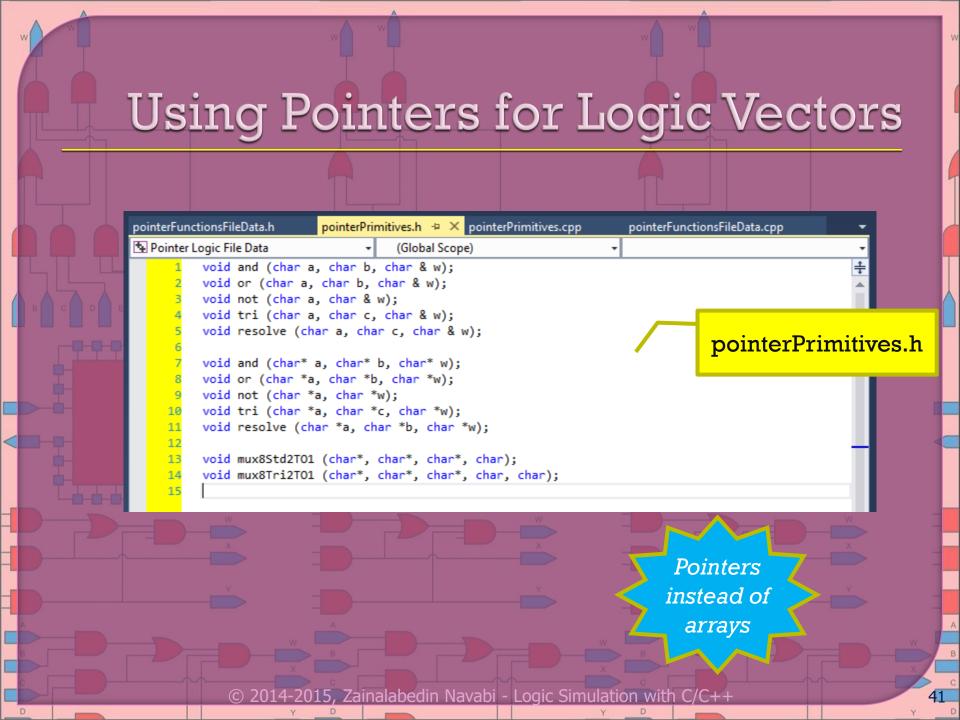

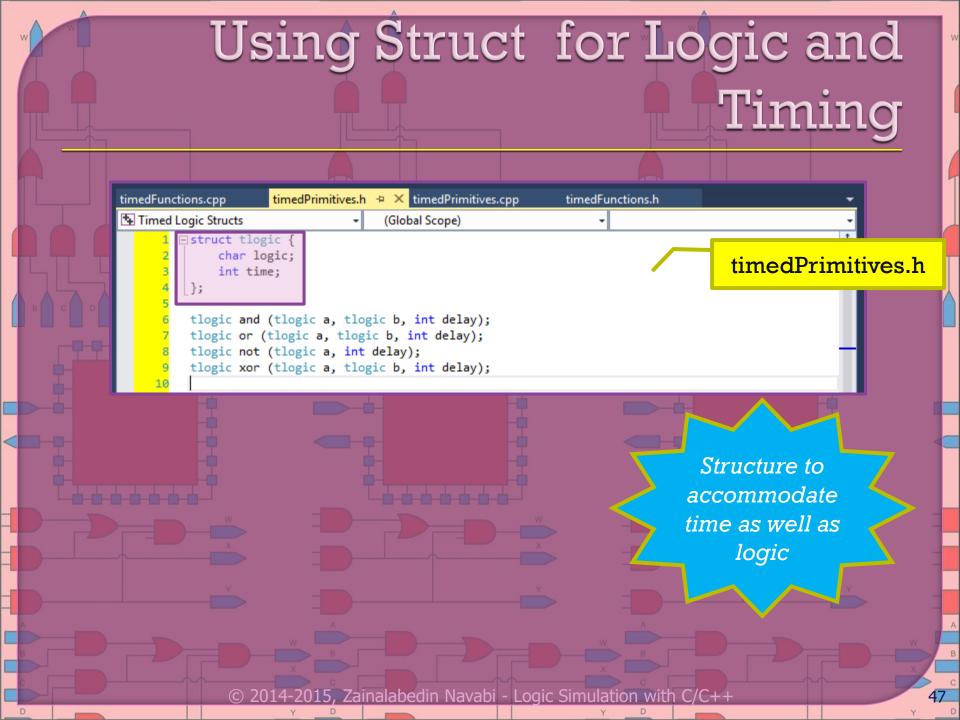

- Using struct for timing and logic

- Gates that handle timing

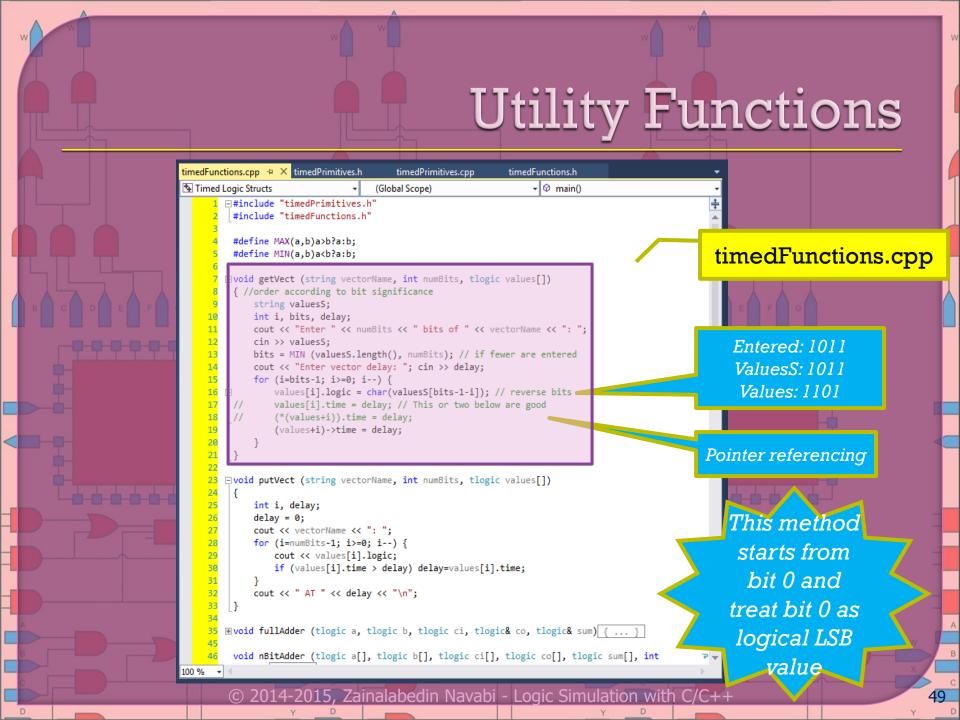

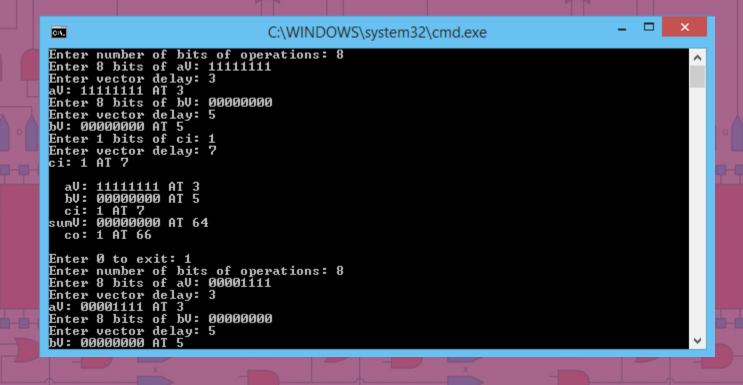

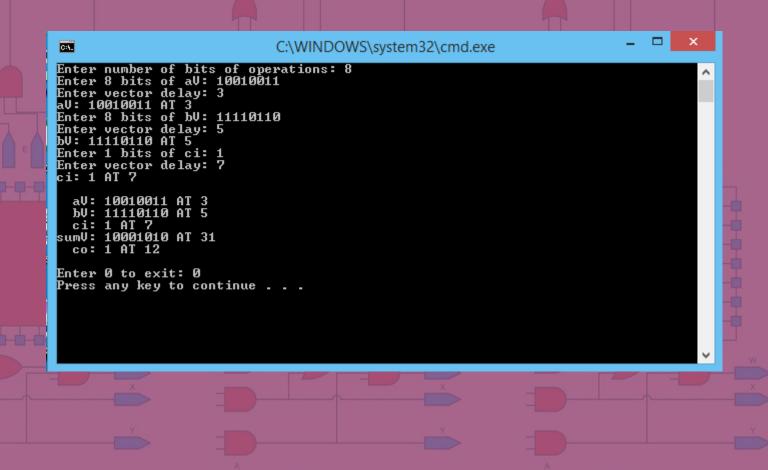

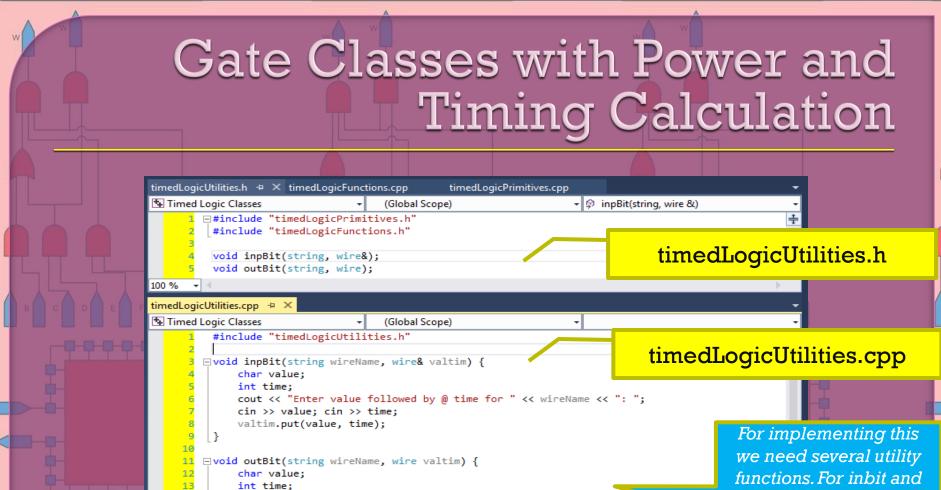

- Utility functions

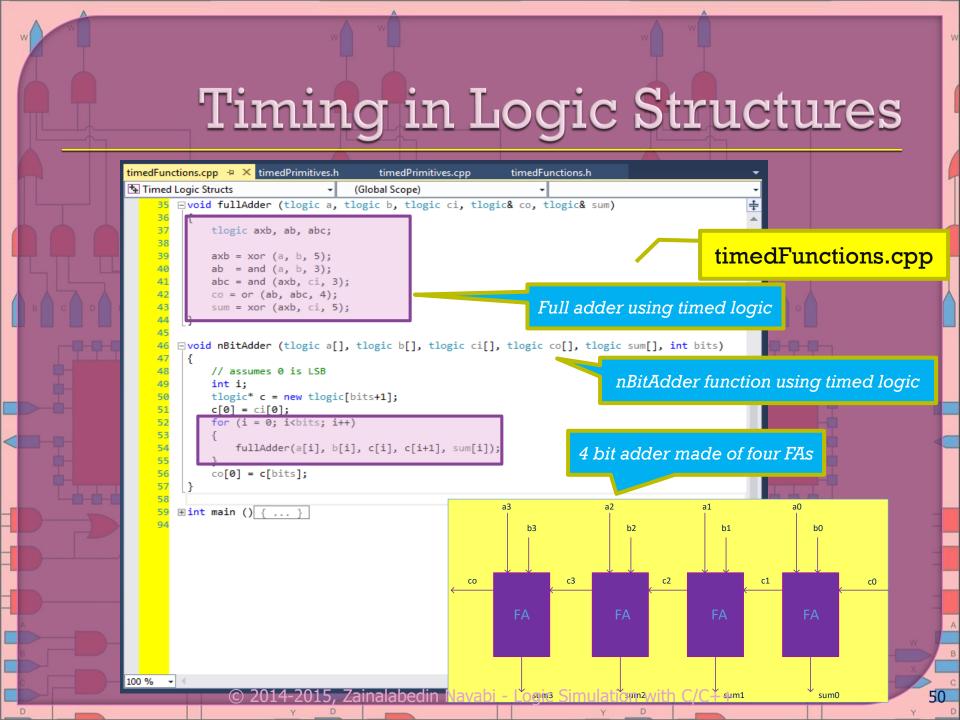

- Timing in logic structures

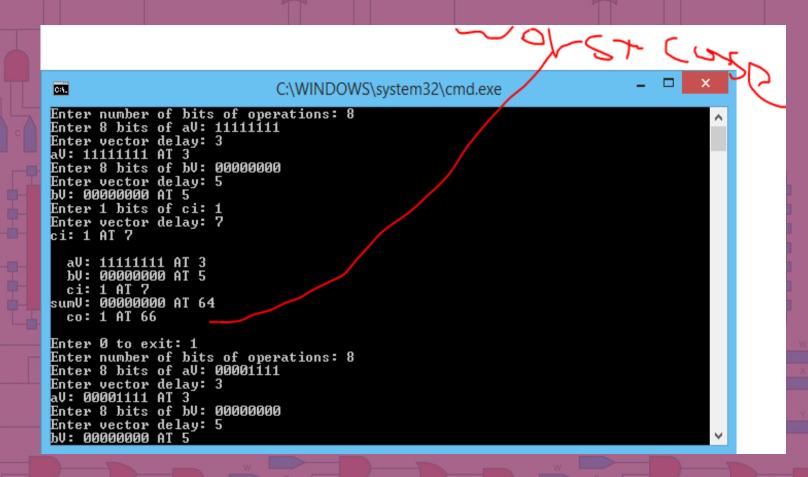

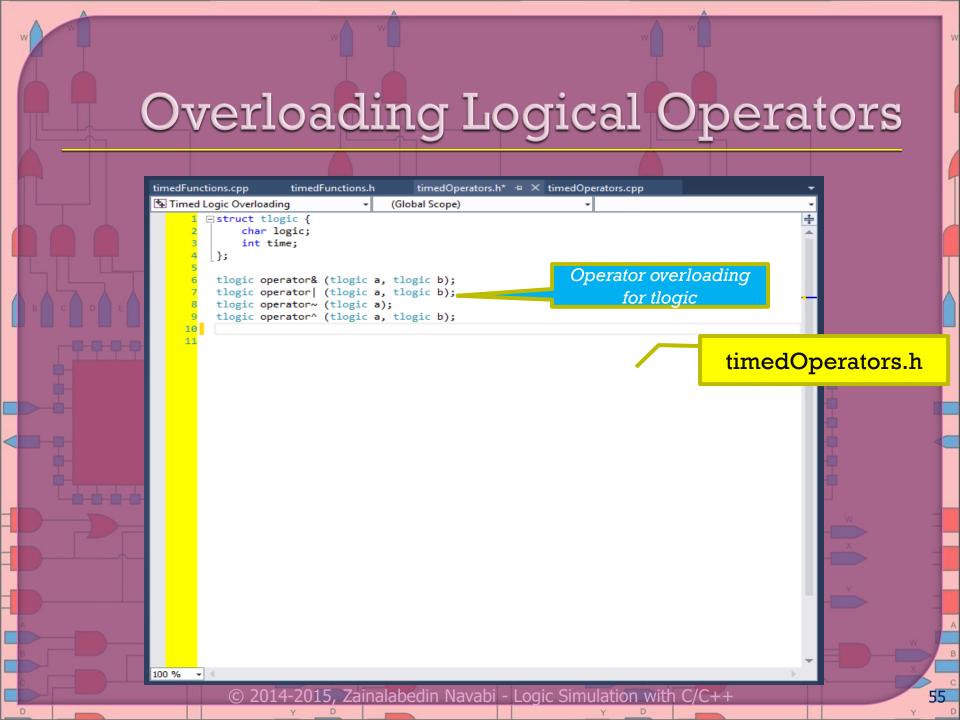

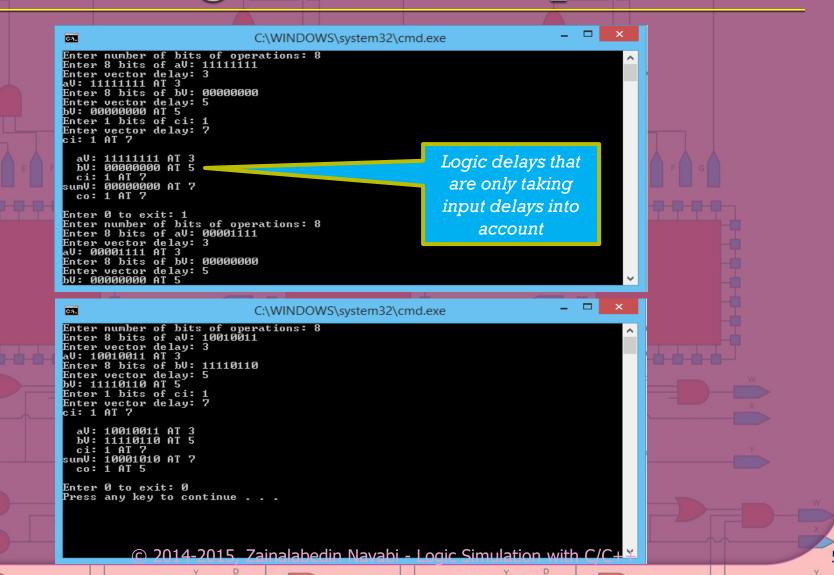

- Overloading logical operators

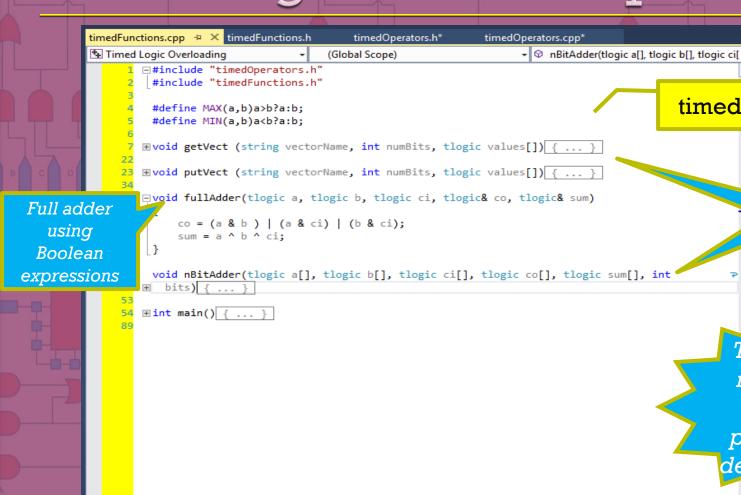

- Using Boolean expressions

- More Functions for Wires and Gates

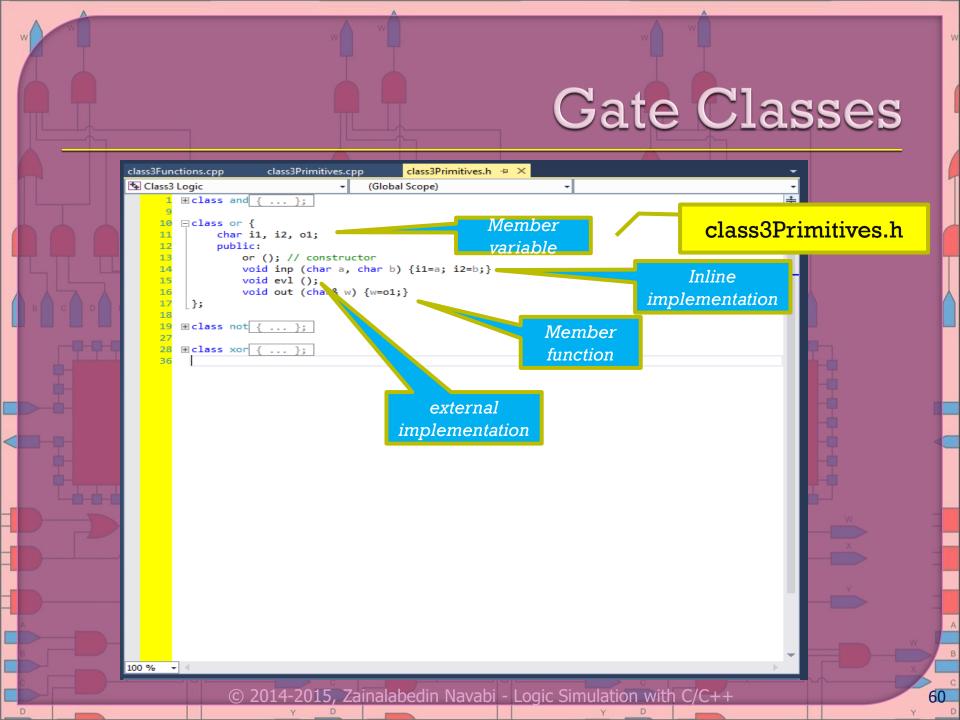

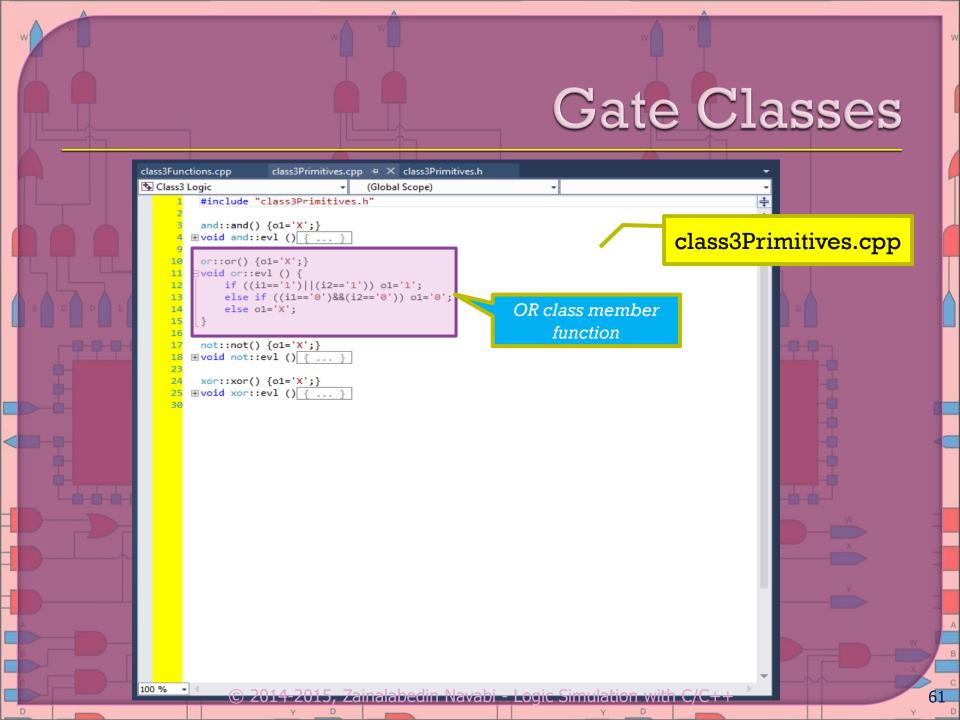

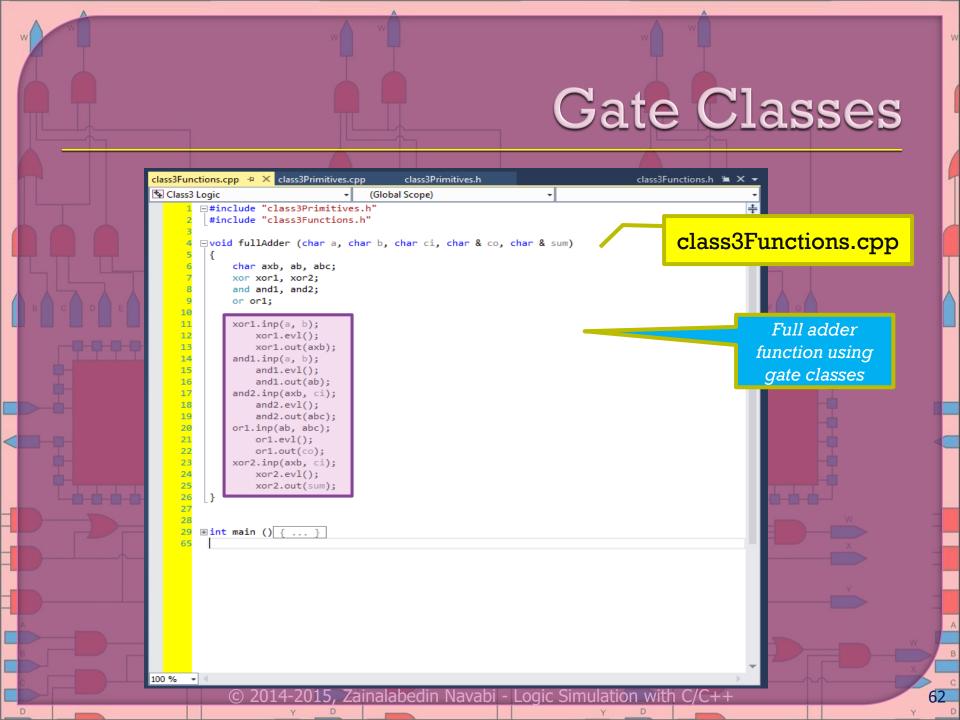

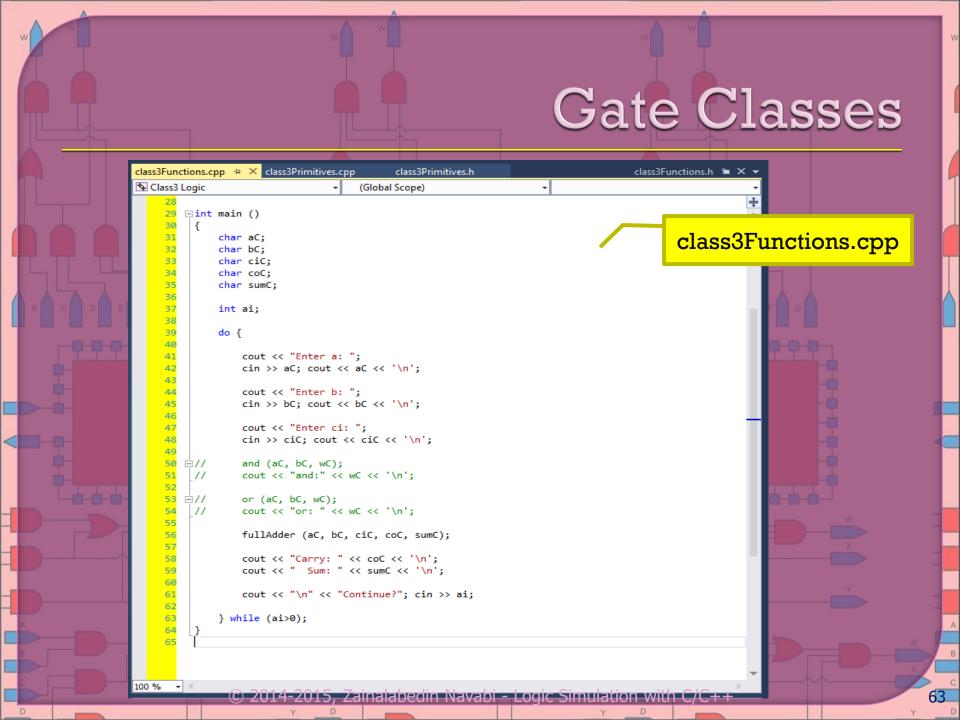

- Gate classes

- Carrier generic modeling

- Compatible scalar and vector

Containing Event Based Timing

To include in wires

To include in gates

Gate-based structures

Gate pointers and objects

Wire and gate vectors

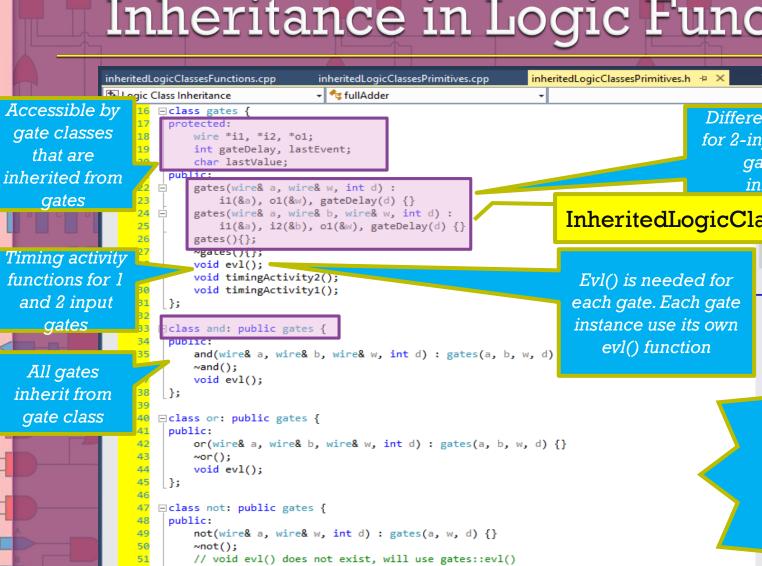

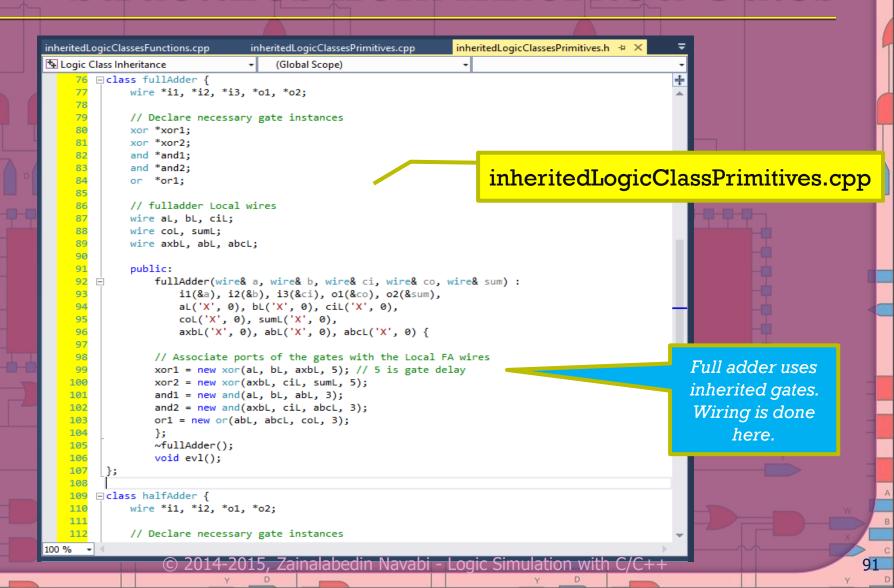

- Inheritance in LogicStructures

- A generic gate definition

Gates to include timing

Building structures from objects

- Hierarchal Modeling of Digital Components

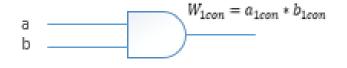

- Wire functionalities

- Gate functionalities

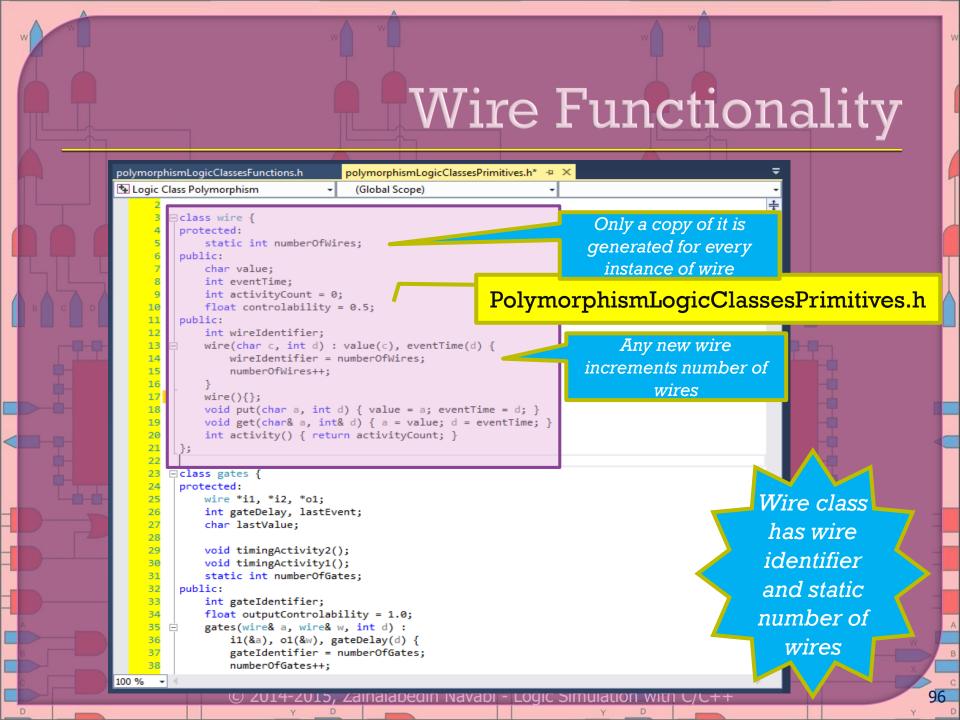

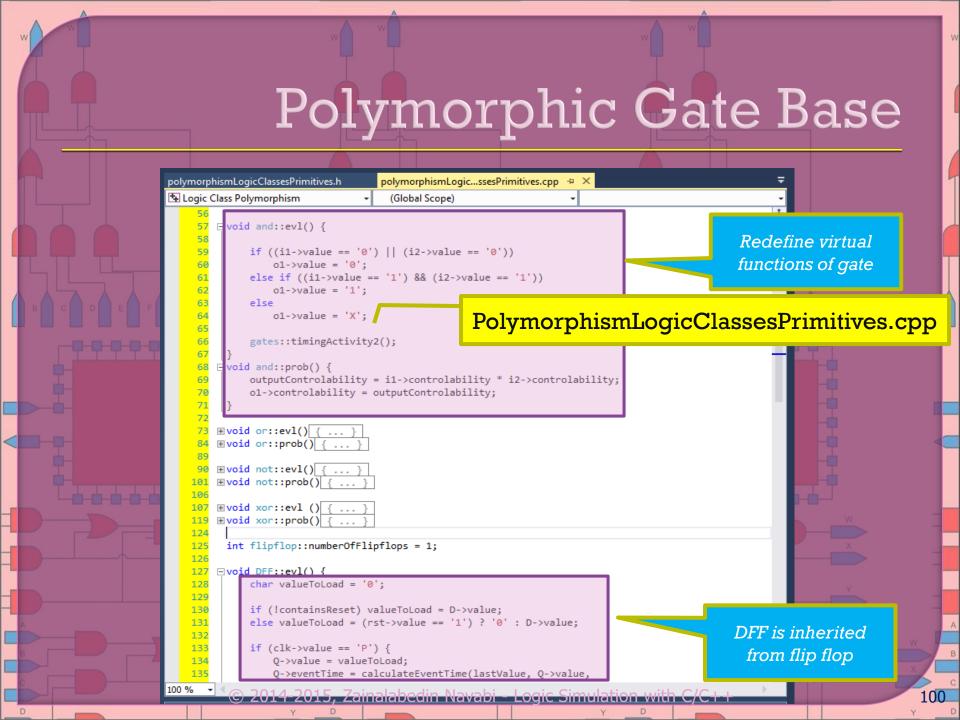

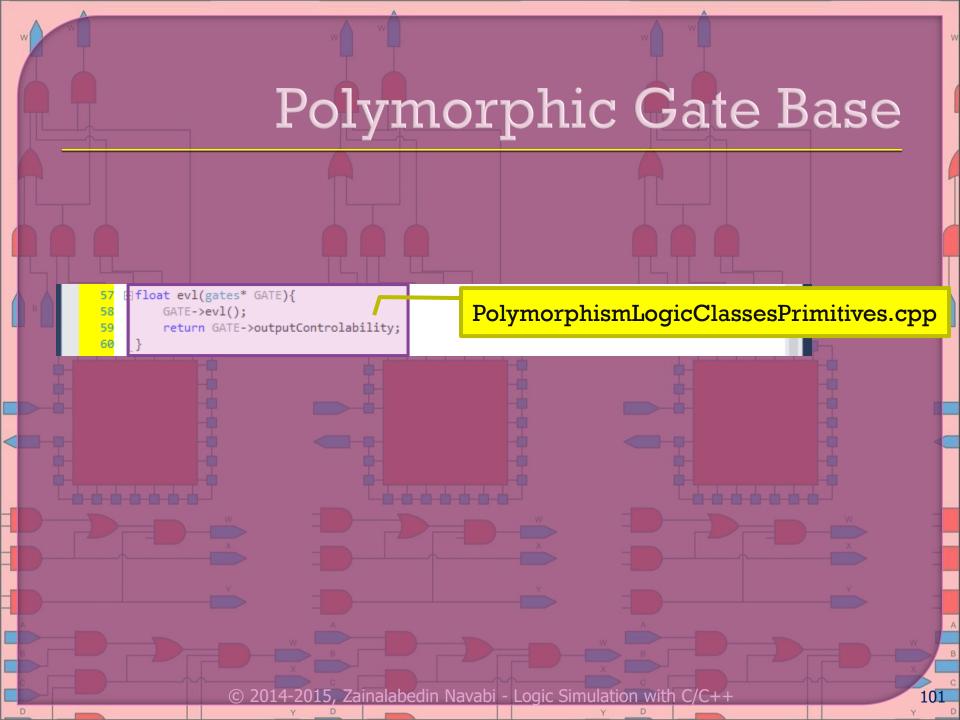

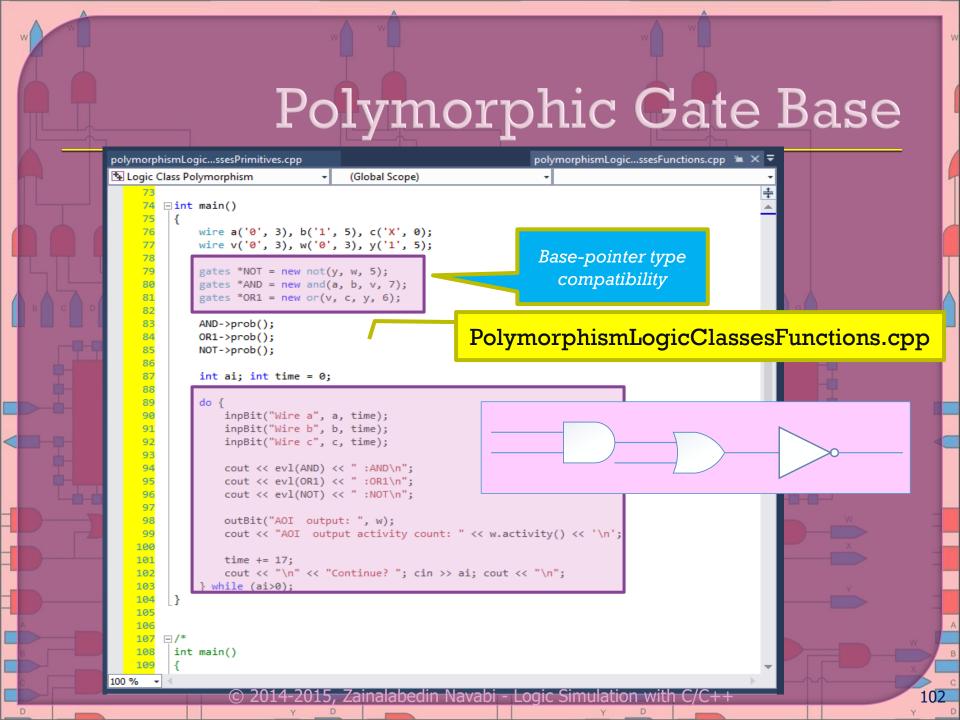

- Polymorphic gate base

- Virtual functions

- Functions overwriting

- Flip flop description hierarchal

- Procedural Languages for Hardware Modeling

- Types and Operators for Logic Modeling

- Basic Logic Simulation

- Logic functions

- Function overloading

- Passing logic functions

- Using default values

- Building higher level structures

- Handling 4-value logic

- Logic vector

- Sequential circuit modeling

- Using pointers for logic

vectors

- Enhanced logic simulation with timing

- Using struct for timing and logic

- Gates that handle timing

- Utility functions

- Timing in logic structures

- Overloading logical operators

- Using Boolean expressions

- More Functions for Wires

and Gates

- Gate classes

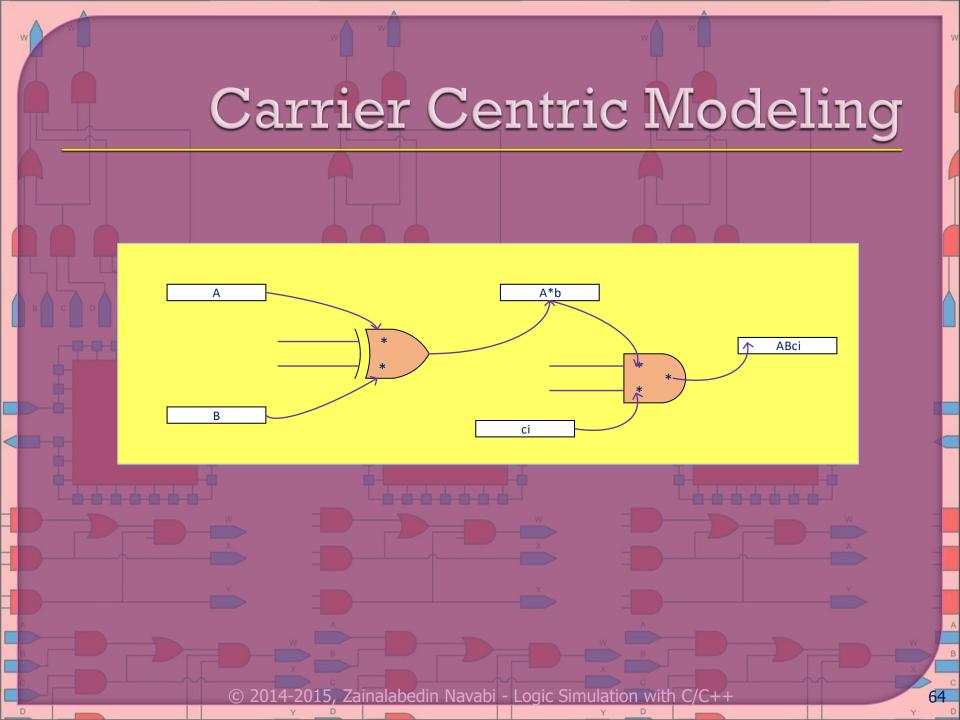

- Carrier centric modeling

- Compatible scalar and vector

© 2014-2015, Zainalabedin Navabi - Logic Simulation with C/C++

- Procedural Languages for Hardware Modeling

- Types and Operators for Logic Modeling

- Basic Logic Simulation

- Logic functions

- Function overloading

- Passing logic functions

- Using default values

- Building higher level structures

- Handling 4-value logic

- Tarianing I value 10g

- Logic vector

- Sequential circuit modeling

- Using pointers for logic

vectors

- Enhanced logic simulation with timing

- Using struct for timing and logic

- Gates that handle timing

- Utility functions

- Timing in logic structures

- Overloading logical operators

- Using Boolean expressions

- More Functions for Wires

and Gates

- Gate classes

- Carrier centric modeling

- Compatible scalar and vector

## Types and Operators for logic Modeling

| Group                                                          | Type names    | Note on size/Precision                    |

|----------------------------------------------------------------|---------------|-------------------------------------------|

| Character Types                                                | Char          | Exactly one byte in size. At least 8 bits |

| Integer Types (signed)                                         | Signed Char   | Same size as char. At least 8 bits        |

|                                                                | Signed Int    | At least 16 bits                          |

| Integer Types (unsigned)                                       | Unsigned Char | Same size as char. At least 8 bits        |

|                                                                | Unsigned Int  | At least 16 bits                          |

|                                                                | Float         |                                           |

| Floating-point Type                                            | Double        | Precision not less than float             |

|                                                                | Long Double   | Precision not less than float             |

| Boolean Type                                                   | Bool          |                                           |

| Void Type                                                      | Void          | No storage                                |

| © 2014-2015, Zainalabedin Navabi - Logic Simulation with C/C++ |               |                                           |

#### Types and Operators for Logic Modeling String Character.cpp + X String Characters (Global Scope) → Operation(string fn, bool in1, bool in2) 17 ⊞bool char2bool (char c) { ... } ⊕bool operation (string fn, bool in1, bool in2) { ... } 32 33 ⊡int main () 34 35 string i1Seq, i2Seq; String Character.cpp 36 string logic; 37 int i, illen, illen, outlen; 38 bool i1=0, i2=0, out=0; 39 hool go(1): while (go) { MIN macro cout << "Enter logic type and input sequences calculating Output the cin >> logic >> i1Seq >> i2Seq; output waveform ilLen=wave (ilSeq); waveform for i2Len=wave (i2Seq); length input sequence outLen = MIN (i1Len, i2Len); string outSeq (outLen, '0'); 47 for (i=0; i<outLen; i++) {</pre> Apply a certain 48 i1 = char2bool (i1Seq[i]); logic operation i2 = char2bool (i2Seq[i]); 49 50 out=operation(logic, i1,i2); outSeq[i] = out ? '1' : '0'; 51 Output the 52 waveform for 53 outLen=wave (outSeq); cout << '\n'; 54 cout << "Enter 0 to end:"; cin >> go; output sequence 55 56 return 0; 57 58 Zainalabedin Navabi - Logic Simulation with

# Types and Operators for Logic Modeling

© 2014-2015, Zainalabedin Navabi - Logic Simulation with C/C++

- Procedural Languages for Hardware Modeling

- Types and Operators for Logic Modeling

- Basic Logic Simulation

- Logic functionsFunction overloading

- · Passing logic functions

- Using default values

- Building higher level structures

- Handling 4-value logic

- Logic vector

- Sequential circuit modeling

- Using pointers for logic

vectors

- Enhanced logic simulation with timing

- Using struct for timing and logic

- Gates that handle timing

- Utility functions

- Timing in logic structures

- Overloading logical operators

- Using Boolean expressions

- More Functions for Wires

and Gates

- Gate classes

- Carrier centric modeling

- Compatible scalar and vector

```

primitives.cpp # X logicGates.cpp

Logic Simulation

(Global Scope)

□bool and (bool a, bool b)

return (a && b);

⊕bool or (bool a, bool b) { ... }

Primitives.cpp

bool not (bool a) { ... }

⊕bool nand (bool a, bool b) { ... }

⊕bool nor (bool a, bool b) { ... }

⊕bool xor (bool a, bool b) { ... }

Functions are

□void and (bool a, bool b, bool& w)

Pass by

w = a &  b;

reference.

overloaded for

Value can be

various type of

woid or (bool a, bool b, bool& w) { ...

returned via

procedure and

⊕void not (bool a, bool& w) { ... }

this argument

⊞void nand (bool a, bool b, bool& w)

vector format

woid nor (bool a, bool b, bool& w) { ... }

⊕void xor (bool a, bool b, bool& w) { ... }

Function passing. Function

□bool logic (bool a, bool b, void (*f) (bool, bool, bool&))

pointer is passed to logic

bool w;

(*f) (a, b, w);

as an argument

return (w);

```

### Building Higher Level Structures

```

primitives.cpp

logicGates.cpp* →

🔁 Logic Simulation

(Global Scope)

1 ∃#include "logicGates.h"

#include "primitives.h"

± /* ... */

17 1 /* ... */

logicgates.cpp

30 ⊟void fullAdder (bool a, bool b, bool ci, bool& co, bool& sum)

bool axb, ab, abc;

axb = logic (a, b, xor); // uses: void xor (bool, bool, bool&)

Use logic function and

35

ab = logic (a, b, and);

36

abc = logic (axb, ci, and);

pass specific function

37

co = logic (ab, abc, or);

38

sum = logic (axb, ci, xor);

□void fullAdder (bool a, bool b, bool ci, bool& co, bool& sum)

bool ab, bc, ac;

ab = and5 (a, b);

bc = and5 (b, ci);

ac = and5 (a, ci);

co = or5 (ab, bc, ac);

sum = xor5 (a, b, ci);

⊞int main () { ... }

Full-adder implementation

```

#### Building Higher Level Structures

```

logicGates.cpp* -

primitives.cpp

Logic Simulation

(Global Scope)

□#include "logicGates.h"

#include "primitives.h"

4 ⊡void fullAdder (bool a, bool b, bool ci, bool& co, bool& sum)

bool axb, ab, abc;

logicgates.cpp

axb = xor(a, b);

ab = and (a, b);

abc = and (axb, ci);

co = or (ab, abc);

sum = xor (axb, ci);

13

14

15 # /* ... */

± /* ... */

± /* ... */

53

54 ⊡int main ()

bool a, b, c, co, sum;

57

59

cout << "Enter a, b, c: "; cin >> a >> b >> c;

Calling full-adder

61

fullAdder (a, b, c, co, sum);

62

cout << "Carry:" << co << " Sum:" << sum << "\n";</pre>

63

65

cout << "\n" << "Continue?"; cin >> a;

} while (a != false);

```

| Value | Description              |  |

|-------|--------------------------|--|

| 0     | Forcing 0 or Pulled 0    |  |

| 1     | Forcing 1 or Pulled 1    |  |

| Z     | Float or High Impedance  |  |

| Χ     | Uninitialized or Unknown |  |

Four-Value Logic System

### Handling 4-value Logic

```

characterPrimitives.cpp + X characterFunctions.cpp

Character Logic

(Global Scope)

#include "characterPrimitives.h"

⊡char and (char a, char b)

if ((a=='0')||(b=='0')) return '0';

else if ((a=='1')&&(b=='1')) return '1';

else return 'X';

⊕ char or (char a, char b) { ... }

⊕ char not (char a) { ... }

⊕char tri (char a, char c) { ... }

⊟ char resolve (char a, char b)

if (a=='Z' || a==b) return b;

33

else if (b=='Z') return a;

else return 'X';

⊕char xor (char a, char b) { ... }

⊡void fullAdder (char a, char b, char ci, char & co, char & sum)

char axb, ab, abc;

axb = xor (a, b);

ab = and (a, b);

abc = and (axb, ci);

co = or (ab, abc);

52

sum = xor (axb, ci);

53

```

CharacterPrimitives.cpp

But the drawback is that we have to generate our own logical functions. This happens one and can easily be reused.

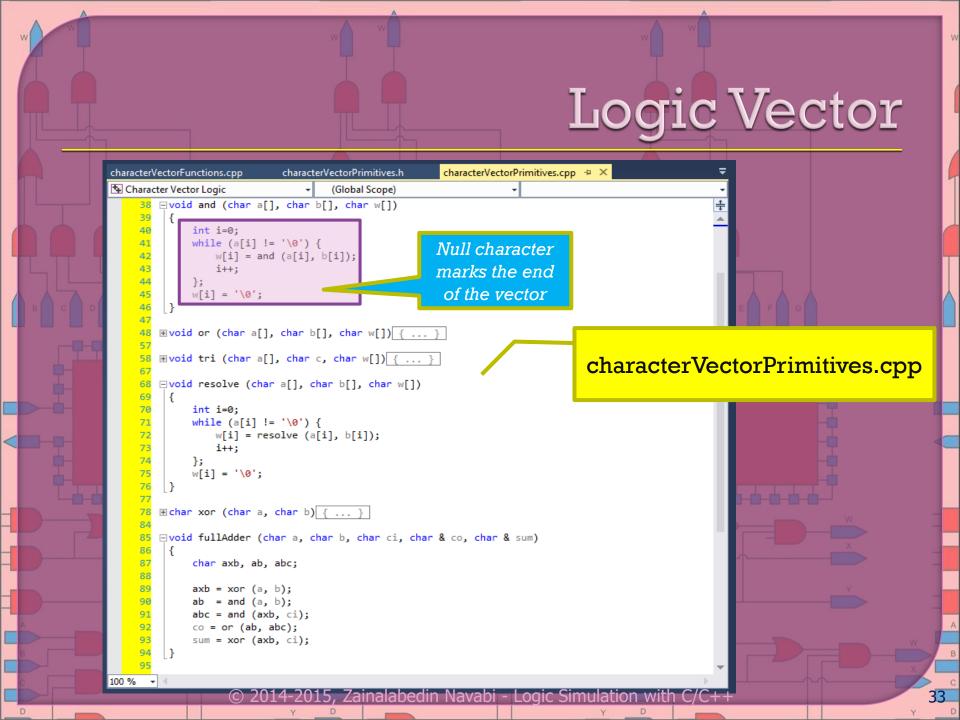

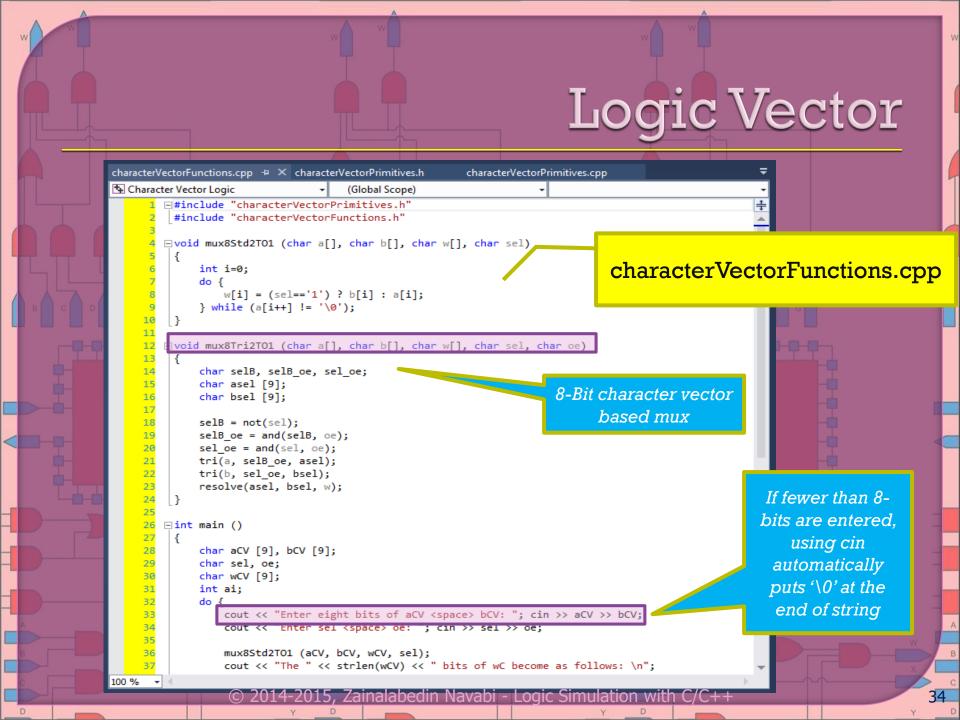

### Logic Vector

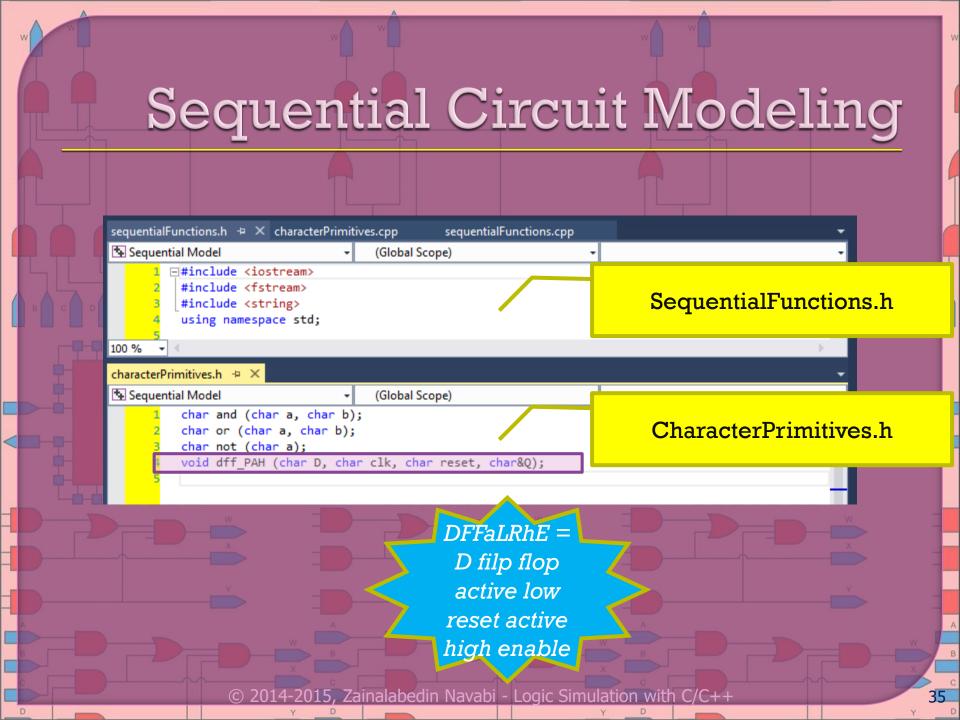

```

characterPrimitives.h

sequentialFunctions.h

characterPrimitives.cpp + X

sequentialFunctions.cpp

🛂 Sequential Model

(Global Scope)

⊕char and (char a, char b)

⊕ char or (char a, char b) { ... }

⊡void dff PAH (char D, char clk, char reset, char&Q)

// Posedge, Asynch, active-Low

CharacterPrimitives.cpp

if (reset=='1') Q='0';

26

else if (clk=='P') Q=D;

D flip flop with

asynchronous reset

```

36

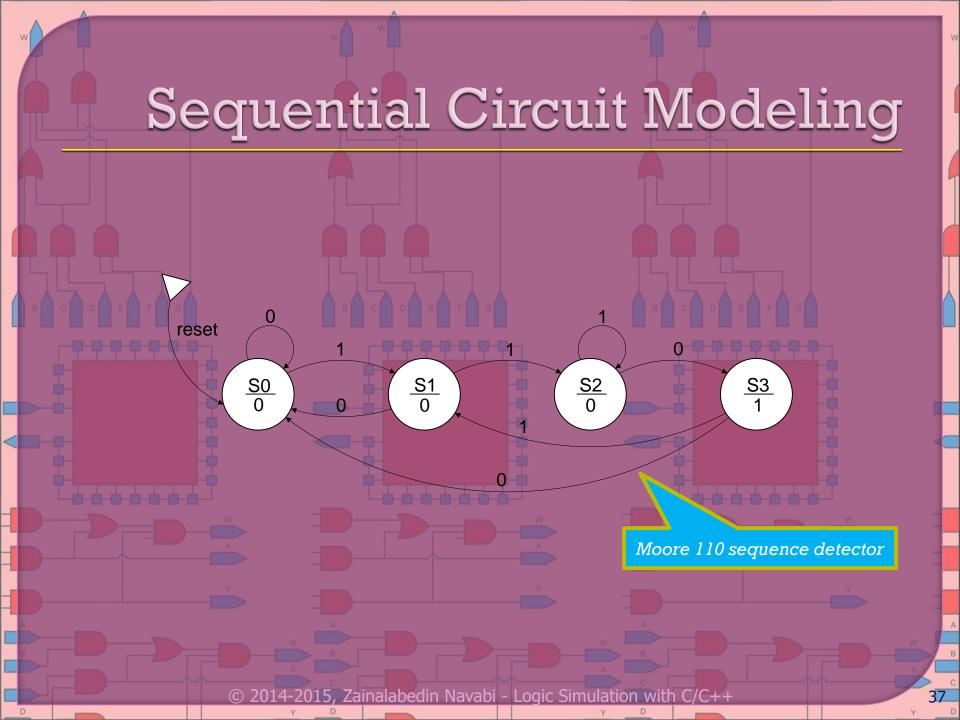

## Sequential Circuit Modeling

```

characterPrimitives.h

characterPrimitives.cpp

sequentialFunctions.cpp + ×

sequentialFunctions.h

Sequential Model

(Global Scope)

1 ∃#include "characterPrimitives.h"

#include "sequentialFunctions.h"

∃int main ()

SequentialFunctions.cpp

string inVec;

string outVec = ",,,,";

char ain('0'), reset, clock;

char Y1('X'), Y0('X'), D1, D0, w;

File handling

12

ifstream finp ( "indata.tst");

13

ofstream fout ("outdata.tst");

14

15

fout << "Inp -> Output, Next state\n";

16

17

do {

18

finp >> inVec;

19

ain = inVec[0];

20

Convert

reset = inVec[1];

21

clock = inVec[2];

22 🖹

// combinational parts in proceduaral fashion

string to

23

// followed by the sequential parts

24

char.

25

D1 = or(and(Y1, Y0), and (ain, Y0));

26

D0 = ain;

Operations

w = and(Y1, not(Y0));

28

29

outVec[0] = w; // These values are after

in char

30

outVec[2] = Y1; // application of the

outVec[3] = Y0; // previous inputs

31

32

fout << outVec+"\n" << inVec << " -> ";

33

34

dff PAH (D1, clock, reset, Y1);

35

dff PAH (D0, clock, reset, Y0);

} while (!finp.eof());

, Zainalabedin Navabi - Logic Simulation with

```

outdata.tst

W and 2 bits of states

Clock by clock output

```

pointerFunctionsFileData.h

pointerPrimitives.h

pointerPrimitives.cpp + × pointerFunctionsFileData.cpp

Pointer Logic File Data

(Global Scope)

#include <iostream>

using namespace std;

void and (char a, char b, char & w)

Overloading AND

W = ((a=='0')||(b=='0')) ? '0':

((a=='1')&&(b=='1')) ? '1':

woid or (char a, char b, char & w) { ... }

pointerPrimitives.cpp

void not (char a, char & w) { ... }

woid tri (char a, char c, char & w) { ... }

woid resolve (char a, char b, char & w) { ... }

oid and (char* a, char* b, char* w)

int i=0;

And with Pointer

and (*(a+i), *(b+i), *(w+i));

Arguments

} while (*(a+i) != '\0');

*(w+i) = '\0';

woid or (char *a, char *b, char *w) { ... }

⊎void not (char *a, char *w) { ... }

woid tri (char *a, char *c, char *w) { ... }

87 ⊡void mux8Std2T01 (char *a, char *b, char *w, char sel)

·2015, Zainalabedin Navabi - Logic Simulation

```

```

pointerFunctionsFileData.h

pointerPrimitives.h

pointerPrimitives.cpp* - > pointerFunctionsFileData.cpp

Pointer Logic File Data

(Global Scope)

resolve(char * a, char * b, char * w)

□ void and (char* a, char* b, char* w)

int i=0:

do {

and (*(a+i), *(b+i), *(w+i));

i++;

} while (*(a+i) != '\0');

*(w+i) = '\0';

pointerPrimitives.cpp

56 ⊞ void not (char *a, char *w) { ... }

74 ⊞void resolve (char *a, char *b, char *w) { ...

84 ⊟void mux8Std2T01 (char *a, char *b, char *w, char sel)

int i=0:

Pointer referencing in

88

*(w+i) = (sel=='1') ? *(b+i) : *(a+i);

89

a multi bit multiplexer

90

} while (*(a+i) != '\0');

91

*(w+i) = '\0';

92

93

void mux8Tri2T01 (char *a, char *b, char *w, char sel, char oe)

95

96

int i=0;

97

98

if (oe == '1') *(w+i) = (sel=='1') ? *(b+i) : *(a+i);

99

else *(w+i) = 'Z';

100

101

} while (*(a+i) != '\0');

102

*(w+i) = '\0';

103

```

```

pointerFunctionsFileData.h

pointerFunctionsFileData.cpp 💠 🗙

pointerPrimitives.h

pointerPrimitives.cpp*

Pointer Logic File Data

(Global Scope)

1 ∃#include "pointerPrimitives.h"

#include "pointerFunctionsFileData.h"

pointerFunctionsFileData.cpp

□int main ()

ifstream inp ("inpdata.tst"); //declare and initialize inp

ofstream out ("outdata.tst"); //declare and initialize out

int ii;

inp >> ii;

11

out << "All vector lengths are " << ii << " bits.\n";

12

13

char sel, oe;

14

char* aC = new char [ii+1];

15

char* bC = new char [ii+1];

16

char* wC = new char [ii+1];

Testing Multiplexers

18

while (inp >> aC >> bC >> sel >> oe)

using ifstream and

19

ofstream

20

out << "Inputs are a, b vectors and sel, oe bits: ";

21

out << aC << " " << bC << " " << sel << " " << oe << "\h":

22

23

mux8Std2T01 (aC, bC, wC, sel);

24

out << "Std Mux: " << wC << '\n';

25

26

mux8Tri2T01 (aC, bC, wC, sel, oe);

27

out << "Tri Mux: " << wC << '\n';

28

29

```

Zainalabedin Navabi - Logic Simulation with

#### outdata.tst × All vector lengths are 8 bits. Inputs are a, b vectors and sel, oe bits: 11001111 11110001 0 0 Std Mux: 11001111 Tri Mux: ZZZZZZZZ Inputs are a, b vectors and sel, oe bits: 11110001 00010101 0 1 Std Mux: 11110001 Tri Mux: 11110001 Inputs are a, b vectors and sel, oe bits: 10101011 11110000 1 0 Std Mux: 11110000 Tri Mux: ZZZZZZZZ Inputs are a, b vectors and sel, oe bits: 11001111 11001100 1 1 Std Mux: 11001100 Tri Mux: 11001100 Inputs are a, b vectors and sel, oe bits: 11110000 11101010 1 1 Std Mux: 11101010 Tri Mux: 11101010 Inputs are a, b vectors and sel, oe bits: 00111110 00110011 0 0 Std Mux: 00111110 Tri Mux: ZZZZZZZZ Inputs are a, b vectors and sel, oe bits: 01110001 00101001 1 0 Std Mux: 00101001 Tri Mux: ZZZZZZZZ Inputs are a, b vectors and sel, oe bits: 00001110 01010101 0 1

Std Mux: 00001110 Tri Mux: 00001110 Outdata.tst

# Logic Simulation with C/C++

- Procedural Languages for Hardware Modeling

- Types and Operators for Logic Modeling

- Basic Logic Simulation

- Logic functions

- Function overloading

- Passing logic functions

- Using default values

- Building higher level structures

- Handling 4-value logic

- Logic vector

- Sequential circuit modeling

- Using pointers for logic

vectors

- Enhanced logic simulation with timing

- Using struct for timing and logic

- Gates that handle timing

- Utility functions

- Timing in logic structures

- Overloading logical operators

- Using Boolean expressions

- More Functions for Wires

and Gates

- Gate classes

- Carrier centric modeling

- Compatible scalar and vector

#### Gates that Handle Timing

```

timedPrimitives.cpp + X timedFunctions.h.

timedFunctions.cpp

timedPrimitives.h

Timed Logic Structs

(Global Scope)

#include "timedPrimitives.h"

⊟tlogic and (tlogic a, tlogic b, int delay)

tlogic tl;

if ((a.logic=='0')||(b.logic=='0')) {

tl.logic = '0';

if (a.logic=='0') tl.time = a.time + delay;

else tl.time = b.time + delay;

10

11

else if ((a.logic=='1')&&(b.logic=='1')) {

12

tl.logic = '1';

13

if (a.time > b.time) tl.time = a.time + delay;

14

else tl.time = b.time + delay;

15

16

else {

17

tl.logic = 'X';

18

if (a.logic != '1') tl.time = a.time + delay;

19

else tl.time = b.time + delay;

20

21

return tl;

22

23

tlogic not (tlogic a, int delay) {

55

∃tlogic xor (tlogic a, tlogic b, int delay)

56

tlogic tl;

58

if (a.logic==b.logic) tl.logic = '0';

59

else tl.logic = '1';

60

if (a.time > b.time) tl.time = a.time + delay;

61

else tl.time = b.time + delay;

62

return tl;

```

timedPrimitives.cpp

And logic function with timing

A more accurate delay propagation requires the gate function to be aware of its previous output value

Zainalabedin Navabi - Logic Simulation with

```

timedFunctions.cpp + X timedPrimitives.h

timedPrimitives.cpp

timedFunctions.h

Timed Logic Structs

(Global Scope)

59 ⊡int main ()

tlogic *aV, *bV, *ci, *co, *sumV;

61

62

63

int bits, go(1);

64

while (go)

67

cout << "Enter number of bits of operations: "; cin >> bits;

68

aV = new tlogic[bits];

bV = new tlogic[bits];

70

ci = new tlogic[1];

co = new tlogic[1];

sumV = new tlogic[bits];

73

74

getVect ("aV", bits, aV); putVect ("aV", bits, aV);

getVect ("bV", bits, bV); putVect ("bV", bits, bV);

getVect ("ci", 1, ci); putVect ("ci", 1, ci);

cout << "\n":

78

nBitAdder (aV, bV, ci, co, sumV, bits); // calculates all propagations

80

81

putVect (" aV", bits, aV); putVect (" bV", bits, bV);

82

putVect (" ci", 1, ci);

putVect ("sumV", bits, sumV); putVect (" co", 1, co);

83

84

85

delete [] aV;

86

delete [] bV;

87

delete [] ci;

88

delete [] co;

89

delete [] sumV;

91

cout << "\nEnter 0 to exit: "; cin >> go;

```

timedFunctions.cpp

Char based adder with tlogic

5

#### Overloading Logical Operators

```

timedOperators.cpp* + ×

timedFunctions.cpp

timedFunctions.h

timedOperators.h*

Timed Logic Overloading

(Global Scope)

#include "timedOperators.h"

±tlogic operator& (tlogic a, tlogic b) { ... }

⊟tlogic operator~ (tlogic a)

47

tlogic tl;

48

if (a.logic=='1') tl.logic = '0';

else if (a.logic=='0') tl.logic = '1';

else tl.logic=='X';

50

timedOperators.cpp

51

tl.time = a.time:

52

return tl:

53

54

55

∃tlogic operator^ (tlogic a, tlogic b)

56

57

tlogic tl:

58

if (a.logic==b.logic) tl.logic = '0';

59

else tl.logic = '1';

60

if (a.time > b.time) tl.time = a.time;

61

else tl.time = b.time;

62

return tl;

64

Overloaded

Operators

for struct

type

```

© 2014-2015, Zainalabedin Navabi - Logic Simulation with C/C++

56

#### Using Boolean Expressions

timedFunction.cpp

Full adder considers logic and timing

There are no inside wires to propagate delay values

57

#### Using Boolean Expressions

# Logic Simulation with C/C++

- Procedural Languages for Hardware Modeling

- Types and Operators for Logic Modeling

- Basic Logic Simulation

- Logic functions

- Function overloading

- Passing logic functions

- Using default values

- Building higher levelstructures

- Handling 4-value logic

- Logic vector

- Sequential circuit modeling

- Using pointers for logic

vectors

- Enhanced logic simulation with timing

- Using struct for timing and logic

- Gates that handle timing

- Utility functions

- Timing in logic structures

- Overloading logical operators

- Using Boolean expressions

- More Functions for Wires and Gates

- Gate classes

- Carrier centric modeling

- Compatible scalar and vector

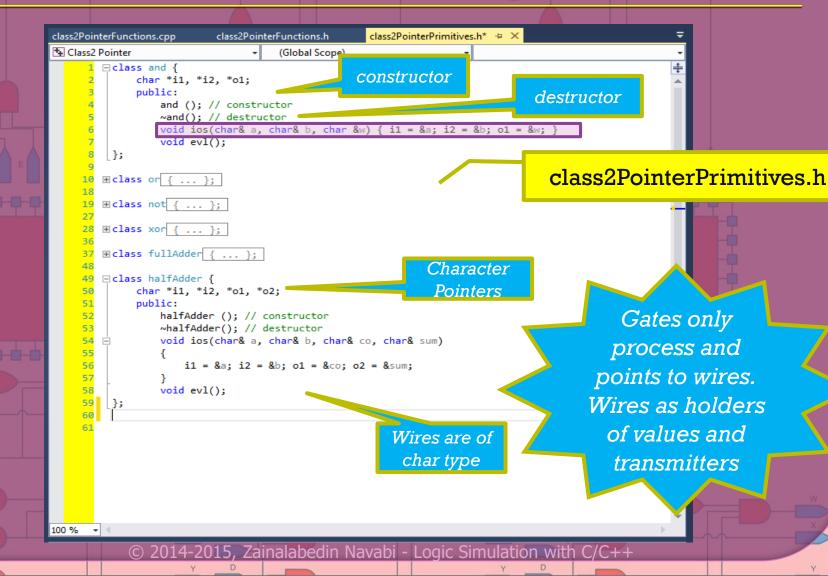

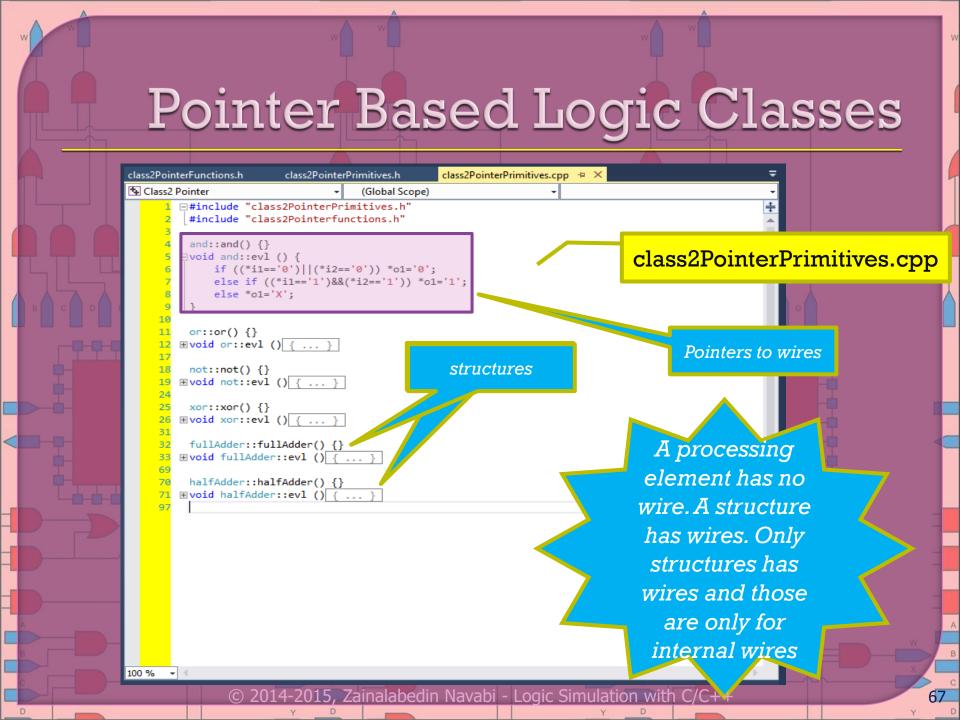

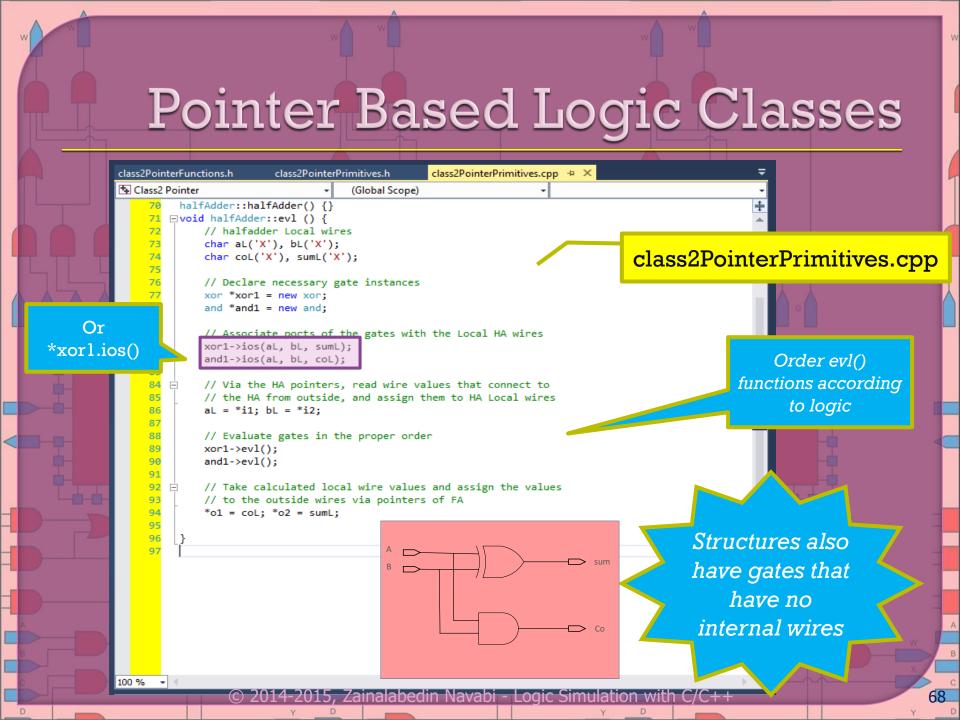

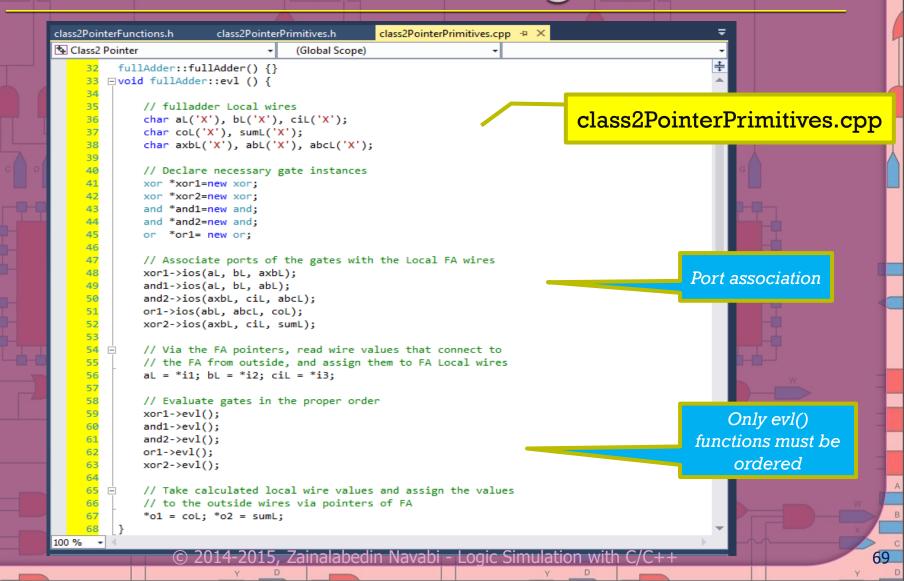

#### Pointer Based Logic Classes

- Classes do not hold values. Since the lines are just pointers, someone else has to declare them and allocate them.

- evl and out are combined and evl does both. Actually, since

the outputs are pointers they will just be updated by evl.

Every invocation of evl puts the internal output values on

the evl return value.

- Destructor is introduced.

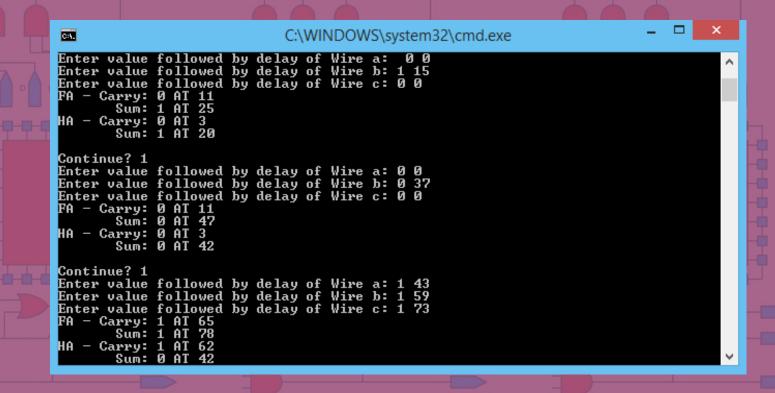

### Pointer Based Logic Classes

#### Pointer Based Logic Classes

```

class2PointerPrimitives.cpp

class2PointerPrimitives.h

class2PointerFunctions.cpp + X

Class2 Pointer

(Global Scope)

□#include "class2PointerPrimitives.h"

#include "class2PointerFunctions.h"

∃int main ()

class2PointerFunctions.cpp

char aC('X'), bC('X'), ciC('X'), coCF('X'), sumCF('X'),

coCH('X'), sumCH('X');

fullAdder *FA:

FA=new fullAdder():

halfAdder *HA;

HA=new halfAdder();

FA->ios(aC, bC, ciC, coCF, sumCF);

HA->ios(aC, bC, coCH, sumCH);

16

int ai:

Shows main for full

18

19

adder and half

20

cout << "Enter a: "; cin >> aC;

cout << "Enter b: "; cin >> bC;

adder functions

cout << "Enter ci: "; cin >> ciC;

FA->evl();

HA->evl();

cout << "FA - Carry: " << coCF << "; Sum: " << sumCF << '\n';</pre>

cout << "HA - Carry: " << coCH << "; Sum: " << sumCH << '\n';

30

cout << "\n" << "Continue?"; cin >> ai;

31

} while (ai>0);

33

```

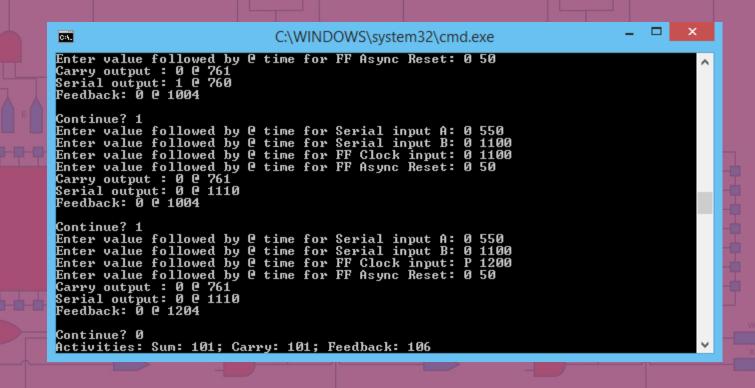

```

delay

```

**ActivityCount** to carry power consumption

```

int activityCount=0;

wire(char c, int d) : value(c), eventTime(d)

wire(){};

void put(char a, int d) { value = a; eventTime = d; }

void get(char& a, int& d) { a = value; d = eventTime; }

int activity() { return activityCount; }

};

class and {

18

wire *i1, *i2, *o1;

19

int gateDelay, lastEvent;

20

char lastValue:

21

public:

22

and(wire& a, wire& b, wire& w, int d):

i1(&a), i2(&b), o1(&w), gateDelay(d) {};

24

```

⊞class or { ... }; ⊕class not { ... };

~and():

void evl();

⊕class xor { ... }; □class dff ar {

25

60

wire \*D, \*clk, \*R, \*Q; int clkQDelay, rstQDelay; int lastEvent; // last time output changed

Wires have constructor for value and event time.

> They have put and get for accessing their value and event time

> > Declare wire to contain more information than just logic value

.5, Zainalabedin Navabi -

Wires have

access

function to

activityCou

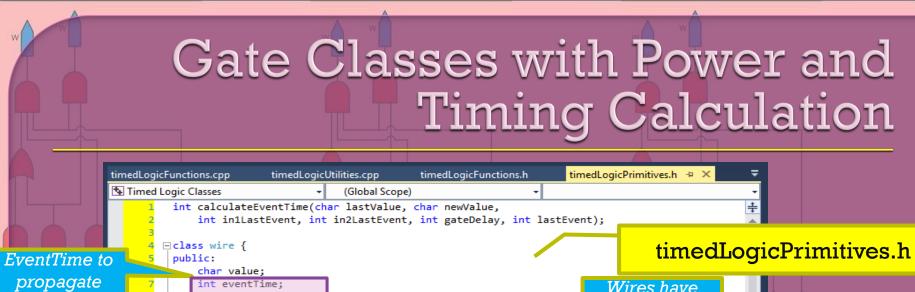

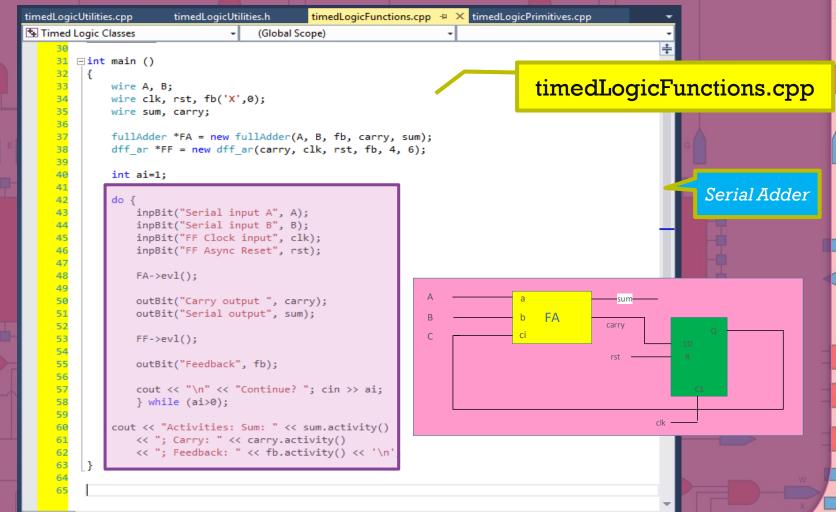

# Gate Classes with Power and Timing Calculation

timedLogicFunctions.h

Xor

constructor

just ties port

pointers to

wires

65 Ė dff ar(wire& d, wire& c, wire& r, wire& q, int dC, int dR): D(&d), clk(&c), R(&r), Q(&q), clkQDelay(dC), rstQDelay(dR) {}; 67 ~dff ar(); 68 void evl(); 69 }; 70 // Structures based on above primitives begin here Ol is a □ class fullAdder { pointer. This wire \*i1, \*i2, \*i3, \*o1, \*o2; pointer is tied 76 // Declare necessary gate instances to pointer of w 77 xor \*xor1; xor \*xor2:

timedLogicFunctions.cpp

48 ⊟class xor {

public:

58 ⊟class dff ar {

wire \*i1, \*i2, \*o1;

char lastValue = 'X';

wire \*D, \*clk, \*R, \*Q;

int clkODelay, rstODelay;

~xor();

void evl();

char lastValue;

public:

and \*and1; and \*and2; or \*or1;

// fulladder Local wires

wire aL, bL, ciL;

int gateDelay, lastEvent;

Timed Logic Classes

50

52

55

56 };

57

60

62

63 64

82 83

84

timedLogicUtilities.cpp

int lastEvent; // last time output changed

(Global Scope)

xor(wire& a, wire& b, wire& w, int d) : i1(&a), i2(&b), o1(&w

```

timedLogicPrimitives.h

```

timedLogicPrimitives.h +

## Gate Classes with Power and Timing Calculation

### Gate Classes with Power and Timing Calculation

```

timedLogicFunctions.cpp

timedLogicFunctions.h

timedLogicPrimitives.h + X

timedLogicUtilities.cpp

Timed Logic Classes

(Global Scope)

105

□class halfAdder {

106

107

wire *i1, *i2, *o1, *o2;

timedLogicPrimitives.h

108

109

// Declare necessary gate instances

110

xor *xor1;

111

and *and1:

112

// halfadder Local wires

113

114

wire aL, bL;

half adder constructor

115

wire coL, sumL;

116

ties ports of the full

117

public:

adder to external wires

118 F

halfAdder(wire& a, wire& b, wire& co, wire& sum) :

119

i1(&a), i2(&b), o1(&co), o2(&sum),

and initialize internal

120

al('X', 0), bl('X', 0), col('X', 0), suml('X', 0){

121

wires

122

// Associate ports of the gates with the Local HA wires

123

xor1 = new xor(aL, bL, sumL, 5);

124

and 1 = \text{new and}(aL, bL, coL, 3);

125

Then It has evl()

~halfAdder();

126

127

void evl();

function that call

128

};

gate classes in

129

130

proper order

```

Zainalabedin Navabi - Logic Simulation with

cout << wireName << ": " << value << " @ " << time << "\n":

14

valtim.get(value, time);

outbit to get time and value for wires

### Gate Classes with Power and Timing Calculation

```

timedLogicUtilities.cpp

timedLogicPrimitives.cpp + X

timedLogicUtilities.h

timedLogicFunctions.cpp

Timed Logic Classes

→ fullAdder

- Ø evl()

∃#include "timedLogicPrimitives.h"

#include "timedLogicFunctions.h"

#define MAX(a,b) ((a>b)?a:b)

timedLogicPrimitives.cpp

int calculateEventTime(char lastValue, char newValue,

int in1LastEvent, int in2LastEvent, int gateDelay, int lastEvent){

if (lastValue == newValue)

If output has changed, the

return lastEvent:

last event time on output is

else

return gateDelay + MAX (in1LastEvent, in2LastEvent);

the larger of the inputs

plus gate delay

15

int calculateEventTime(char lastValue, char newValue,

16

int in1LastEvent, int gateDelay, int lastEvent){

17

if (lastValue == newValue)

18

19

return lastEvent:

20

else

return gateDelay + in1LastEvent;

22

24

Evoid and::evl () {

25

26

if ((i1->value == '0') || (i2->value == '0'))

o1->value = '0';

28

else if ((i1->value == '1') && (i2->value == '1'))

29

o1->value = '1';

30

else

31

o1->value='X':

32

33

o1->eventTime = calculateEventTime(lastValue, o1->value,

34

i1->eventTime, i2->eventTime, gateDelay, lastEvent);

35

36

o1->activityCount = i1->activityCount + i2->activityCount +

((lastValue == o1->value) ? 0 : 1);

© 2014-2015, Zainalabedin Navabi - Logic Simulation with C/C++

```

### Gate Classes with Power and Timing Calculation

```

timedLogicUtilities.cpp

timedLogicUtilities.h

timedLogicPrimitives.cpp +

timedLogicFunctions.cpp

Timed Logic Classes

- → fullAdder

+ Ø evl()

81 ⊟void xor::evl () {

82

if ((i1->value == 'X') || (i2->value == 'X') ||

(i1->value == 'Z') || (i2->value == 'Z'))

Logic part

o1->value = 'X':

else if (i1->value==i2->value)

o1->value='0':

88

else

o1->value='1';

Event

o1->eventTime = calculateEventTime(lastValue, o1->value,

part(timing)

i1->eventTime, i2->eventTime, gateDelay, lastEvent);

o1->activityCount = i1->activityCount + i2->activityCount +

((lastValue == o1->value) ? 0 : 1);

Activity

Retain last

part(power)

lastEvent = o1->eventTime;

lastValue = o1->value:

event and last

100

value

void dff ar::evl() {

if (R->value == '1') {

0->value = '0';

Logic part

Q->eventTime = calculateEventTime(lastValue, Q->value,

R->eventTime, rstQDelay, lastEvent);

else if (clk->value == 'P') {

Event

Q->value = D->value;

Q->eventTime = calculateEventTime(lastValue, Q->value,

part(timing)

clk->eventTime, clkQDelay, lastEvent);

Q->activityCount = D->activityCount + 2 +

Activity

((lastValue == Q->value) ? 0 : 3);

part(power)

```

timedLogicPrimitives.cpp

77

### Gate Classes with Power and Timing Calculation

```

timedLogicFunctions.h

timedLogicPrimitives.cpp + X

timedLogicFunctions.cpp

timedLogicPrimitives.h

Timed Logic Classes

(Global Scope)

→

□ calculateEventTime(char lastValue, char)

120

121

□void fullAdder::evl () {

122

123

// Via the FA pointers, read wire values that connect to

// the FA from outside, and assign them to FA Local wires

124

125

aL = *i1; bL = *i2; ciL = *i3;

126

127

// Evaluate gates in the proper order

128

xor1->evl();

129

and1->evl();

130

and2->evl():

or1->evl();

131

132

xor2->evl();

133

134

// Take calculated local wire values and assign the values

135

// to the outside wires via pointers of FA

136

*o1 = coL; *o2 = sumL;

137

138

139

□void halfAdder::evl () {

140

141

// Via the HA pointers, read wire values that connect to

142

// the HA from outside, and assign them to HA Local wires

aL = *i1; bL = *i2;

143

144

145

// Evaluate gates in the proper order

xor1->evl();

146

147

and1->evl();

148

149

// Take calculated local wire values and assign the values

150

// to the outside wires via pointers of FA

*o1 = coL; *o2 = sumL;

152

153

```

timedLogicPrimitives.cpp

# Gate Classes with Power and Timing Calculation

15, Zainalabedin Navabi - Logic Simulation with

## Gate Classes with Power and Timing Calculation

### Gate Classes with Power and Timing Calculation

#### Wire and Gate Vectors

```

timedVectorLogicFunctions.cpp

timedVectorLogicUtilities.cpp

timedVectorLogicPrimitives.h +

→ dalfAdder

- 👂 evl()

Timed Vector Logic Classes

134

class wireV {

135

public:

timedVectorLogicPrimitives.h

136

char* value;

137

int n; //Bits

138

int eventTime;

139

int activityCount = 0;

Main

140

141

wireV(string v, int d, int size);

difference

142

wireV(){};

with wire

143

~wireV(){};

void put(string a, int d);

144

145

void get(string& a, int& d);

146

int activity() { return activityCount

ast value for

147

Wire vector has an

148

timing

149

☐ class andV {

150

wireV *i1, *i2, *o1;

event time for a

calculation

151

int gateDelay, lastEvent;

152

char* lastValue;

group of wires and

153

public:

154

andV(wireV& a, wireV& b, wireV& w, int d):

155

an activityCount for

i1(&a), i2(&b), o1(&w), gateDelay(d) {

156

lastValue = new char[w.n+1];

157

a group of wires.

158

~andV(){};

159

void evl();

This model is not

160

1:

161

accurate since all

162

□class orV {

163

wireV *i1, *i2, *o1;

164

int gateDelay, lastEvent;

individual wires

165

char* lastValue;

166

public:

are treated the

167

orV(wireV& a, wireV& b, wireV& w, int d) :

168

i1(&a), i2(&b), o1(&w), gateDelay(d) {

lastValue = new char[w.n + 1];

same

© 2014-2015, Zainalabedin Navabi - Logic Simulation with C/C++

```

#### Wire and Gate Vectors

```

timedVectorLogicUtilities.cpp 😕 🗙 timedVectorLogicPrimitives.h

Timed Vector Logic Classes

(Global Scope)

→ InpBit(string wireName, wireV & valtim)

#include "timedVectorLogicUtilities.h"

□void inpBit(string wireName, wire& valtim) {

char value;

timedVectorLogicPrimitives.h

int time;

cout << "Enter value followed by @ time for " << wireName << "

cin >> value: cin >> time:

valtim.put(value, time);

Utility for

□void outBit(string wireName, wire valtim) {

12

char value;

individual

int time:

valtim.get(value, time);

wires

cout << wireName << ": " << value << "@ " << time << "\n";

□void inpBit(string wireName, wireV& valtim) {

19

string value;

20

int time;

21

cout << "Enter value followed by @ time for " << wireName << ": ";

cin >> value; cin >> time;

23

valtim.put(value, time);

24

Utility for

□void outBit(string wireName, wireV valtim) {

string value;

arrays

int time;

29

valtim.get(value, time);

cout << wireName << ": " << value << " @ " << time << "\n";

30

100 %

© 2014-2015, Zainalabedin Navabi - Logic Simulation with C/C++

```

```

timedVectorLogicPrimitives.cpp* + X

timedVectorLogicUtilities.h

timedVectorLogicUtilities.cpp

wireV::wireV(string v, int d, int size) : eventTime(d), n(size)

157

158

value = new char[n + 1];

159

v.resize(n, 'X');

timedVectorLogicPrimitives.cpp

160

for (i = 0; i < n; i++){ *(i + value) = v.at(i); };

161

*(n + value) = '\0';

162

□void wireV::put(string a, int d){

164

int i;

compatible with the c++

165

eventTime = d;

166

a.resize(n, '0');

predefined string class

167

for (i = 0; i < n; i++){ *(i + value) = a.at(i);};

168

□void wireV::get(string& a, int& d){

169

170

int i;

171

d = eventTime;

172

a.resize(n, '0');

173

for (i = 0; i < n; i++){ a.at(i) = *(i + value); };

174

175

176

□void andV::evl() {

177

int i = 0;

178

while (i1->value[i] != '\0'){

179

if (((i1->value[i]) == '0') || ((i2->value[i]) == '0'))

180

181

o1->value[i] = '0';

182

else if ((i1->value[i] == '1') && (i2->value[i] == '1'))

183

o1->value[i] = '1';

184

else

185

o1->value[i] = 'X';

186

i++;

187

188

189

190 ⊟void orV::evl() {

int i = 0;

while (i1->value[i] != '\0'){

192

```

Adding \0 to make it

Evl() function for wireV. Since they are clusters, individual delay and power do not apply

#### Wire and Gate Vectors

```

timedVectorLogicFunctions.cpp + ×

timedVectorLogicUtilities.cpp

timedVectorLogicPrimitives.cpp*

Timed Vector Logic Classes

(Global Scope)

65 ⊡int main ()

66

67

wireV aWV("10101111", 0, 8), bWV("00110000", 0, 8), cWV("00001111", 0, 8),

68

wWV("00001111", 0, 8), yWV("XXXX0000", 0, 8);

69

andV *AND = new andV(aWV, bWV, wWV, 0);

orV *OR = new orV(aWV, bWV, yWV, 0);

int ai;

do {

inpBit("Wire a", aWV);

inpBit("Wire b", bWV);

timedVectorLogicFunctions.cpp

78

AND->evl();

OR->evl();

81

82

outBit("Wire w AND result", wWV);

83

outBit("Wire w OR result", yWV);

84

85

cout << "\n" << "Continue? "; cin >> ai;

Vectors have

86

character pointer

87

} while (ai>0);

88

instead of char

```

Zainalabedin Navabi - Logic Simulation with C/C+-

85

- Containing Event Based

Timing

- To include in wires

- To include in gates

- Gate-based structures

- Gate pointers and objects

- Wire and gate vectors

- Inheritance in LogicStructures

- A generic gate definition

- Gates to include timing

- Building structures from objects

- Hierarchal Modeling of Digital Components

- Wire functionalities

- Gate functionalities

- Polymorphic gate base

- Virtual functions

- Functions overwriting

- Flip flop description hierarchal

### Inheritance in Logic Functions

Different constructors for 2-input and 1-input gates and no initailization

InheritedLogicClassPrimitives.h

An inherited class that

does not have its own evl() can depend on the base

class

#### Inheritance in Logic Functions

```

inheritedLogicClassesPrimitives.cpp + X inheritedLogicClassesPrimitives.h

inheritedLogicClassesFunctions.cpp

Logic Class Inheritance

- | ∅ evl()

#define MAX(a,b) ((a>b)?a:b)

int calculateEventTime(char lastValue, char newValue,

int in1LastEvent, int in2LastEvent, int gateDelay, int lastEvent){

if (lastValue == newValue)

return lastEvent;

else

12

return gateDelay + MAX (in1LastEvent, in2LastEvent);

13

15

int calculateEventTime(char lastValue, char newValue,

16

int in1LastEvent, int gateDelay, int lastEvent) { ... }

23

24

□void gates::evl() { // inverts its input 1

25

26

if (i1->value == '0')

InheritedLogicClassPrimitives.cpp

o1->value = '1';

28

else if (i1->value == '1')

29

o1->value = '0';

else

31

o1->value = 'X';

32

33

gates::timingActivity1();

34

35

□void gates::timingActivity2() {

36

37

o1->eventTime = calculateEventTime(lastValue, o1->value,

38

i1->eventTime, i2->eventTime, gateDelay, lastEvent);

39

40

o1->activityCount = i1->activityCount + i2->activityCount +

41

((lastValue == o1->value) ? 0 : 1);

43

lastEvent = o1->eventTime;

44

lastValue = o1->value;

.5, Zainalabedin Navabi - Logic Simulation

```

#### Inheritance in Logic Functions

```

inheritedLogicClassesFunctions.cpp

inheritedLogicClassesPrimitives.cpp + X inheritedLogicClassesPrimitives.h

- Ø evl()

Logic Class Inheritance

- → dff ar

Calculate output

57 ⊡void and::evl() {

value and call

if ((i1->value == '0') || (i2->value == '0'))

timing activity at

o1->value = '0';

else if ((i1->value == '1') && (i2->value == '1'))

gates

o1->value = '1';

else

o1->value = 'X';

gates::timingActivity2();

⊕void or::evl() { ... }

inheritedLogicClassPrimitives.cpp

/*void not::evl () { // uses gates::evl(); }*/

⊡void xor::evl () {

84

85

if ((i1->value == 'X') || (i2->value == 'X') ||

(i1->value == 'Z') || (i2->value == 'Z'))

86

No evl() for

87

o1->value = 'X';

else if (i1->value==i2->value)

88

not to use

o1->value='0';

that of

90

else

91

o1->value='1';

gates

92

93

gates::timingActivity2();

94

95

□void dff ar::evl() {

97

if (R->value == '1') {

98

99

0->value = '0';

100

0->eventTime = calculateEventTime(lastValue, 0->value,

R->eventTime, rstQDelay, lastEvent);

101

102

103

else if (clk->value == 'P') {

```

-2015, Zainalabedin Navabi - Logic Simulation with

#### Structures from Inherited Gates

#### Inheritance in Logic Structures

```

inheritedLogicClassesFunctions.cpp

inheritedLogicClassesPrimitives.cpp

inheritedLogicClassesPrimitives.h

- → xor

Logic Class Inheritance

- | @ evI()

□void fullAdder::evl () {

118

119 E

// Via the FA pointers, read wire values that connect to

120

// the FA from outside, and assign them to FA Local wires

121

aL = *i1; bL = *i2; ciL = *i3;

122

and1->timingActivity1();

inheritedLogicClassPrimitives.cpp

123

// Evaluate gates in the proper order

xor1->evl();

125

and1->evl();

126

and2->evl();

127

or1->evl();

Evl() of full

128

xor2->evl();

129

adder order the

130

// Take calculated local wire values and assign the values

131

// to the outside wires via pointers of FA

gates

132

*o1 = coL; *o2 = sumL;

134

□void halfAdder::evl () {

136

137

// Via the HA pointers, read wire values that connect to

138

// the HA from outside, and assign them to HA Local wires

aL = *i1; bL = *i2;

// Evaluate gates in the proper order

142

and1->evl();

xor1->evl();

144

145

// Take calculated local wire values and assign the values

146

// to the outside wires via pointers of FA

147

*o1 = coL; *o2 = sumL;

148

149

// ----- Vector Logics ----- //

```

#### Inheritance in Logic Structures

```

inheritedLogicClassesFunctions.cpp + ×

inheritedLogicClassesPrimitives.cpp

inheritedLogicClassesPrimitives.h

Logic Class Inheritance

(Global Scope)

∃int main ()

wire aW('0', 3), bW('1', 5), ciW('X', 0), coWF('X', 0), sumWF('X', 0),

coWH('X', 0), sumWH('X', 0);

wire dW('X', 4), eW('X', 4);

fullAdder *FA = new fullAdder(aW, bW, ciW, coWF, sumWF);

10

halfAdder *HA = new halfAdder(aW, bW, coWH, sumWH);

11

//not *NOT = new not(aW, dW, 5); // or use gates as below

12

gates *NOT = new not(aW, dW, 5); // "not" can do everything that "gates" can.

13

int ai:

15

inheritedLogicClassFunctions.cpp

16

inpBit("Wire a", aW);

18

inpBit("Wire b", bW);

19

inpBit("Wire c", ciW);

20

21

FA->evl();

HA->evl();

NOT->evl();

24

outBit("FA - Carry", coWF);

outBit("

Sum", sumWF);

27

outBit("HA - Carry", coWH);

outBit("

Sum", sumWH);

30

outBit("NOT - Gate", dW);

33

cout << "\n" << "Continue? "; cin >> ai;

34

35

} while (ai>0);

36

⊡/*int main ()

Zainalabedin Navabi - Logic Simulation with

```

- Containing Event Based Timing

- To include in wires

- To include in gates

- Gate-based structures

- Gate pointers and objects

- Wire and gate vectors

- Inheritance in LogicStructures

- A generic gate definition

- Gates to include timing

- Building structures from objects

- Hierarchal Modeling of Digital Components

- Wire functionalities

- Gate functionalities

- · Polymorphic gate base

- Virtual functions

- Functions overwriting

- Flip flop description hierarchal

$$W_{0con} = a_{0con} * b_{0con}$$

$$W_{1con} = a_{1con} + b_{1con} - a_{1con} * b_{1con}$$

$$w_{1con} = 1 - a_{1con}$$

### Polymorphic Gate Base

```

polymorphismLogicClassesPrimitives.h* +

polymorphismLogicClassesFunctions.h

Logic Class Polymorphism

(Global Scope)

□class gates {

protected:

25

wire *i1, *i2, *o1;

26

int gateDelay, lastEvent;

27

char lastValue:

28

void timingActivity2();

PolymorphismLogicClassesPrimitives.h

30

void timingActivity1();

31

static int numberOfGates;

32

public:

33

int gateIdentifier;

Gates constructor

34

float outputControlability = 1.0;

assigns an id and

35

gates(wire& a, wire& w, int d) :

36

i1(&a), o1(&w), gateDelay(d) {

increments the gate

gateIdentifier = numberOfGates;

38

numberOfGates++:

count

39

40

gates(wire& a, wire& b, wire& w, int d) :

41

i1(&a), i2(&b), o1(&w), gateDelay(d) {

gateIdentifier = numberOfGates;

numberOfGates++;

44

45

gates(){};

46

~gates(){}:

47

virtual void evl();

48

virtual void prob(){};

49

Virtual can be overwritten by

50

51

float getProb(gates*);

classes that inherit from it. If not

52

☐ class and: public gates {

overwritten, the same evl() of

54

public:

and(wire& a, wire& b, wire& w, int d) : gates(a, b, w, d) {}

55

gates will be used for an

~and();

void evl();

57

inherited class

void prob();

```

#### Polymorphic Gate Base polymorphismLogicClassesPrimitives.h 垣 🗶 polymorphismLogic...ssesPrimitives.cpp Logic Class Polymorphism (Global Scope) □class and: public gates { and(wire& a, wire& b, wire& w, int d) : gates(a, b, w, d) 55 56 ~and(); 57 void evl(); void prob(); 59 PolymorphismLogicClassesPrimitives.h □ class or: public gates { public: or(wire& a, wire& b, wire& w, int d) : gates(a, b, w, d) {} 63 void evl(); 66 void prob(); Each gate just uses the **|** }; 68 constructor of gates and □class not: public gates { declares member not(wire& a, wire& w, int d) : gates(a, w, d) {} functions to overwrite evl() ~not(); void evl(); and prob() of gates void prob(); }; □class xor: public gates { public: xor(wire& a, wire& b, wire& w, int d) : gates(a, b, w, d) {} 80 ~xor(); 81 void evl(); 82 void prob(); 83 84 □class flipflop { protected: 87 wire \*D, \*clk, \*rst, \*cen, \*Q; int clkODelav: int rstQDelay; © 2014-2015, Zainalabedin Navabi - Logic Simulation with C/C++

### Polymorphic Gate Base

103

```

polymorphismLogicClassesPrimitives.h* +

polymorphismLogic...ssesPrimitives.cpp

Logic Class Polymorphism

(Global Scope)

□class flipflop {

protected:

87

wire *D, *clk, *rst, *cen, *Q;

int clkQDelay;

89

int rstQDelay;

int lastEvent; // last time output changed

91

char lastValue;

bool containsReset = false;

93

float clockControlability = 0.5;

94

static int numberOfFlipflops:

95

public:

PolymorphismLogicClassesPrimitives.h

96

int flipflopIdentifier;

97

float outputControlability = 1.0;

98

flipflop(wire& d, wire& c, wire& q, int dC):

99

D(\&d), clk(\&c), Q(\&q), clkQDelay(dC) {

100

flipflopIdentifier = numberOfFlipflops;

numberOfFlipflops++:

101

102

Pure virtual functions

103

~flipflop(){};

104

virtual void evl() = 0;

105

virtual void prob() = 0;

106

virtual void init(float, char) = 0;

107

108

class DFF : public flipflop {

109

110

First Level Derived

111

DFF(wire& d, wire& c, wire& q, int dC) : flipflop(d, c, q, dC)

112

{ containsReset = false; };

flip-flop classes

113

~DFF(){};

114

virtual void evl();

115

virtual void prob();

116

virtual void init(float, char);

117

118

□class DFFsR : public DFF {

119

120

public:

l.5, Zainalabedin Navabi - Logic Simulation with

```

## Flip Flop Description Hierarchies polymorphismLogicClassesPrimitives.h\* polymorphismLogic...ssesPrimitives.cpp \* ×

```

Logic Class Polymorphism

(Global Scope)

int flipflop::numberOfFlipflops = 1;

126

PolymorphismLogicClassesPrimitives.cpp

127

∃void DFF::evl() {

128

char valueToLoad = '0':

129

130

if (!containsReset) valueToLoad = D->value;

131

else valueToLoad = (rst->value == '1') ? '0' : D->value;

132

133

if (clk->value == 'P') {

134

0->value = valueToLoad;

135

Q->eventTime = calculateEventTime(lastValue, Q->value,

Basic DFF with

136

clk->eventTime, clkQDelay, lastEvent);

137

synchronous reset

138

139

Q->eventTime = calculateEventTime(lastValue, Q->value,

140

clk->eventTime, clkQDelay, lastEvent);

141

142

Q->activityCount = (D->activityCount + clk->activityCount) * 2 +

143

((lastValue == Q->value) ? 0 : 3);

144

145

lastEvent = 0->eventTime:

146

lastValue = Q->value;

147

148

□void DFF::prob(){

149

outputControlability = D->controlability * clockControlability;

150

Q->controlability = outputControlability;

151

152

□void DFF::init(float clkCon, char iniOut) {

clockControlability = clkCon; Q->value = iniOut;

153

154

155

156

□void DFFsR::prob(){

DFFsR is inherited

157

outputControlability = (D->controlability + rst->controlability -

158

D->controlability * rst->controlability ) *

from DFF

159

clockControlability;

160

Q->controlability = outputControlability;

```

```

Flip Flop Description Hierarchies

polymorphismLogic...ssesPrimitives.cpp

polymorphismLogicClassesPrimitives.h +

Inherited from DFF.

c Class Polymorphism

(Global Scope)

Second Level

class DFFsR : public DFF {

Same members but

Derivation

DFFsR(wire& d, wire& c, wire& r, wire& q, int dC, int dR) : DFF(d, c, q, dC) +

assigns value to

containsReset = true:

existing rst of flip

rst = &r;

No evl(), so

rstQDelay = dR;

flop

uses the one of

~DFFsR(){};

virtual void prob();

DFF

PolymorphismLogicClassesPrimitives.h

class DFFsRE : public DFFsR {

public:

Third Level

DFFsRE(wire& d, wire& c, wire& r, wire& e,

derivation

wire& q, int dC, int dR) : DFFsR(d, c, r, q, dC, dR) {

cen = &e;

137

~DFFsRE(){};

138

virtual void evl();

139

140

141

142

// Structures based on above primitives begin here

143

144

□ class fullAdder {

wire *i1, *i2, *i3, *o1, *o2;

145

146

147

// Declare necessary gate instances

148

gates *xor1;

149

gates *xor2;

150

gates *and1;

151

gates *and2;

152

gates *or1;

153

154

155

156

// fulladder Local wires

100 % -

© 2014-2015, Zainalabedin Navabi - Logic Simulation with C/C++

105

```

#### Flip Flop Description Hierarchal

```

polymorphismLogicClassesPrimitives.h*

polymorphismLogic...ssesPrimitives.cpp +

🛂 Logic Class Polymorphism

(Global Scope)

□void DFFsR::prob(){

156

157

outputControlability = (D->controlability + rst->controlability -

158

D->controlability * rst->controlability ) *

159

clockControlability;

160

Q->controlability = outputControlability;

161

162

163

□void DFFsRE::evl() {

if (en->value == '1') DFFsR::evl();

164

165

166

PolymorphismLogicClassesPrimitives.cpp

// Structures based on above primitives begin

167

168

□void fullAdder::prob(){

169

170

171

// Calculate probabilities in the proper order

DFFsRE calls

172

xor1->prob();

173

and1->prob();

DFFsR when

174

and2->prob();

value is one

175

or1->prob();

176

xor2->prob();

177

178

o1Controlability = getProb(or1);

179

o2Controlability = getProb(xor2);

180

181

□void fullAdder::evl () {

182

183

// Via the FA pointers, read wire values that connect to

184

// the FA from outside, and assign them to FA Local wires

185

aL = *i1; bL = *i2; ciL = *i3;

186

187

// Evaluate gates in the proper order

188

xor1->evl();

189

and1->evl();

190

and2->evl();

191

or1->evl();

```

106

#### Flip Flop Description Hierarchal

```

polymorphismLogicClassesUtilities.cpp +>

polymorphismLogic...ssesPrimitives.cpp

Logic Class Polymorphism

(Global Scope)

□void inpBit(string wireName, wire& valtim) {

char value;

int time:

cout << "Enter value followed by @ time for " << wireName << ": ":

cin >> value; cin >> time;

valtim.put(value, time);

Pvoid inpBit(string wireName, wire& valtim, int t: PolymorphismLogicClassesPrimitives.cpp

13

cout << "For @ time " << time << ", enter logic value for " << wireName << ": ";

cin >> value:

valtim.put(value, time);

17

18

□void outBit(string wireName, wire valtim) {

19

char value:

20

int time:

21

valtim.get(value, time);

cout << wireName << ": " << value << " @ " << time << "\n";

22

23

□void inpBit(string wireName, wireV& valtim) {

25

26

string value;

cout << "Enter value followed by @ time for " << wireName << ": ";

cin >> value; cin >> time;

30

valtim.put(value, time);

31

□void outBit(string wireName, wireV valtim) {

34

string value:

int time;

valtim.get(value, time);

cout << wireName << ": " << value << "@ " << time << "\n";

37

15. Zainalabedin Navabi - Logic Simulation with

```

#### Flip Flop Description Hierarchal

```

polymorphismLogicClassesUtilities.cpp

polymorphismLogic...ssesFunctions.cpp 垣

Logic Class Polymorphism

(Global Scope)

3 ⊡int main()

wire a('0', 3), b('1', 5), c('X', 0), clk('X', 0), rst('X', 0),

en('X', 0),

Q1('X', 0), Q2('X', 0), Q3('X', 0);

wire v('0', 3), w('0', 3), y('1', 5);

10

flipflop *FF1 = new DFF(a, clk, Q1, 401);

11

flipflop *FF2 = new DFFsR(a, clk, rst, Q2, 502, 6);

12

flipflop *FF3 = new DFFsRE(a, clk, rst, en, Q3, 603, 7);

13

FF1->init(float(0.37), '1');

14

FF2->init(float(0.37), '1');

FF3->init(float(0.37), '1')

PolymorphismLogicClassesFunctions.cpp

15

16

17

gates *NOT = new not(y, w, 5);

18

gates *AND = new and(a, b, v, 7);

19

gates *OR1 = new or(v, c, y, 6);

20

21

AND->prob();

Pointer

OR1->prob();

compatibility

NOT->prob();

24

FF1->prob();

FF2->prob();

FF3->prob();

27

28

cout << "AND gate Id: " << AND->gateIdentifier << '\n';

cout << "OR1 gate Id: " << OR1->gateIdentifier << '\n';

30

cout << "NOT gate Id: " << NOT->gateIdentifier << "\n\n";

31

cout << "DFF2 output 1-probability: " << FF2->outputControlability << '\n';</pre>

33

cout << "DFF3 output 1-probability: " << FF3->outputControlability << "\n\n";</pre>

34

cout << "AOI output 1-probability: " << getProb(NOT) << '\n';

36

cout << "DFF1 output 1-probability: " << FF1->outputControlability << '\n';</pre>

37

cout << "DFF2 output 1-probability: " << FF2->outputControlability << '\n';</pre>

cout << "DFF3 output 1-probability: " << FF3->outputControlability << "\n\n";</pre>

. Zainalabedin Navabi - Logic Simulation wit

```

108

#### Flip Flop Description Hierarchal polymorphismLogic...ssesFunctions.cpp + polymorphismLogicClassesUtilities.cpp 🛂 Logic Class Polymorphism (Global Scope) int ai: int time = 0: 40 do { inpBit("Wire a", a, time); 43 inpBit("Wire b", b, time); inpBit("Wire c", c, time); 46 inpBit("Clock input", clk, time); inpBit("Reset input", rst, time); inpBit("Enable input", en, time); 49 AND->evl(): 51 OR1->evl(); 52 PolymorphismLogicClassesFunctions.cpp NOT->evl(); FF1->evl(); 54 FF2->evl(); 55 FF3->evl(); 56 57 outBit("AOI output: ", w); 58 outBit("DFF1 output: ", Q1); outBit("DFF2 output: ", Q2); 60 outBit("DFF3 output: ", Q3); 61 cout << "AOI output activity count: " << w.activity() << '\n';</pre> 63 cout << "DFF1 output activity count: " << Q1.activity() << '\n';</pre> 64 cout << "DFF2 output activity count: " << Q2.activity() << '\n';</pre> cout << "DFF3 output activity count: " << Q3.activity() << "\n\n";</pre> 66 67 time += 17; cout << "\n" << "Continue? "; cin >> ai; cout << "\n";</pre> 68 69 70 } while (ai>0); 72 int main() wire aW('0', 3), bW('1', 5), ciW('X', 0), coWF('X', 0), sumWF('X', 0), 109 -2015, Zainalabedin Navabi - Logic Simulation with

#### This chapter presented:

- Procedural Languages for Hardware Modeling

- Types and Operators for Logic Modeling

- Basic Logic Simulation

- Enhanced logic simulation with timing

More Functions for Wires and Gates

- Inheritance in Logic StructuresHierarchal Modeling of Digital Components

#### Copyright and Acknowledgment

© 2015, Zainalabedin Navabi, System-Level Design and Modeling: ESL Using C/C++, SystemC and TLM-2.0, ISBN-13: 978-1441986740, ISBN-10: 144198674X

Slides prepared by Hanieh Hashemi, ECE graduate student